模拟CMOS集成电路设计入门学习(11)

MOS为负载的差动对

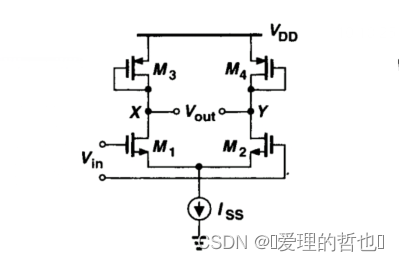

下图是以二级管连接的MOS为负载的差动对:

用器件尺寸表示和

,则有:

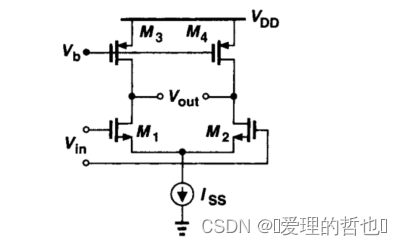

下图是电流源负载的差动对:

回顾:

对于给定的偏置电流和输入器件的尺寸,电路的增益与PMOS管的过驱动电压成比例变化。为了得到更大的电路增益,必须减小(W/L),从而增大,降低X点和Y点的共模电平。

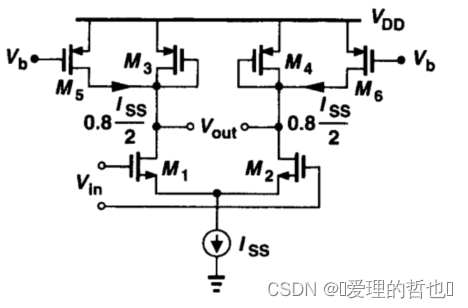

为了缓解上述问题,输入晶体管偏置电流的一部分可以由PMOS管来提供。

如下图所示:

其目的是通过减小其电流而不是减小其宽长比来降低负载器件的。

以电流源为负载的差动对的小信号增益相对较小,该增益在亚微米级技术中一般在10到20之间。

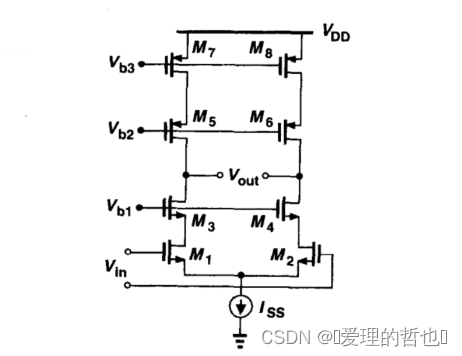

我们可以采用共源共栅来增大PMOS和NMOS的输出阻抗,形成共源共栅级的差动形式:

所以,增益为:

可见共源共栅极大地增大了电路的差动增益,但其代价却是消耗更多的电压余度。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!