FPGA开发——VHDL实现各类触发器

前言

小编最近在学习时序电路的VHDL设计,通过此文对触发器和VHDL相关知识进行总结,以便日后进行复习、查阅。本文首先回顾了各类触发器的基本知识包括特性方程、状态图等,最后通过VHDL来实现各类触发器。

一、触发器知识回顾

在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态。把这种在时钟信号触发时才能动作的存储单元电路称为触发器,常见的触发器有D触发器、RS触发器、JK触发器、T触发器,它们是构成时序逻辑电路的基本单元。

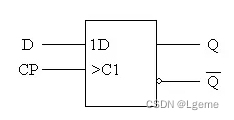

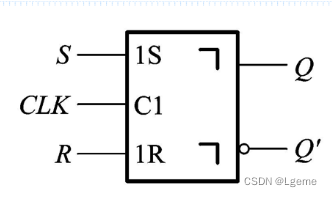

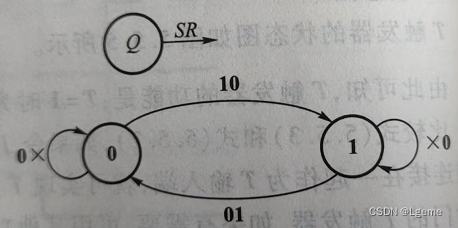

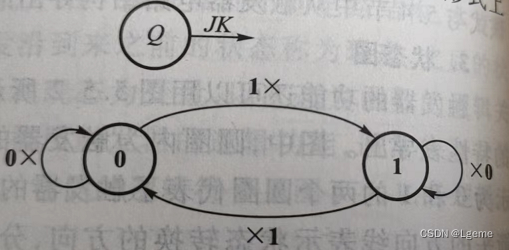

| 名称 | 特性方程 | 逻辑符号 | 状态图 |

| D触发器 |  |  | |

| RS触发器(或非门实现) |

|  |  |

| JK触发器 |  |  | |

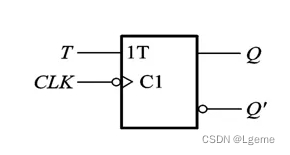

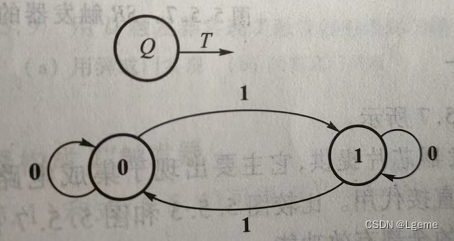

| T触发器 |  |  |

D触发器真值表:

| D | ||

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

RS触发器真值表:

| S | R | ||

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 不确定 |

| 1 | 1 | 1 | 不确定 |

RS触发器真值表:

| J | K | ||

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

T触发器真值表:

| Y | ||

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

二、VHDL实现

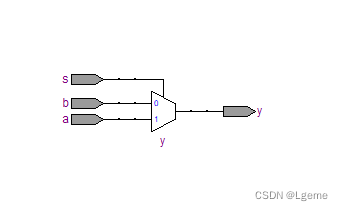

在VHDL中完整的条件语句只能构成组合逻辑电路,例如下面的二选一数据选择器。

entity select1of2 is port (a, b, s : in bit;y : out bit);

end entity select1of2;architecture bhv of select1of2 is beginprocess(a,b,s)beginif(s='1') then y<=a; else y<=b;end if;end process;

end architecture bhv;可以观察到二选一数据选择器的RTL电路没有触发器或者锁存器,即没有存储功能。

在VHDL实现时序电路的核心思想就是通过不完整条件语句。为了实现记忆、存储功能,对于不满足条件的的语句,VHDL综合器解释为不予执行,即信号保持前一次的值,不发生改变。对于数字电路来说,当输入改变后仍能保持原值不变,就意味着使用了具有存储功能的元件,其中输出不仅仅取决于输入,还取决于所处的状态。

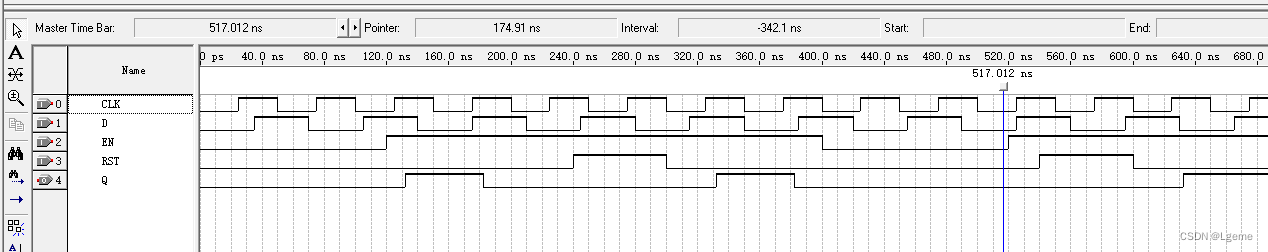

D触发器代码实现

library ieee;

use ieee.std_logic_1164.all;

entity dff2 isport(CLK, RST, EN, D : in std_logic;Q : out std_logic);

end entity dff2;

architecture bhv of dff2 issignal Q1 : std_logic;beginprocess(CLK, Q1, RST, EN)beginif RST = '1' then Q1 <= '0';elsif CLK'EVENT and CLK = '1' then if EN = '1' then Q1 <= D;end if;end if;end process;Q <= Q1;

end architecture bhv;

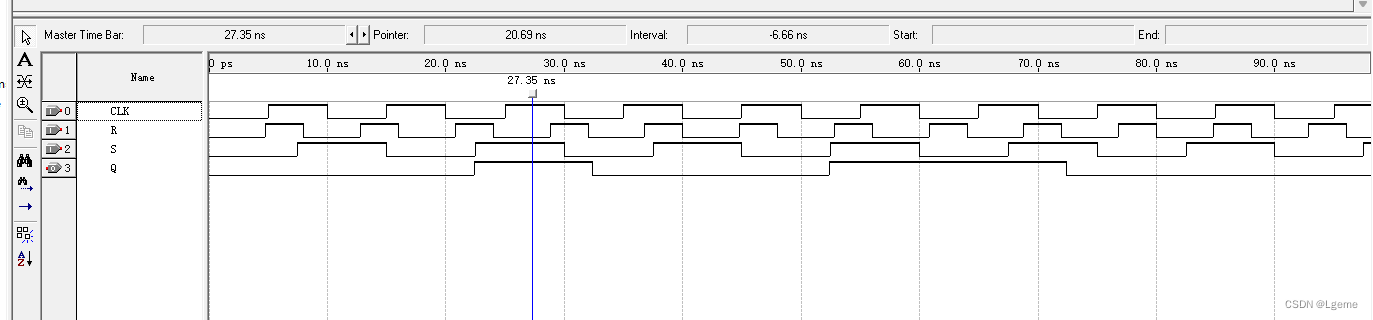

D触发器仿真波形

RS触发器代码实现

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;entity SR isport(S, R, CLK : in std_logic;Q : buffer std_logic);

end entity SR;architecture bhv of SR issignal Q_TEMP : std_logic;beginprocess(CLK)beginif CLK'EVENT and CLK = '1' then --或非门构成的SR触发器if S = '0' and R = '1' thenQ_TEMP <= '0';elsif S = '1' and R = '0' then Q_TEMP <= '1';end if;end if;Q <= Q_TEMP;end process;

end architecture bhv;RS触发器仿真波形

JK触发器代码实现

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity JK isport(CLK,J, K : in std_logic;Q, NQ : out std_logic);

end entity JK;architecture bhv of JK issignal Q_TEMP : std_logic;signal NQ_TEMP: std_logic;beginprocess(CLK, J, K)beginif CLK'EVENT and CLK = '1' thenif (J = '0') and (K = '1') thenQ_TEMP <= '0';NQ_TEMP <= '1';elsif (J = '1') and (K ='0') thenQ_TEMP <= '1';NQ_TEMP <= '0';elsif (J = '1') and (K = '1') thenQ_TEMP <= not Q_TEMP;NQ_TEMP <= not NQ_TEMP;end if;end if;Q <= Q_TEMP;NQ <= NQ_TEMP;end process;

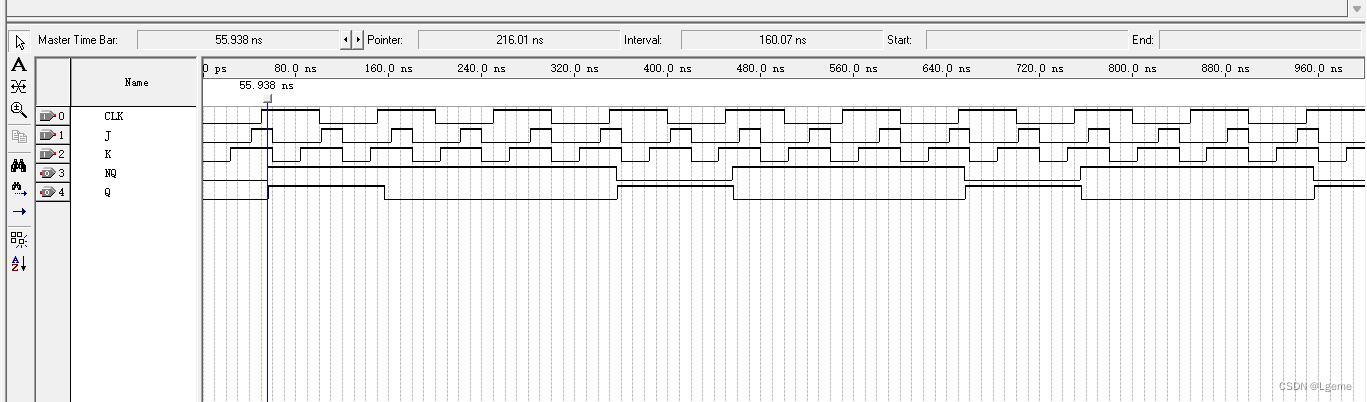

end architecture bhv;JK触发器仿真波形

T触发器代码实现

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;entity t_ff isport(CLK, T : in std_logic;Q: buffer std_logic);

end entity t_ff;architecture bhv of t_ff issignal Q_TEMP : std_logic;beginprocess(CLK)beginif CLK'EVENT and CLK = '1' thenif T = '1' then Q_TEMP <= not Q_TEMP;elseQ_TEMP <= Q_TEMP;end if;end if;Q <= Q_TEMP;end process;

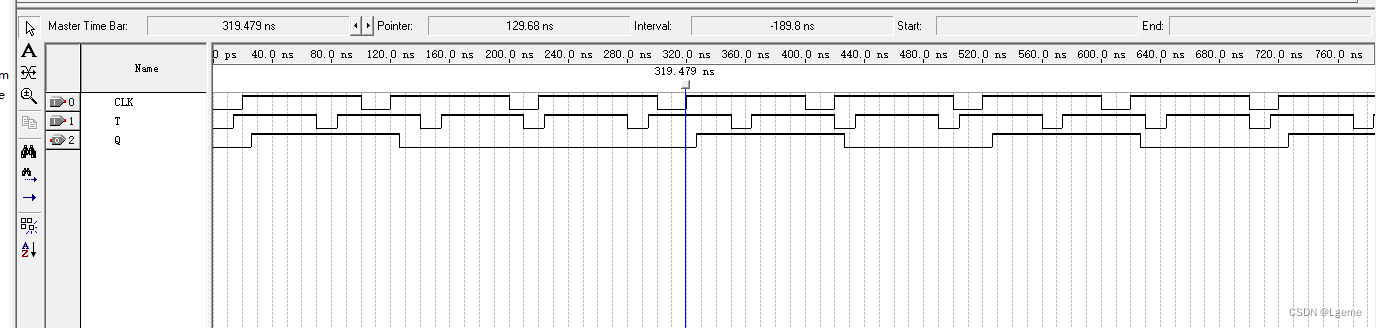

end architecture bhv;T触发器仿真波形

总结

以上就是本文的全部内容,非常感谢你能看到这里(仿真波形有一定的延迟)。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!