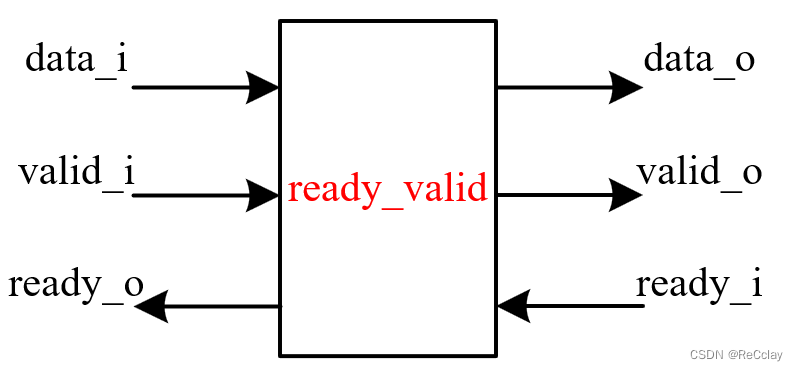

【校招Verilog手撕代码】VL8、握手过程(ready-valid)

文章目录

- 理论

- 代码

理论

握手过程主要用于上下游模块之间的交互。

握手信号,就是为了模块之间的数据交互正确才衍生出来的信号。其无非就是三种可能

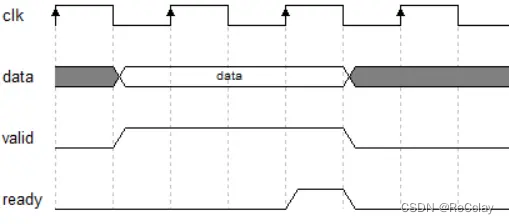

1、上游master提供的valid 信号随数据一起拉高,但下游slave过一段时间才准备好的valid先高为敬。

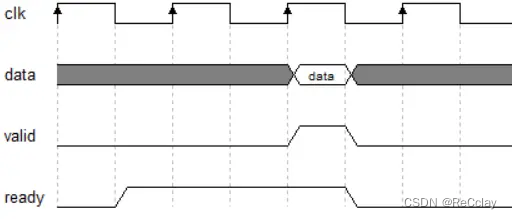

2、下游slave一直准备好,但上游数据过段时间才有效的ready先高为敬。

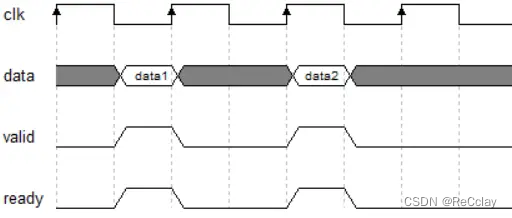

3、上游master的valid信号和下游slave的ready同时为高。

代码

RTL

module ready_valid(本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!