同步置位与异步置位

同步置位:当置位信号有效且时钟上升沿到来时,才会执行置位。

异步置位:只要置位信号有效,就会执行置位,不考虑时钟信号是否有效。

程序:

//功能:使用触发器实现同步置位和异步置位

module dff_sync_set (input wire clk,//50mhz时钟input wire rst_n,//复位,下降沿有效input wire din,//输入信号input wire set,//置位信号,高电平有效output reg out1,//输出信号,同步置位output reg out2 //输出信号,异步置位

);

//同步置位

always @(posedge clk or negedge rst_n ) beginif (!rst_n) beginout1 <= 1'b0;end else if(set)beginout1 <= 1'b1;endelse beginout1 <= din;endend

//异步置位

always @(posedge clk or negedge rst_n or posedge set) beginif(!rst_n)beginout2 <= 1'b0;endelse if(set)beginout2 <= 1'b1;endelse beginout2 <= din;end

endendmodule测试代码:

`timescale 1ns/1nsmodule tb_dff_sync_set ();reg clk;reg rst_n;reg din;reg set;wire out1;wire out2;initial beginclk = 1'b0;rst_n=1'b0;#10;rst_n=1'b1;

end

always #10 clk=~clk;

initial begindin=1'b0;set=1'b0;#20;din=1'b1;set=1'b0;#20;din=1'b0;set=1'b0;#20din=1'b0;set=1'b1;#20din=1'b1;set=1'b0;#40;$stop;

enddff_sync_set dff_sync_set_inst (/*input wire*/ .clk (clk ),//50mhz时钟/*input wire*/ .rst_n(rst_n),//复位,下降沿有效/*input wire*/ .din (din ),//输入信号/*input wire*/ .set (set ),//置位信号,高电平有效/*output reg*/ .out1 (out1),//输出信号,同步置位/*output reg*/ .out2 (out2)//输出信号,异步置位

);

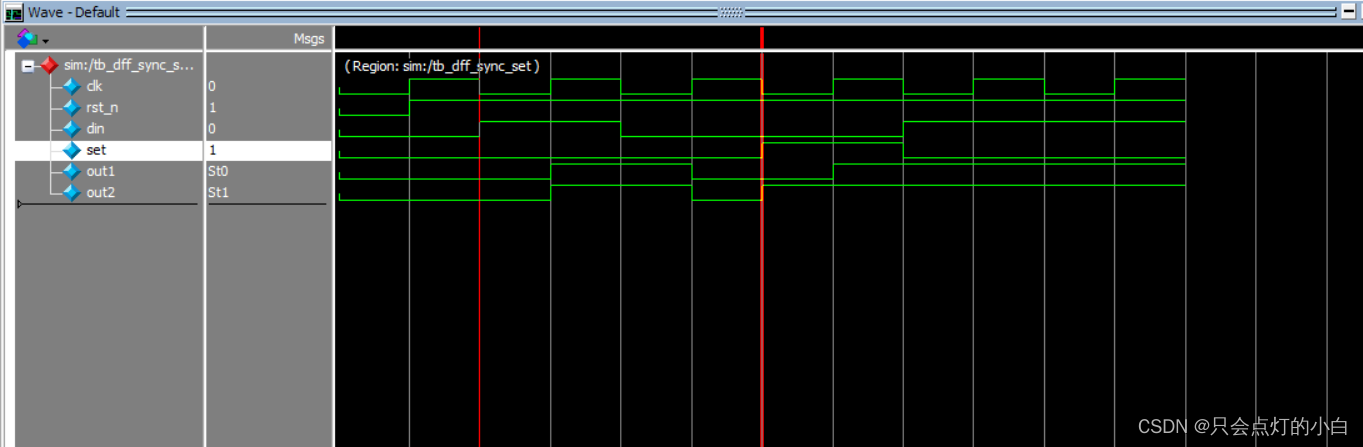

endmodule仿真图:

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!