基于vivado的同步和异步置位触发器

目录

基本要求

设计思路

同步置位复位代码

testbench代码

behavioral波形图编辑

合成电路结构图

post-synthesis timing simulation:

Implementation:

post-implementation-timing simulation

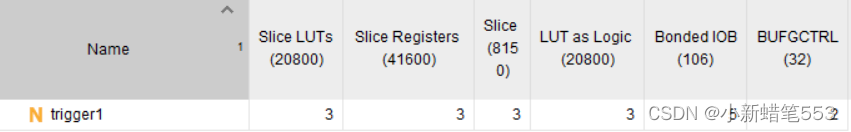

资源利用率:

异步置位复位

Verilog代码

Testbench代码

仿真电路图

3.3 behavioral

3.4 post-synthesis timing simulation

3.5 post-implementation-timing simulation

布局布线图

3.7资源利用率:

Xilinx FPGA芯片的时序逻辑资源(D触发器)的种类进行归纳总结:

基本要求

- 分析同步和异步复位触发器的工作原理,画出电路结构示意图;

- 创建New Project,并编写Verilog module代码实现1位同步复位触发器和1位异步触发器,检查语法错误;

- 编写testbench.v 文件进行仿真,并得出behavioral仿真波形图,验证所实现电路的正确性;

- 对Verilog module电路进行综合(synthesis),整理出电路结构图,并查看综合报告,分析波形图,得出延迟信息等;

- 对Verilog module电路进行布局布线(implementation),整理出布局布线图,并进行post-implementation-timing simulation,分析波形图,得出延迟信息,分析原因;

设计思路

同步和异步复位电路在Verilog代码中的设计区别在于,同步复位仅仅在时钟信号clk上升沿有效,即clk上升沿信号来时set和reset信号才有效。异步复位则是不论始终信号何时到来只要set和reset信号改变都会引起q值的变化。故在Verilog代码设计同步和异步复位电路是只需要改变当set和reset信号改变时也引起输出值的改变即可将同步改为异步触发器。

同步置位复位代码

module trigger(data,clk,reset,set,q);

input data,clk,reset,set;

output reg q;always @(posedge clk )

begin

if(!reset)q<=1'b0;

else if(!set)q<=1'b1;

else q<=data;endendmoduletestbench代码

module trigger_tb();

reg data, set,reset, clk;

wire q;

trigger t(.data(data),.set(set),. clk(clk),.reset(reset),.q(q));

initial

begin

data=1;set=1;reset=1;clk=0;

end

always #10 clk=~clk;

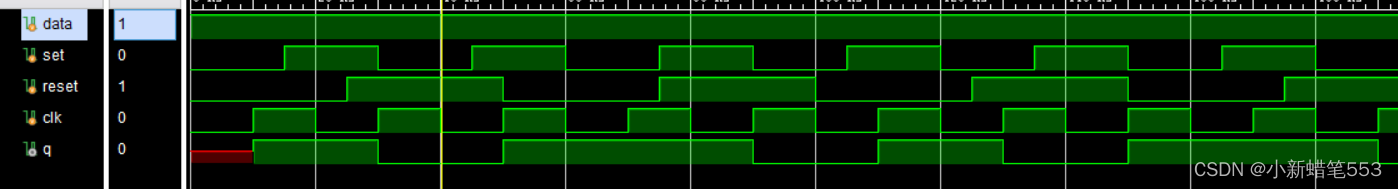

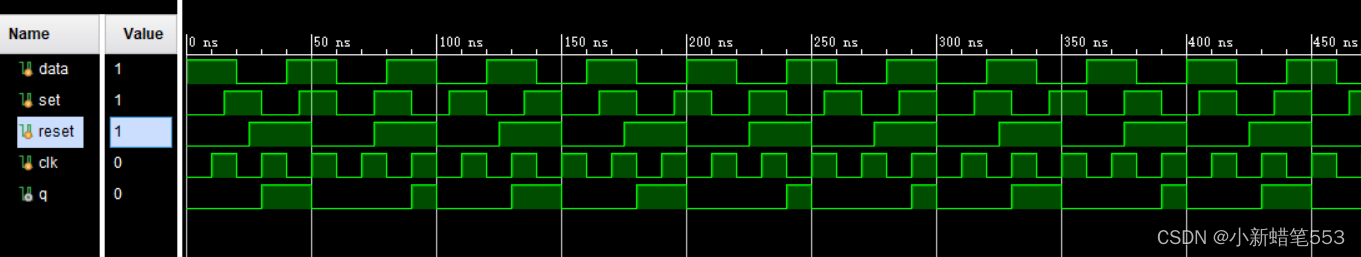

always #20 data=~data;endmodulebehavioral波形图

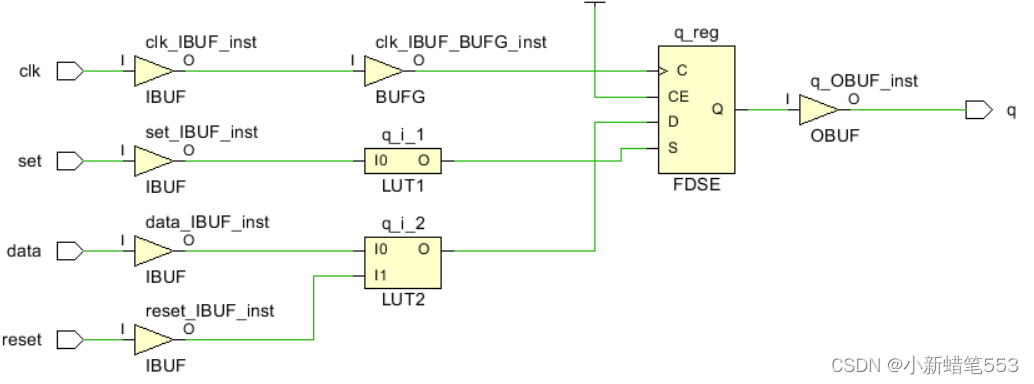

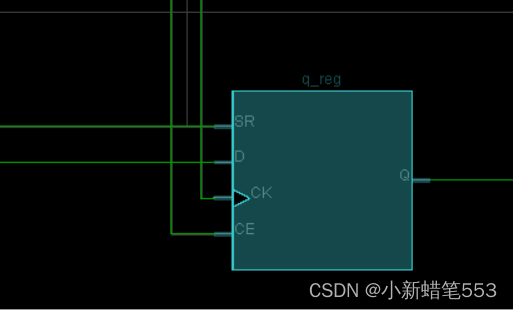

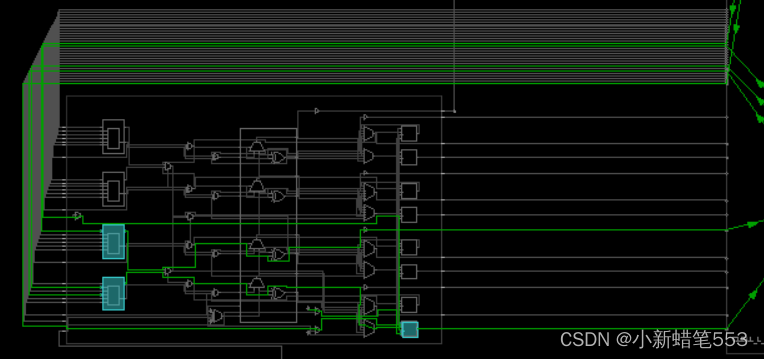

合成电路结构图

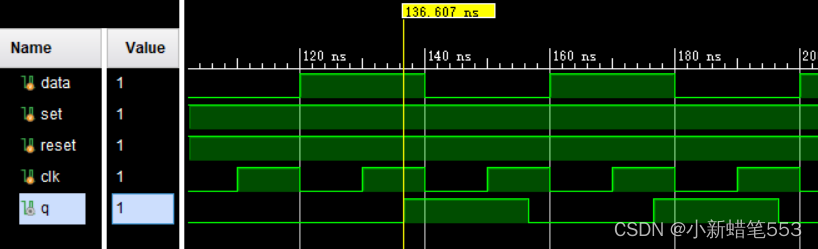

post-synthesis timing simulation:

任意取一个变化的状态观察考虑传输延时的波形图并对比理想状态下的波形图发现,此时波形延迟约为6.2ns,

Implementation:

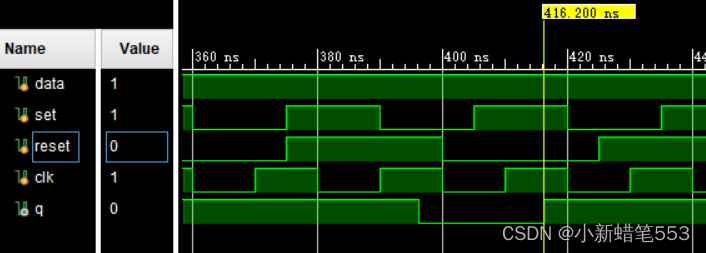

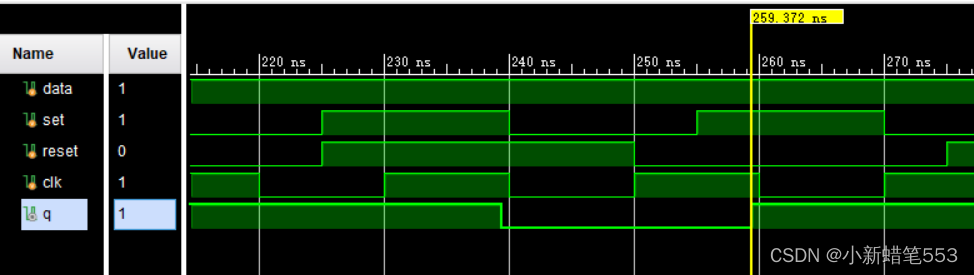

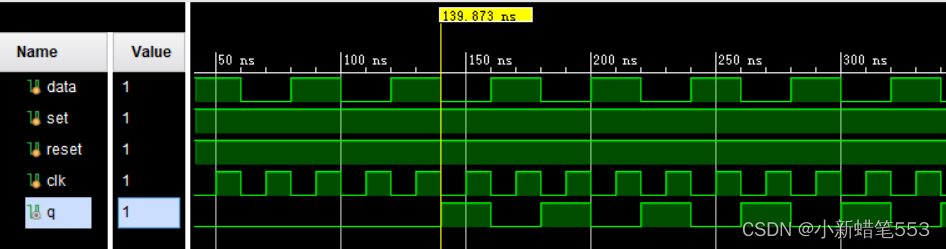

post-implementation-timing simulation

观察后仿真输出波形发现,此时输出延时约为9.372ns ,比综合后的电路传输延时要高,这其中的原因是由于综合后生成的门级网表只是表示了门与门之间虚拟的连接关系,并没有规定每个门的位置以及连线的长度等。所以,布局布线图是更为接近真实情况的仿真,综合仿真是比较理想化的传输延时。

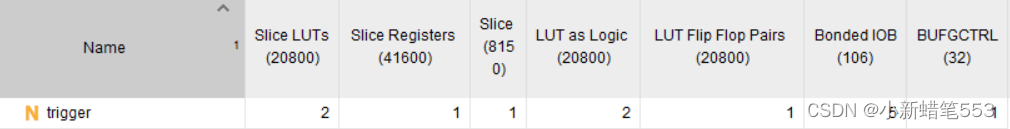

资源利用率:

异步置位复位

Verilog代码

module trigger1(data,clk,reset,set,q);

input data,clk,reset,set;

output reg q;always @(posedge clk or negedge set or negedge reset)

begin

if(!reset)q<=1'b0;

else if(!set)q<=1'b1;

else q<=data;endendmoduleTestbench代码

module trigger1_tb();

reg data, set,reset, clk;

wire q;

trigger1 t(.data(data),.set(set),. clk(clk),.reset(reset),.q(q));

initial

begin

data=1;set=1;reset=1;clk=0;

end

always #10 clk=~clk;

always #20 data=~data;

endmodule仿真电路图

3.3 behavioral

3.4 post-synthesis timing simulation

延时为6.607ns

3.5 post-implementation-timing simulation

延时约为9.873ns

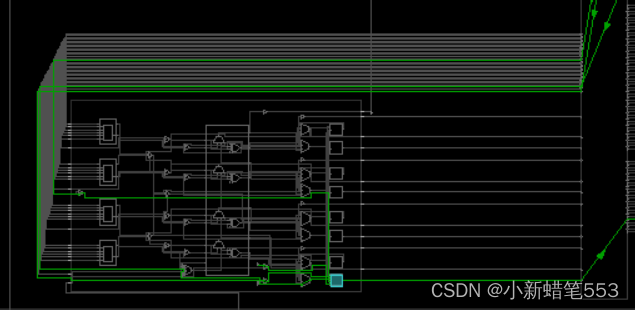

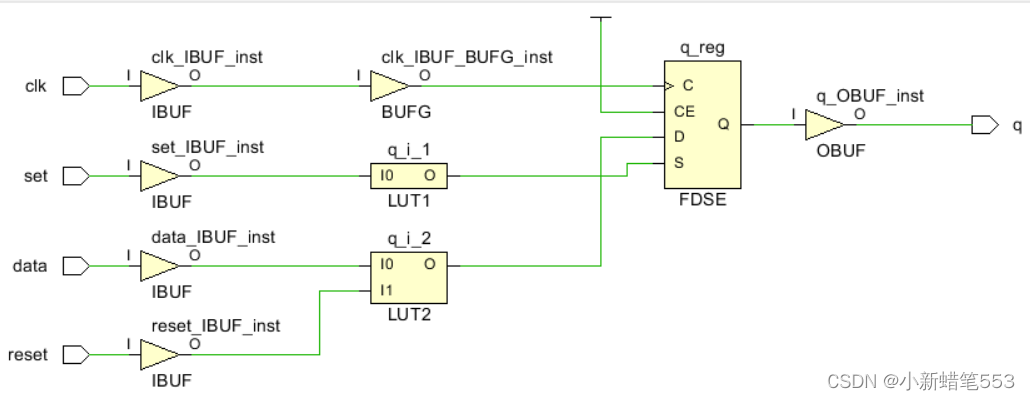

布局布线图

3.7资源利用率:

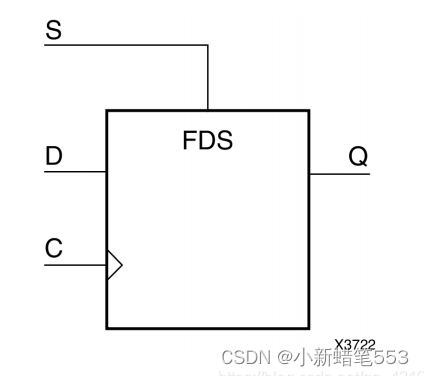

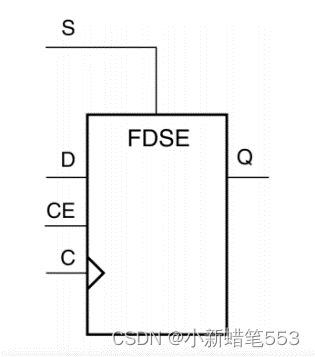

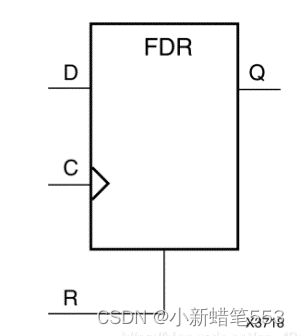

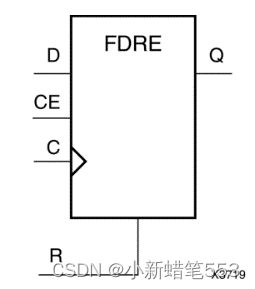

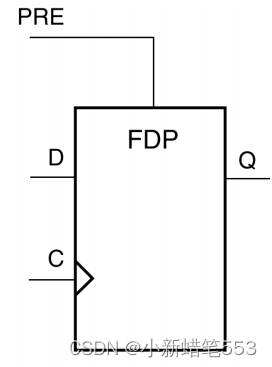

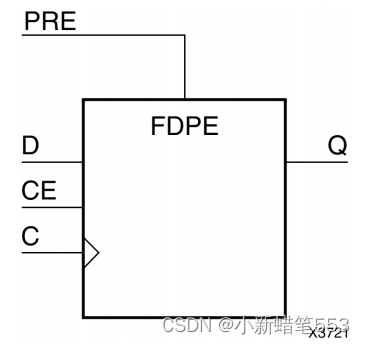

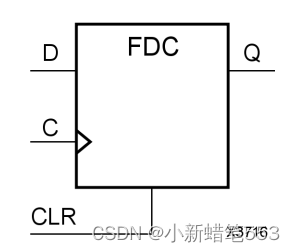

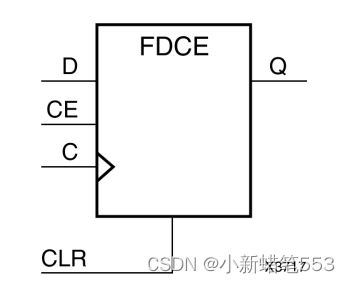

Xilinx FPGA芯片的时序逻辑资源(D触发器)的种类进行归纳总结:

FDS:D Flip-Flop with Synchronous Set 带同步置位的D触发器 当置为端为低电平时,在时钟的上升沿触发数据保存在触发器中,当置位端为低电平时,在一个时钟的上升沿触发导致触发器清0

FDSE:D Flip-Flop with Clock Enable and Synchronous Set 带时钟使能和同步置位的D触发器。当置位端为高电平时覆盖所有输出,一个时钟的上升沿触发导致寄存器置位,当置位端为低电平和时钟使能位为高电平时,在一个时钟的上升沿触发导致寄存器装载数据口的数据

FDR : D Flip-Flop with Synchronous Rsest 同步清除D触发器。FDR 拥有一个时钟输入接口,一个D触发器数据接口,一个同步复位接口和一个触发器输出接口,当同步复位接口为高电平时,时钟的上升沿触发寄存器复位(置0);当同步时钟接口为低电平时,时钟的上升沿触发寄存器装载数据接口的数据。

FDRE:D Flip-Flop with Clock Enable and Synchronous Reset 带使能功能的同步清除D触发器,相比与FDR多了一个使能接口,当同步复位接口为高电平时覆盖所有其他输出,时钟的上升沿触发寄存器复位(置0);当同步时钟接口为低电平且使能接口为高电平时,时钟的上升沿触发寄存器装载数据接口的数据。

FDP:D Flip-Flop with Asynchronous Preset 带有异步预置的D触发器 相比FDS不需要等到时钟的上升沿,即刻可进行置位。

FDPE:D Flip-Flop with Clock Enable and Asynchronous Preset 带有时钟使能和异步置位的D触发器 ,相比于FDSE不需要等到时钟的上升沿,即刻可进行置位。

FDC :D Flip-Flop with Asynchronous Clear 带异步清除D触发器 ,与 FDR的区别是,当CLR置为高电平时,不需要等到下一个时钟的上升沿就可以复位寄存器

FDCE:D Flip-Flop with Clock Enable and Asynchronous Reset 带使能功能的异步清除D触发器,相比与FDRE将同步复位变化成异步复位,当同步复位接口为高电平时,直接触发寄存器复位(置0);当同步时钟接口为低电平且使能接口为高电平时,时钟的上升沿触发寄存器装载数据接口的数据。

若本篇文章对您有帮助可以点赞或打赏支持一下作者

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!