QuartusII中LPM_COUNTER的使用

ALTERA建议,在设计时时序允许的情况下尽量使用Megafunction的资源,因为在多数情况下Megafunction的综合和实现结果更为优化。现在,就LPM_COUNTER的使用,浅谈一下。

Megafunction中LPM_COUNTER的参数设定主要是以下三部分:

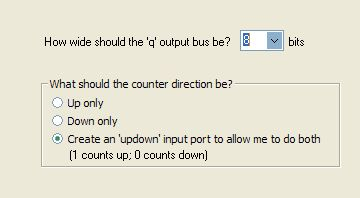

1.计数输出值位数和计数方向的设定:

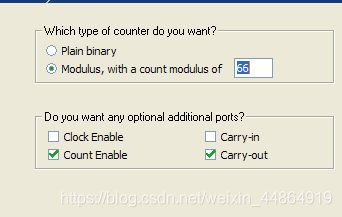

2. 计数系数和使能及进位的设定:

需要注意的是:这里的Count Enable计数使能,即其只是计数的使能信号,加载信号并不受它的控制。

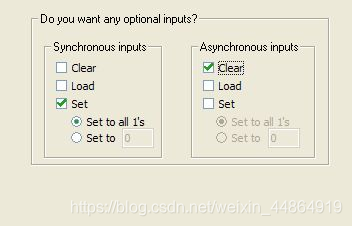

3.所需同步输入和异步输入的设定:

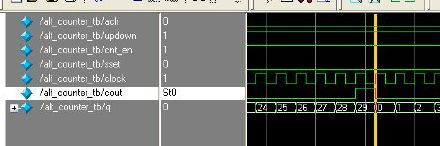

其实,这三个部分的设定很简单,主要是我们如何使用这些设定的问题。平时的数字设计中,我们经常需要对一些脉冲进行计数,而且是要求计到某个值时,产生一个相应的输出,相当于我们通过计数产生一个标志信号,在这种情况下,modulus和carry_out的设定就起了作用了。现在我将modulus设为30,选择向上计数的8位计数器,并选中carry_out,看一下仿真波形如下:

也就是说,这时cout就可以做为一个标志信号,用来决定其他相关操作开始的标志。通过这样简单的设定,无疑节省了我们编写代码的工作时间,尽管这个设计代码量很小。

好,现在再来看一下次LPM_COUNTER的verilog代码,如下:

`timescale 1 ps / 1 ps// synopsys translate_onmodule alt_counter (aclr,clock,cnt_en,sset,updown,cout,q);input aclr;input clock;input cnt_en;input sset;input updown;output cout;output [7:0] q;wire sub_wire0;wire [7:0] sub_wire1;wire cout = sub_wire0;wire [7:0] q = sub_wire1[7:0];parameter n=30; //%%%%%%%%%%%//lpm_counter lpm_counter_component (.aclr (aclr),.clock (clock),.updown (updown),.sset (sset),.cnt_en (cnt_en),.cout (sub_wire0),.q (sub_wire1),.aload (1'b0),.aset (1'b0),.cin (1'b1),.clk_en (1'b1),.data ({8{1'b0}}),.eq (),.sclr (1'b0),.sload (1'b0));defparamlpm_counter_component.lpm_direction = "UNUSED",lpm_counter_component.lpm_modulus = n, //lpm_counter_component.lpm_port_updown = "PORT_USED",lpm_counter_component.lpm_type = "LPM_COUNTER",lpm_counter_component.lpm_width = 8;endmodule其中标记为//行中的n是我更改的,原产生程序中为30,此处,我将其改为n后,在上面加上一行声明parameter n=30;(标记为//%%%%%%//的行),便于程序的通用性移植。

此设计消耗8个寄存器,16个组合功能块,共16个LE。当设定的modulus值大于255时,消耗8个寄存器,10个组合功能块,共10个LE。当不使用cout输出也不对modulus设置时,消耗9个组合功能块,共9个LE,这也可为资源的使用提供参考。

此为文档搬运,原文链接

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!