基于FPGA的小波变换的verilog实现和硬件测试,使用quartusii平台

1.问题描述:

基于FPGA的小波变换的verilog实现和硬件测试,使用quartusii平台

2.部分程序:

`timescale 1ns / 10ps

//

// Company:

// Engineer:

//

// Design Name:

// Module Name: coff_delta

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module coff_delta(

i_din,

o_dout

);

input signed[15:0] i_din;

output signed[15:0]o_dout;

//0.4435068522

///2 /3 /4 /5 /9 /11 /12 /13 /14

wire signed[15:0]r0;

//0.4435068522

assign r0 ={i_din[15],i_din[15],i_din[15:2]} +

{i_din[15],i_din[15],i_din[15],i_din[15:3]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:4]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:5]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:9]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:11]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:12]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:13]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:14]};

//0.4435068522

assign o_dout = r0;

endmodule

`timescale 1ns / 10ps

//

// Company:

// Engineer:

//

// Design Name:

// Module Name: coff_alpha

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module coff_beta(

i_din,

o_dout

);

input signed[15:0] i_din;

output signed[15:0]o_dout;

//-0.052978515625

//1/5 1/6 1/8 /9 1/12

wire signed[15:0]r0;

//0.052978515625

assign r0 ={i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:5]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:6]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:8]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:9]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:12]};

//-0.052978515625

assign o_dout = ~r0 + 1'b1;

endmodule

3.仿真结论:

硬件测试图

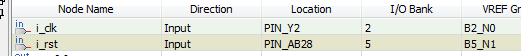

1.先进行管脚绑定

选择pin planner

这个就是管脚绑定。

3.然后对signaltap进行配置

小波shint编码压缩:

小波shint解压缩:

使用modeslsim进行仿真,结果如下

将仿真波形放大,其中小波变换之后如下所示:

编码解码如下所示

最后小波逆变换之后得到如下结果:

A17-9

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!