Cadence Allegro(14):CM约束管理器

Cadence Allegro(14):CM约束管理器

前提摘要

-

个人说明:

限于时间紧迫以及作者水平有限,本文错误、疏漏之处恐不在少数,恳请读者批评指正。意见请留言或者发送邮件至:“noahpanzzz@gmail.com”

-

参考

- PCB入门首选视频-小哥Cadence Allegro 2层板视频

正文

嘉立创 PCB工艺规则

CM约束管理器

-

Eletical:设置差分对和等长规则。

-

Physical:设置走线规则。

-

设置Physical中的Physical Constraint set(设置规则)

- Defualt(信号走线):设置Line Width(线宽规则),8mils,和Vias(过孔属性)via_24d12。

- POWER(电源走线):设置Line Width(线宽规则),20mils,和Vias(过孔属性)via_24d12。

-

设置Physical中的Net(将上面的规则赋予给网络)

创建Netclass,选中网络,右键,Create->Class(比如电源网络,可以批量进行更改)。

-

-

Spacing:设置间距规则。

常规设置版上包括走线,铜皮,过孔,管脚。

-

设置Spacing中的Spacing Constraint set(设置规则)

-

需要设置Line(走线)到其他常用属性对象的间距(Line,Thru Pin(通孔管脚),SMD Pin,Thru Via(通孔),Shape(铜皮),Hole)。

-

批量设置All,全选设置为8mils。

-

-

-

Same Net Spacing :设置相同网络间距。

-

这里由于铜皮是十字花连接,可以在Shape中设置到Thru pin,SMD Pin的间距为8mils(在Cadence Allegro(15):设置全局铜皮参数中关于设置十字花形式连接的线宽,如果选择设置Use thermal width oversize of,则线宽是这两个数值之和)。

-

如果使用全连接,则这里不需要设置。

-

规则检测开关

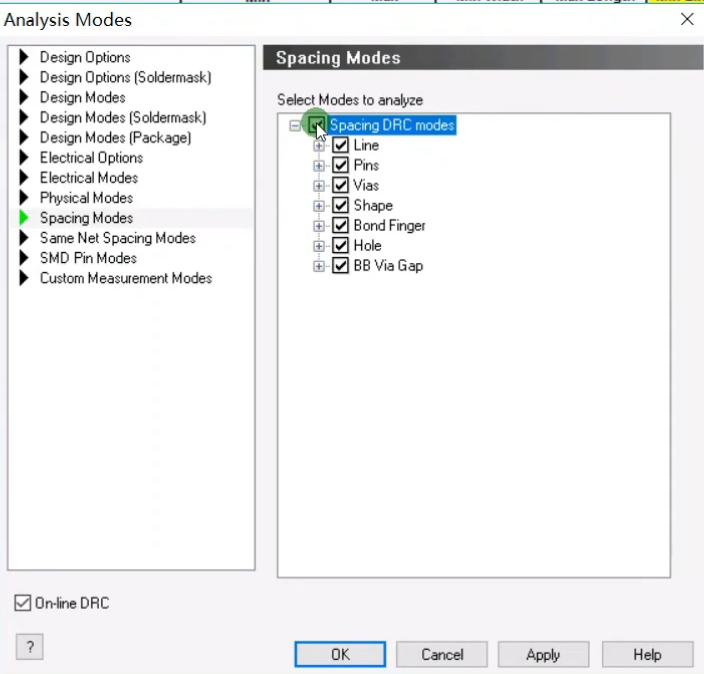

最后需要打开规则开关,否则不会检测规则,在菜单栏点击Analyze->Analyze mode。

-

取消相同网络间距检测选项(Same Net Spacing Modes)。

如果打开的话,fanout的时候,孔离焊盘太近会报错。

-

打开不同网络间距检测选项(Spacing Modes)。

3.打开电气规则设置检测选项(Electrical Modes)。

总结

本文均为原创,欢迎转载,请注明文章出处:https://blog.csdn.net/ZipingPan/article/details/131068378。百度和各类采集站皆不可信,搜索请谨慎鉴别。技术类文章一般都有时效性,本人习惯不定期对自己的博文进行修正和更新,因此请访问出处以查看本文的最新版本。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!