实验二 多路复用器与加法器的实现

实验二 多路复用器与加法器的实现

一、实验目的

1.熟悉多路复用器、加法器的工作原理。

2.学会使用 VHDL 语言设计多路复用器、加法器。

3.掌握 generic 的使用,设计 n-1 多路复用器。

4.兼顾速度与成本,设计行波加法器和先行进位加法器。

二、实验内容

1.用 VHDL 语言设计 8 重 3-1 多路复用器;

2.用 VHDL 语言设计 n-1 多路复用器,调用该 n-1 多路复用器定制为 8-1 多路复用器。

3.用 VHDL 语言设计 4 位行波进位加法器。

4.用 VHDL 语言设计 4 位先行进位加法器。

三、实验方法

- 实验方法:

1采用基于FPGA进行数字逻辑电路设计的方法。

2采用的软件工具是QuartusII软件仿真平台。

- 实验步骤:

- 新建,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径+设置project name)-【next】-【next】(设置Family=FLEX10K;name=EPF10K10TI144-4)-【next】-【finish】

(2).新建:【file】-【new】(选择AHDL File)-【OK】

2、写好源代码,保存文件(文件名与工程名需保持一致)。

3、编译与调试。确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译。编译结果无警告,文件编译成功。

4、波形仿真及验证。【file】-【new】(选择Vector Waveform File)-【OK】。按照程序所述插入节点(插入输入节点和输出节点)。(操作为:左键双击NAME下方框框 -【Node Finder】(设置Filter:Pins:all)-【list】)-【>>】-【ok】-【ok】)。按题目需求设置输入波形,点击保存按钮保存。

5、时序仿真或功能仿真。

(1).时序仿真:

编译VHDL文件-选择.VWF波形文件-【Processing】-【Simulator Tool】(Simulation mode:选择Timing)-点击开始仿真按钮。

(2).功能仿真

编译VHDL文件-选择.VWF波形文件-【Processing】-【Simulator Tool】(Simulation mode:选择Functional)-【Generate Funtional Silmulation Netlist】-点击开始仿真按钮。

6、查看RTL Viewer:【Tools】-【netlist viewer】-【RTL viewer】。

四、实验过程

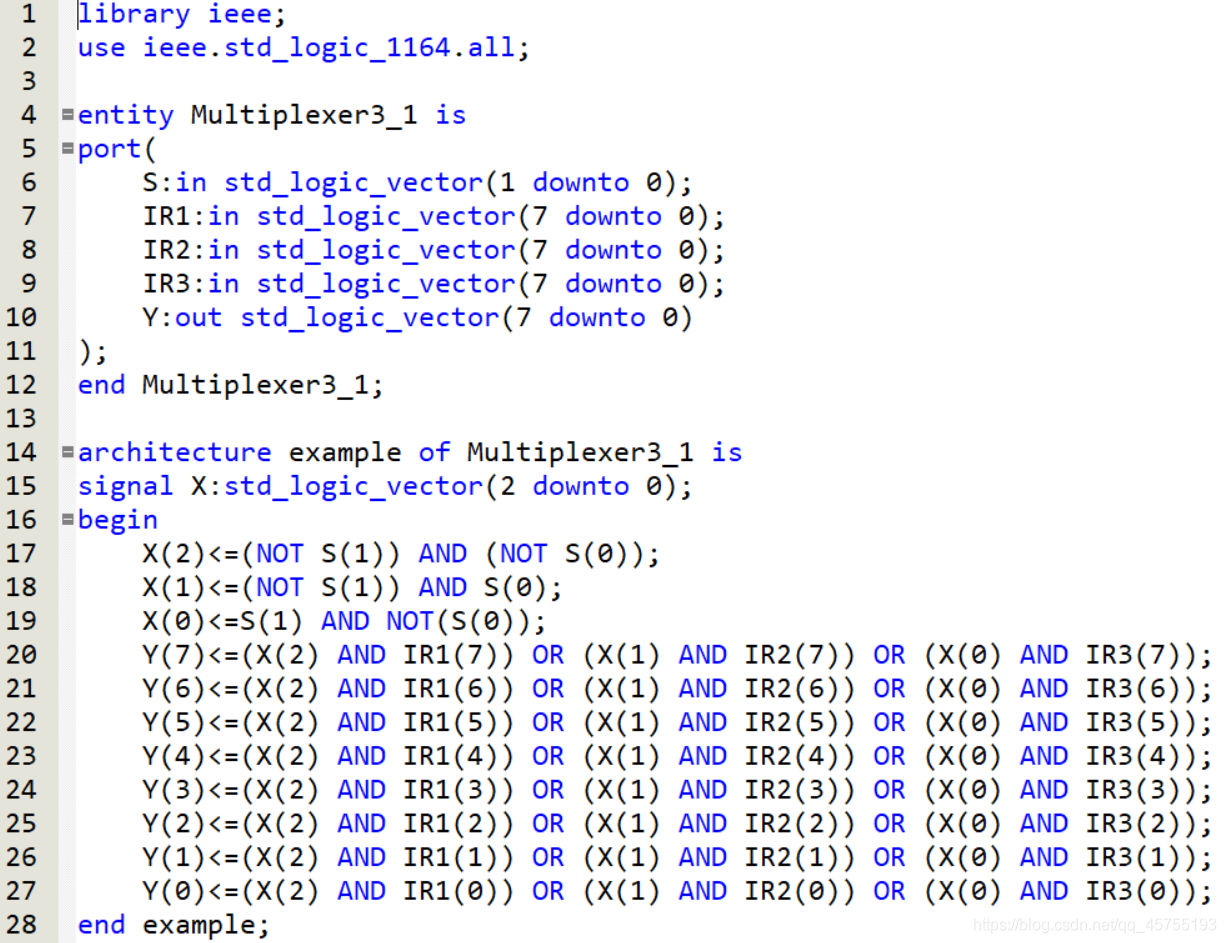

1.8重3-1多路复用器

- 编译过程

a)源代码如图(VHDL设计)

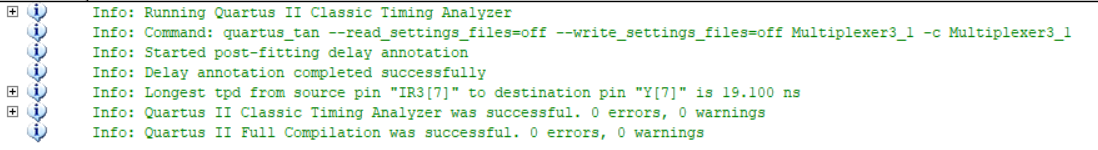

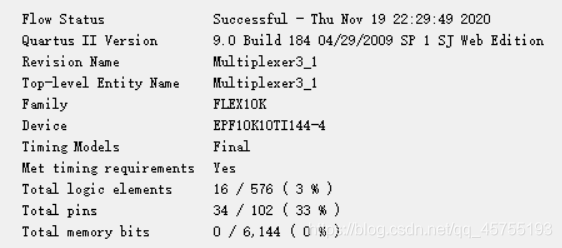

b)编译、调试过程

c)结果分析及结论

结果显示0 errors,0 warnings,VHDL文件满足题目要求。

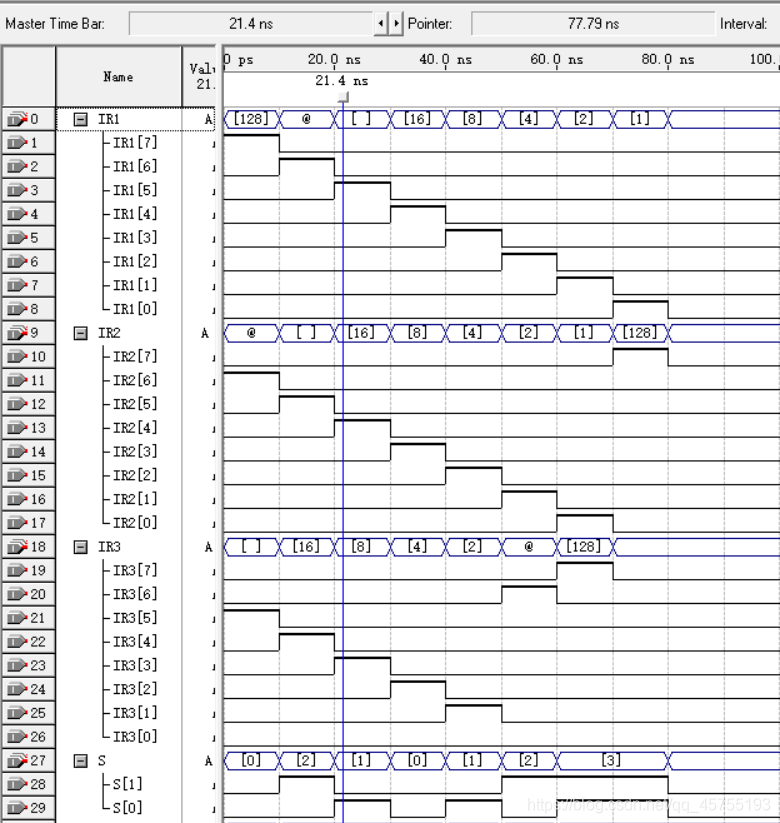

- 波形仿真

a)波形仿真过程(详见实验步骤)

b)波形仿真波形图

功能仿真波形图:

c)结果分析及结论

0-10ns对应: 控制端为00,输出IR1的8位向量 正确

10-20ns对应:控制端为10,输出IR3的8位向量 正确

20-30ns对应:控制端为01,输出IR2的8位向量 正确

30-40ns对应:控制端为00,输出IR1的8位向量 正确

40-50ns对应:控制端为01,输出IR2的8位向量 正确

50-60ns对应:控制端为10,输出IR3的8位向量 正确

60-80ns对应:控制端为11,输入为无效,无输出 正确

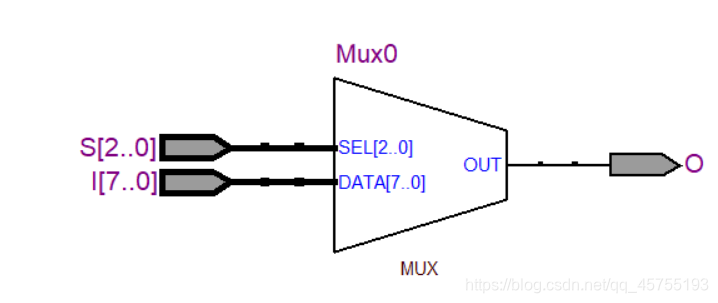

- 查看RTL Viewer

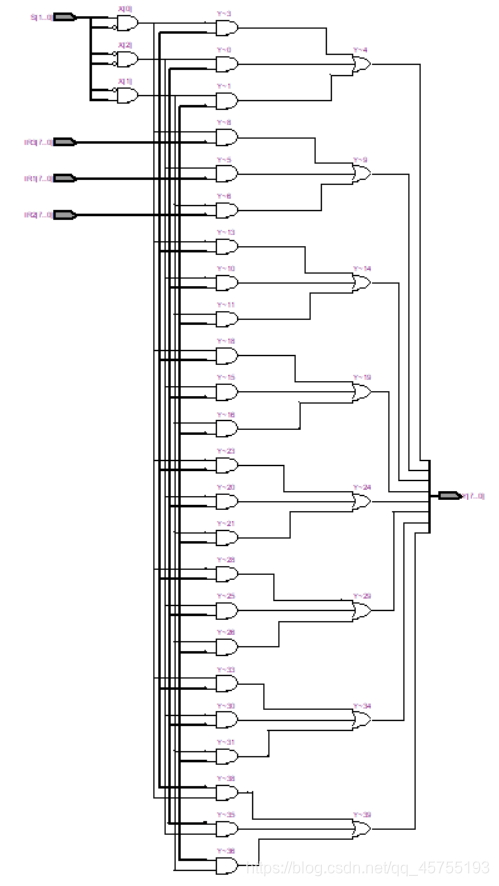

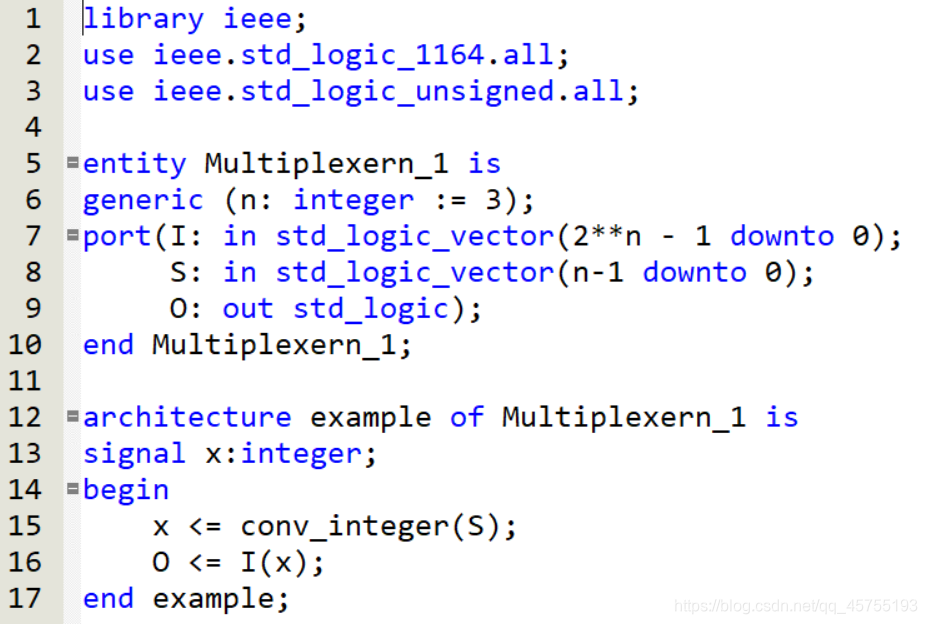

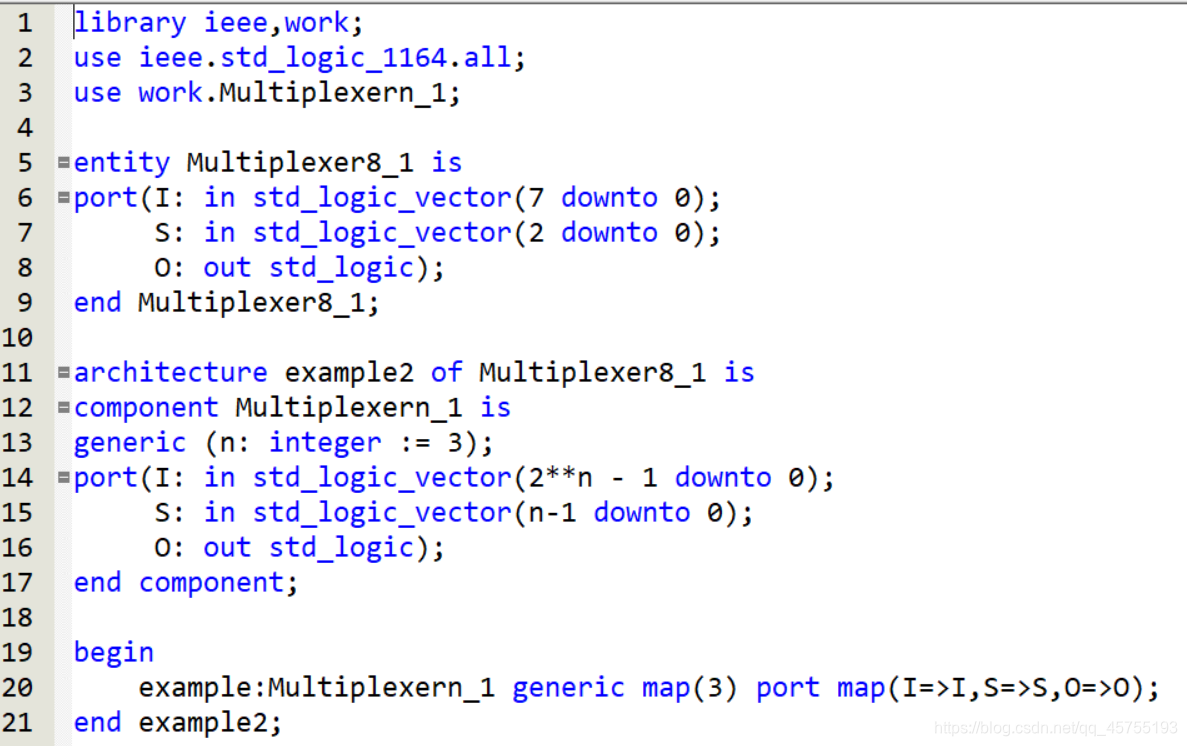

2. 8-1 多路复用器(调用n-1 多路复用器)

- 编译过程

a)源代码如图(VHDL设计)

1)n-1多路复用器的设计:

2)调用为8-1多路复用器

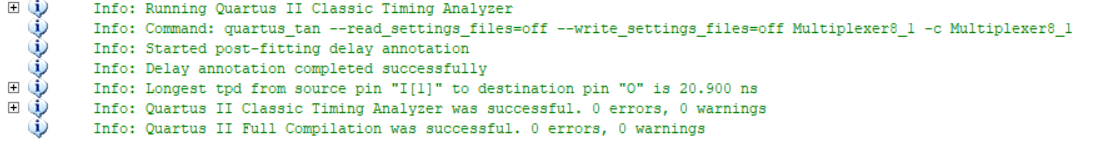

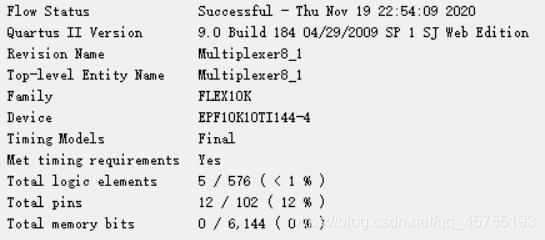

b)编译、调试过程

c)结果分析及结论

结果显示0 errors,0 warnings,VHDL文件满足题目要求。

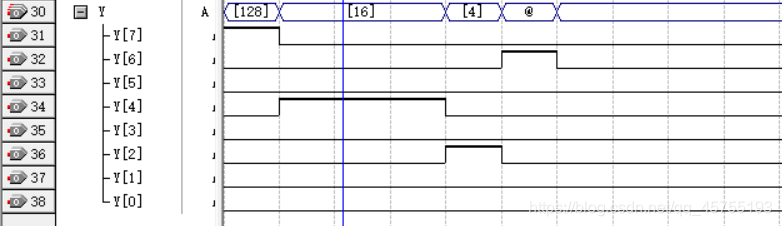

- 波形仿真

a)波形仿真过程(详见实验步骤)

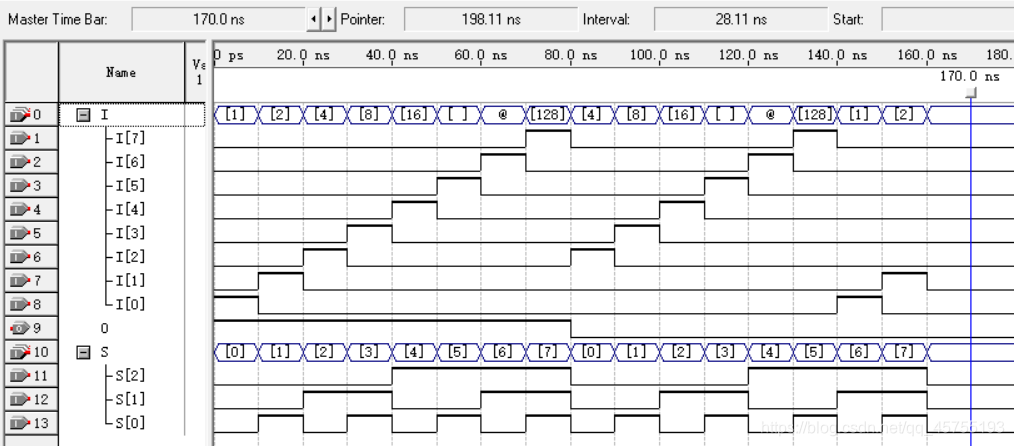

b)波形仿真波形图

功能仿真波形图:

c)结果分析及结论

0-10ns对应: 000对应I[0],I[0]为1,输出为1 正确

10-20ns对应:001对应I[1],I[1]为1,输出为1 正确

20-30ns对应:010对应I[2],I[2]为1,输出为1 正确

30-40ns对应:100对应I[3],I[3]为1,输出为1 正确

40-50ns对应:101对应I[4],I[4]为1,输出为1 正确

50-60ns对应:000对应I[5],I[5]为1,输出为1 正确

60-70ns对应:000对应I[6],I[6]为1,输出为1 正确

70-80ns对应:000对应I[7],I[7]为1,输出为1 正确

80-90ns对应: 000对应I[0],I[0]为0,输出为0 正确

90-100ns对应:001对应I[1],I[1]为0,输出为0 正确

100-110ns对应:010对应I[2],I[2]为0,输出为0 正确

110-120ns对应:100对应I[3],I[3]为0,输出为0 正确

120-130ns对应:101对应I[4],I[4]为0,输出为0 正确

130-140ns对应:000对应I[5],I[5]为0,输出为0 正确

140-150ns对应:000对应I[6],I[6]为0,输出为0 正确

150-160ns对应:000对应I[7],I[7]为0,输出为0 正确

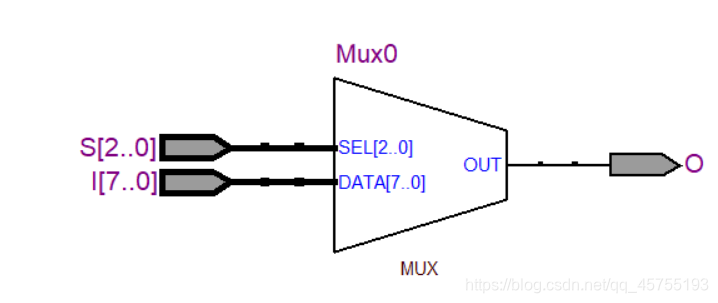

- 查看RTL Viewer

3. 4 位行波进位加法器

A.设计方法一:迭代法设计

- 编译过程

a)源代码如图(VHDL设计)

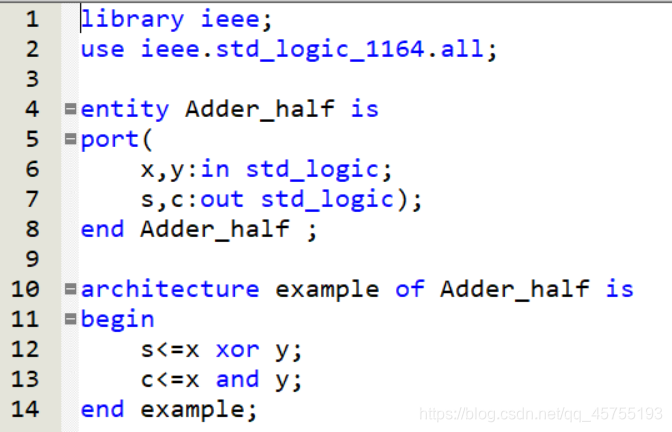

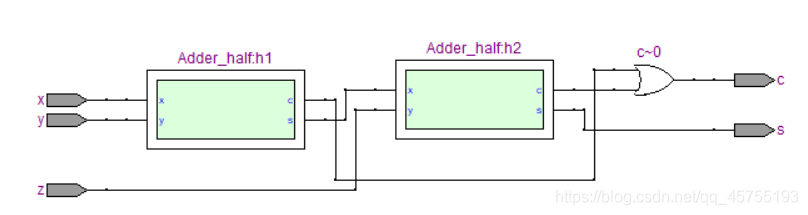

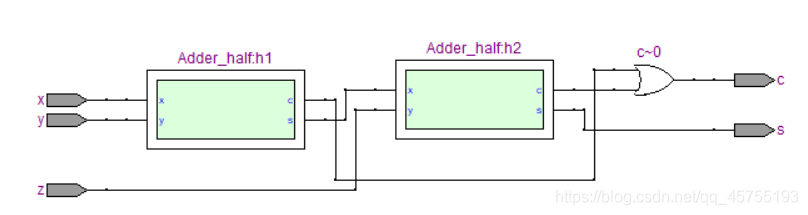

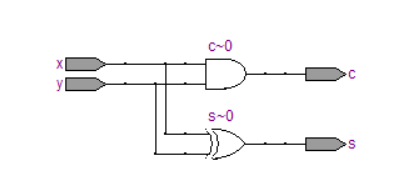

1)半加器VHDL设计:

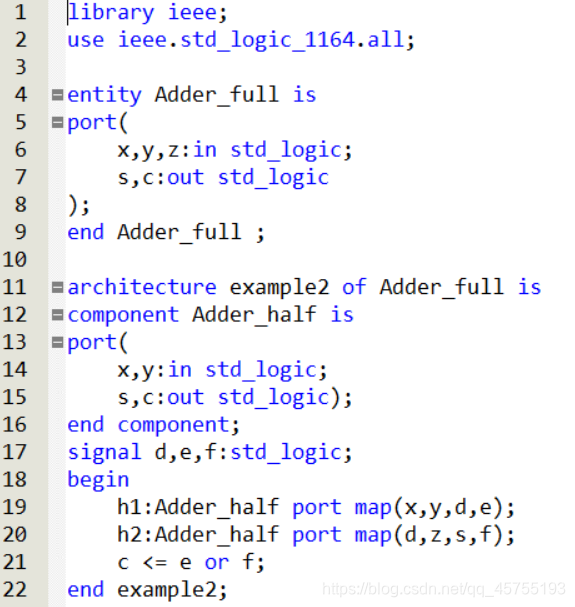

2)全加器设计(调用半加器):

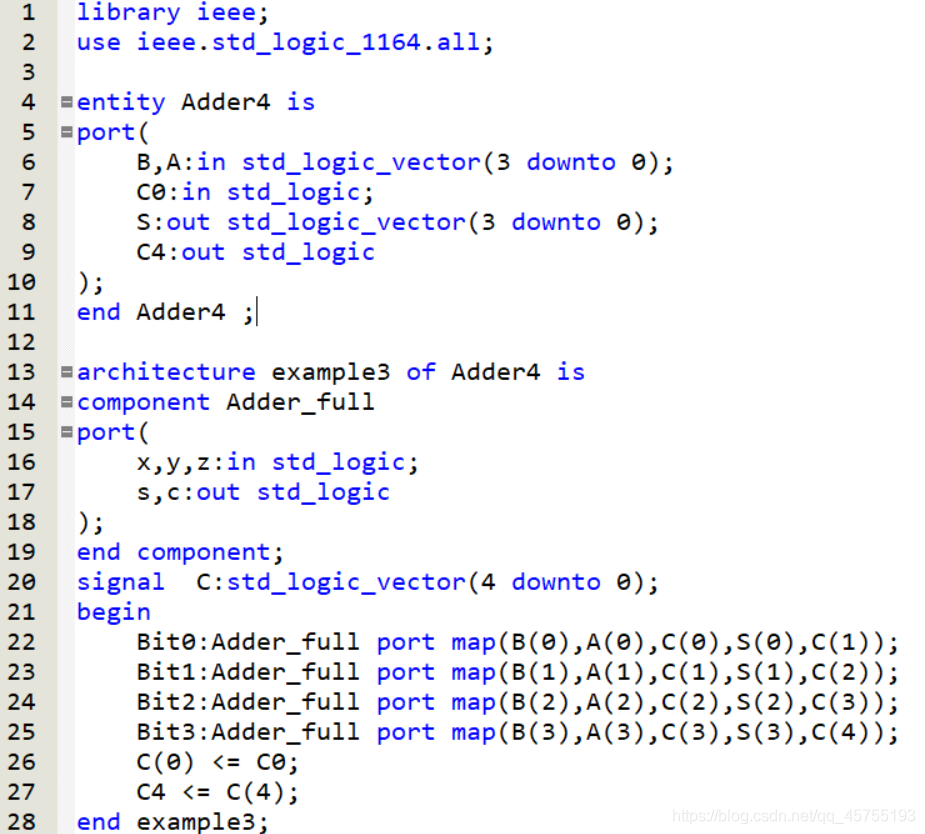

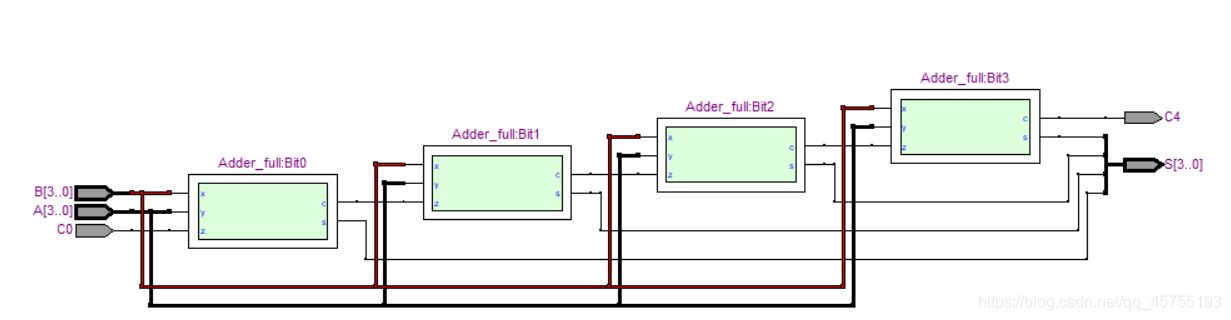

3)4位行波进位加法器设计(调用全加器)

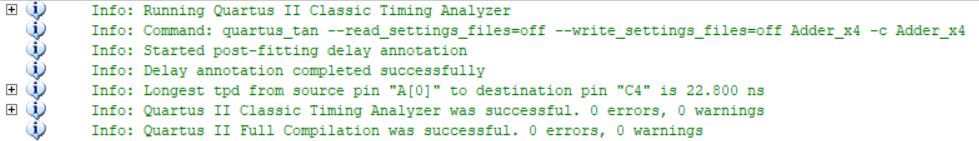

b)编译、调试过程

c)结果分析及结论

结果显示0 errors,0 warnings,VHDL文件满足题目要求,采用迭代思想设计。

- 波形仿真

a)波形仿真过程(详见实验步骤)

b)波形仿真波形图

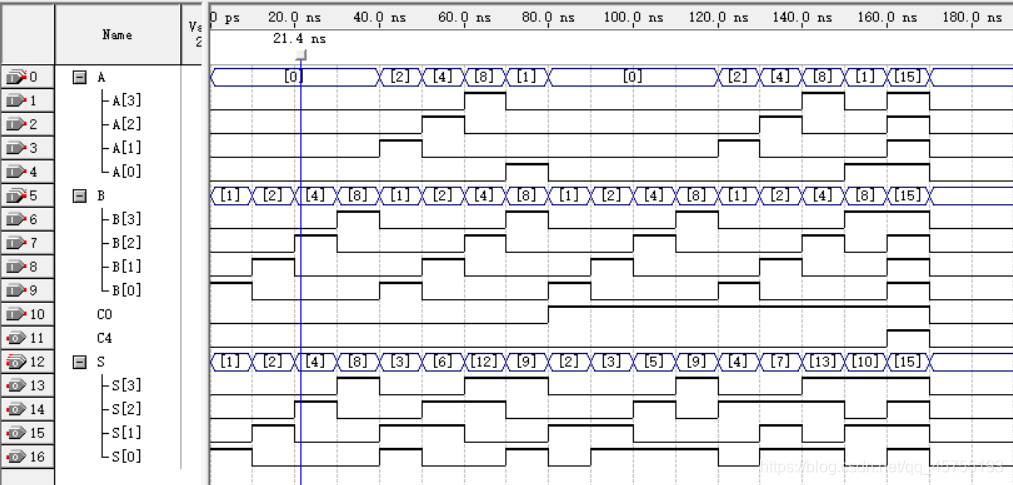

功能仿真波形图:

c)结果分析及结论

对于功能仿真:

0-10ns对应: 0000+0001+0=00001 正确

10-20ns对应: 0000+0010+0=00010 正确

20-30ns对应: 0000+0100+0=00100 正确

30-40ns对应: 0000+1000+0=01000 正确

40-50ns对应: 0010+0001+0=00011 正确

50-60ns对应: 0100+0010+0=00110 正确

60-70ns对应: 1000+0100+0=01100 正确

70-80ns对应: 0001+1000+0=01001 正确

80-90ns对应: 0000+0001+1=00010 正确

90-100ns对应: 0000+0010+1=00011 正确

100-110ns对应:0000+0100+1=00101 正确

110-120ns对应:0000+1000+1=01001 正确

120-130ns对应:0010+0001+1=00100 正确

130-140ns对应:0100+0010+1=00111 正确

140-150ns对应:1000+0100+1=01101 正确

150-160ns对应:0001+1000+1=01010 正确

150-160ns对应:1111+1111+1=11111 正确

3 查看RTL Viewer

- 四位行波进位加法器:

- 全加器:

- 半加器:

B.设计方法二:进位程序设计

1. 编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

c)结果分析及结论

结果显示0 errors,0 warnings,VHDL文件满足题目要求。

- 波形仿真

a)波形仿真过程(详见实验步骤)

b)波形仿真波形图

功能仿真波形图:

c)结果分析及结论

对于功能仿真:

0-10ns对应: 0000+0001+0=00001 正确

10-20ns对应: 0000+0010+0=00010 正确

20-30ns对应: 0000+0100+0=00100 正确

30-40ns对应: 0000+1000+0=01000 正确

40-50ns对应: 0010+0001+0=00011 正确

50-60ns对应: 0100+0010+0=00110 正确

60-70ns对应: 1000+0100+0=01100 正确

70-80ns对应: 0001+1000+0=01001 正确

80-90ns对应: 0000+0001+1=00010 正确

90-100ns对应: 0000+0010+1=00011 正确

100-110ns对应:0000+0100+1=00101 正确

110-120ns对应:0000+1000+1=01001 正确

120-130ns对应:0010+0001+1=00100 正确

130-140ns对应:0100+0010+1=00111 正确

140-150ns对应:1000+0100+1=01101 正确

150-160ns对应:0001+1000+1=01010 正确

150-160ns对应:1111+1111+1=11111 正确

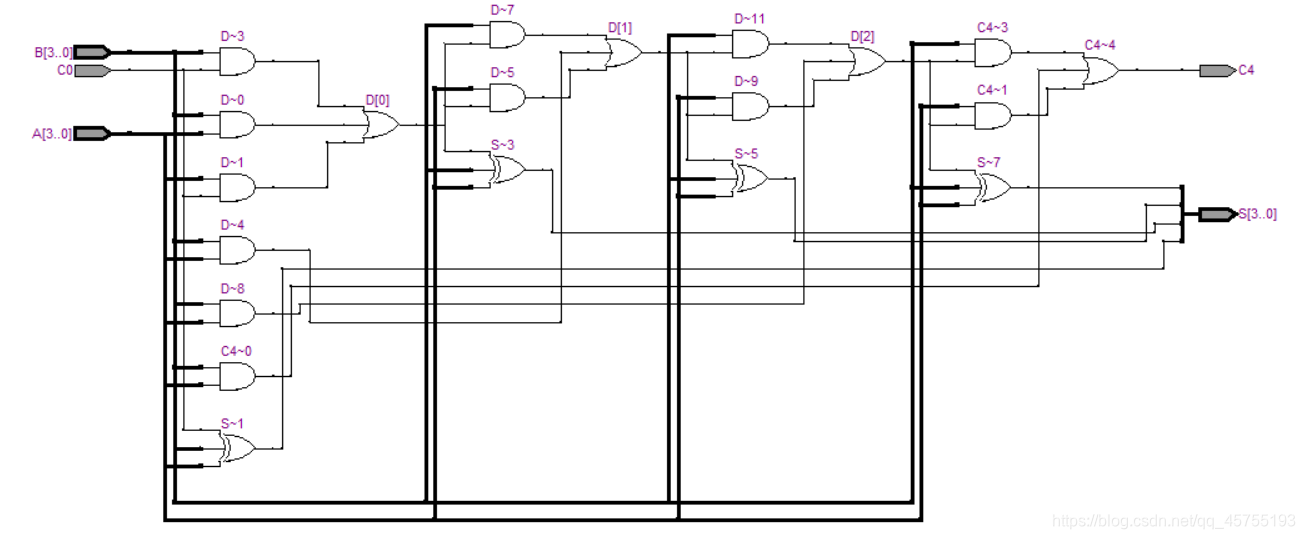

3 查看RTL Viewer

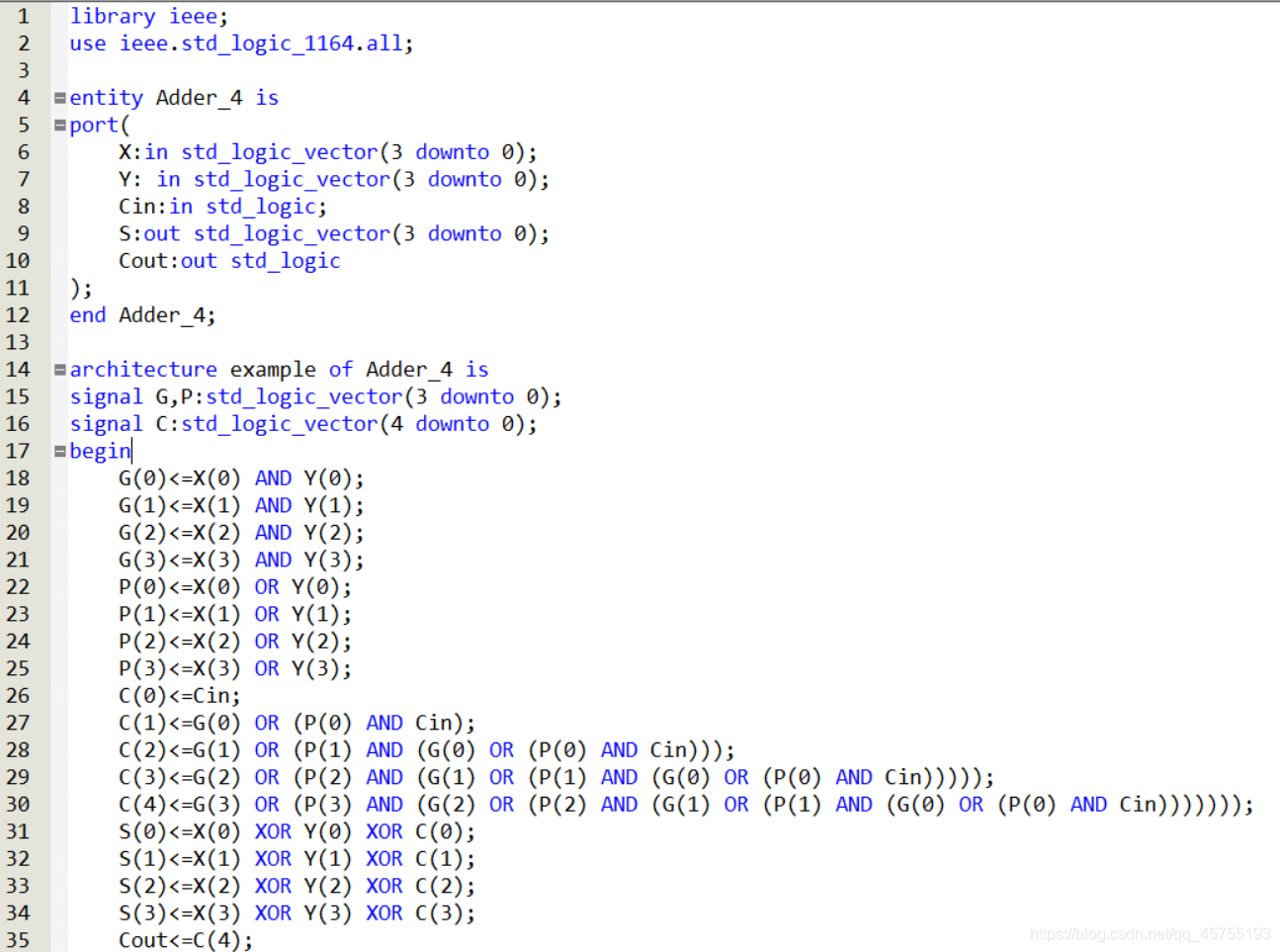

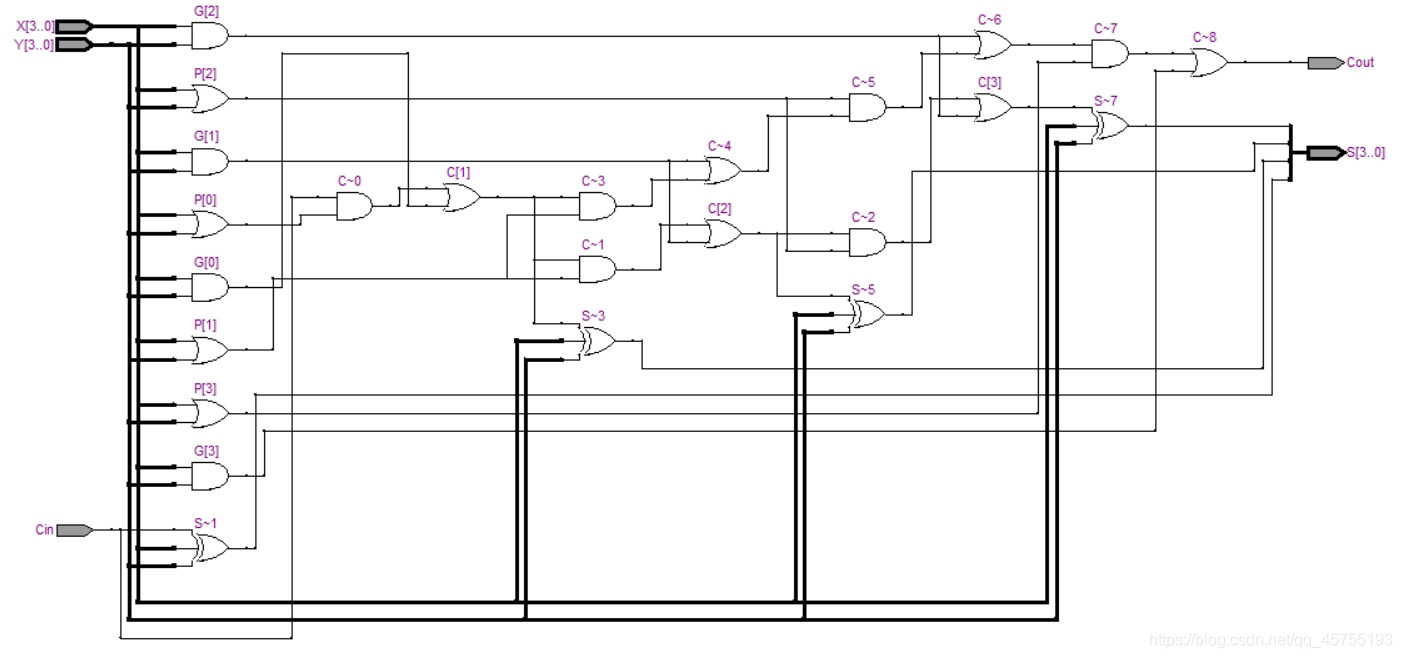

4. 4 位先行进位加法器

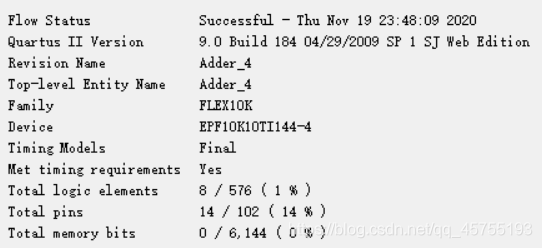

- 编译过程

a)源代码如图(VHDL设计)

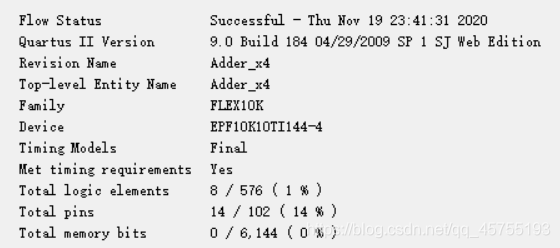

b)编译、调试过程

c)结果分析及结论

结果显示0 errors,0 warnings,VHDL文件满足题目要求。

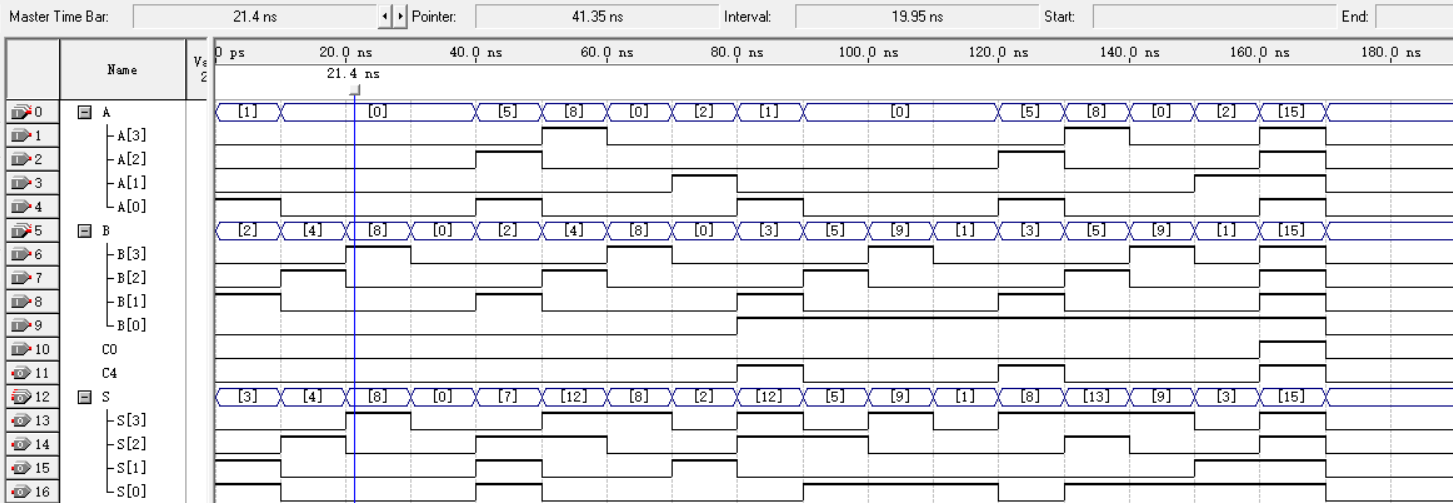

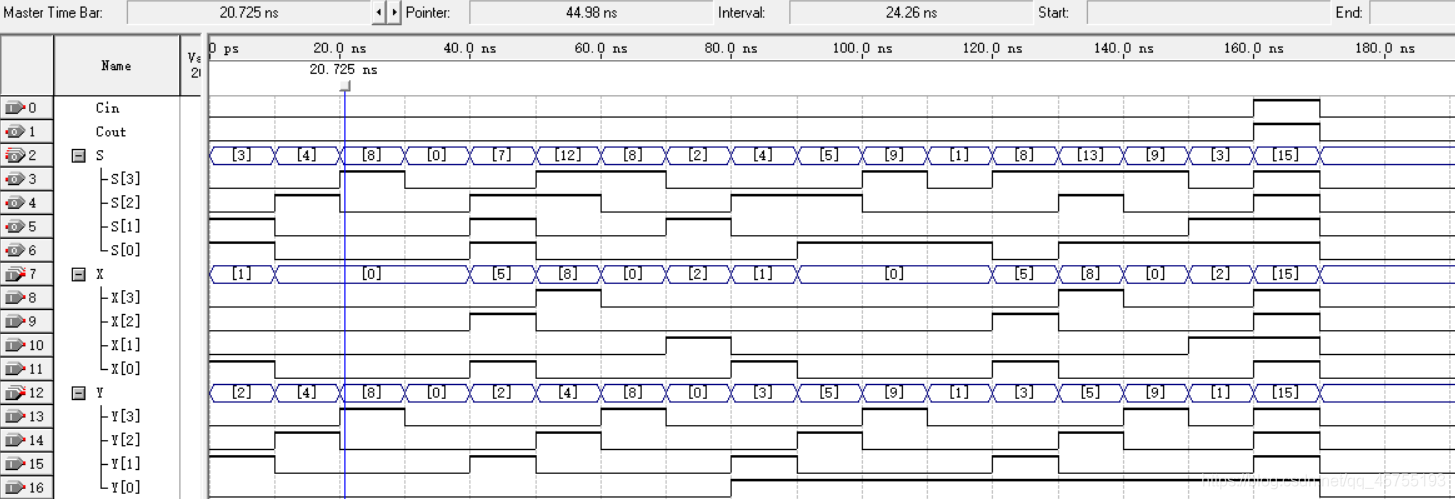

- 波形仿真

a)波形仿真过程(详见实验步骤)

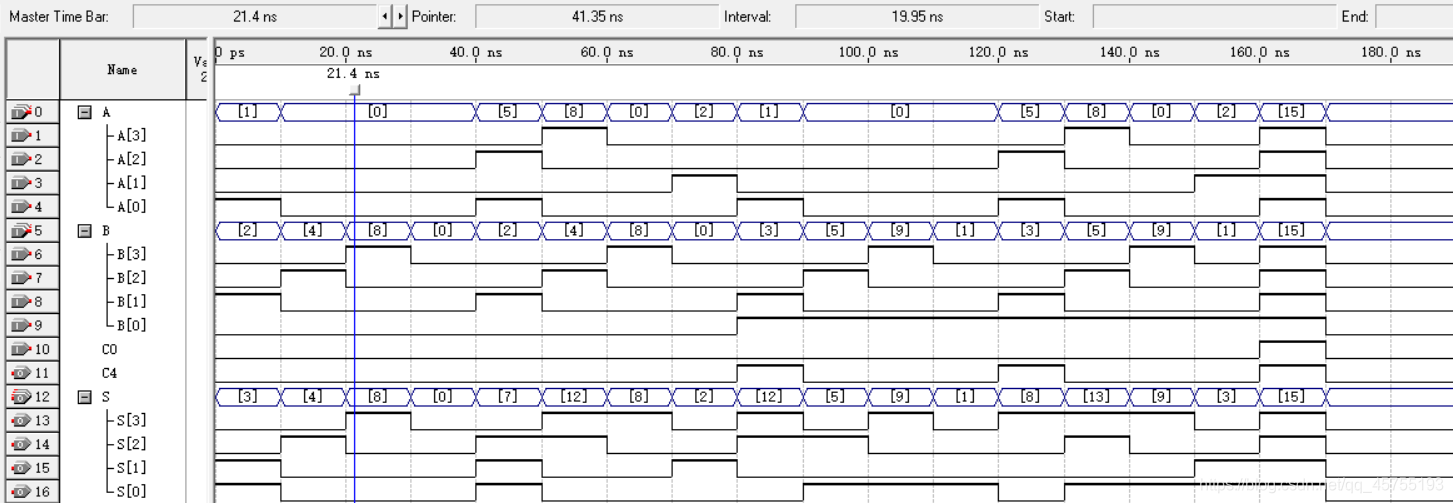

b)波形仿真波形图

功能仿真波形图:

c)结果分析及结论

对于功能仿真:

0-10ns对应: 0000+0001+0=00001 正确

10-20ns对应: 0000+0010+0=00010 正确

20-30ns对应: 0000+0100+0=00100 正确

30-40ns对应: 0000+1000+0=01000 正确

40-50ns对应: 0010+0001+0=00011 正确

50-60ns对应: 0100+0010+0=00110 正确

60-70ns对应: 1000+0100+0=01100 正确

70-80ns对应: 0001+1000+0=01001 正确

80-90ns对应: 0000+0001+1=00010 正确

90-100ns对应: 0000+0010+1=00011 正确

100-110ns对应:0000+0100+1=00101 正确

110-120ns对应:0000+1000+1=01001 正确

120-130ns对应:0010+0001+1=00100 正确

130-140ns对应:0100+0010+1=00111 正确

140-150ns对应:1000+0100+1=01101 正确

150-160ns对应:0001+1000+1=01010 正确

150-160ns对应:1111+1111+1=11111 正确

3 查看RTL Viewer

五、实验结论与心得

经过本次实验,我对Quartus II仿真软件有了更好的理解和运用,对VHDL语言的使用有了更好的掌握,熟练了创建工程文件、软件编译操作、仿真波形模拟等操作。

了解到VHDL语言可以使用模块并调用模块,熟练掌握了component语法的运用以及模块的调用设计,并利用不同方式使用模块。

为了更好地运用4 位行波进位加法器,熟悉其操作,分别采用了迭代法和进位程序设计,对比两者的RTL视图,更好地理解了迭代法对模块使用的好处以及优点。在实验过程中,写好4 位行波进位加法器和4 位先行进位加法器,通过对波形仿真的操作,明白了先行进位加法器无需等待进位输入的优点。

六、思考题

1.多路复用器的实现方法很多,请总结两种以上实现方法。

一是直接定制特定规模特定需求的多路复用器;

二是调用模块定制成不同规模的多路复用器。

2. 总结 VHDL 语言描述多路复用器的方法和常用语句。

VHDL语言的基本结构由库和程序包、实体、结构体组成,描述多路复用器常用语句有变量赋值语句、信号代入语句等。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!