【FPGA】基于状态机实现自动售货机模拟

文章目录

- 一、售货机功能

- 二、售货机状态分析及模块划分

- 三、代码实现

- 四、上板验证

一、售货机功能

此自动售货机模拟基于EP4CE6F17C8开发板实现,用按键,led灯,数码管表示各个输入输出

功能:

此自动售货机可以选择A(三元)与B(五元)商品且选择商品数量,一次可以投1块与5块钱。当投币数量满足商品价格时则能出货,且退款额外支付,在任意阶段皆可以取消支付并退款。

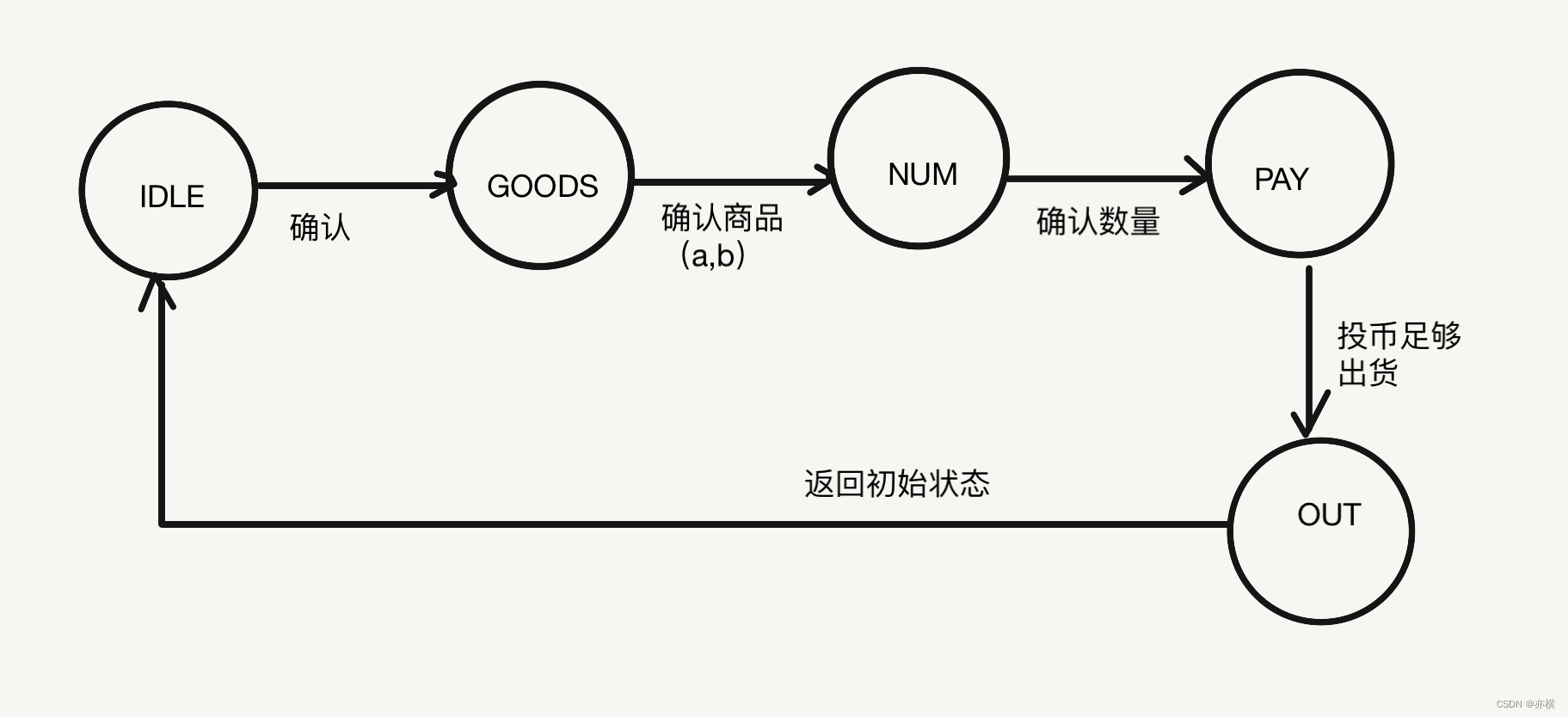

二、售货机状态分析及模块划分

IDLE(初始状态):key3确认进入GOODS状态

GOODS(选择商品状态):key1选择A商品(3元),led0亮,key2选择B商品(5元),led2亮,key3确认进入NUM状态

NUM(选择商品数量状态):key1商品数量加一,key2商品数量减一,在数码管第一位显示数量,商品数量不为0时按key3进入PAY状态,同时得到所需支付总价并在数码管三四位显示

PAY(支付状态):key1付款1元,key2付款5元,若投币数量小于商品总价则在五六位显示投币数量,且数码管第二位显示0表示无法出货,若投币数量大于等于商品总价则在五六位显示投币超出总价所需退款价格,数码管第二位显示1表示key出货,此时按下key3进入OUT状态。

OUT(出货状态):商品出货,四个led灯全亮。

因开发板按键数量不足,每个状态需要取消支付和出货后回到初始状态都用复位按键key4表示。

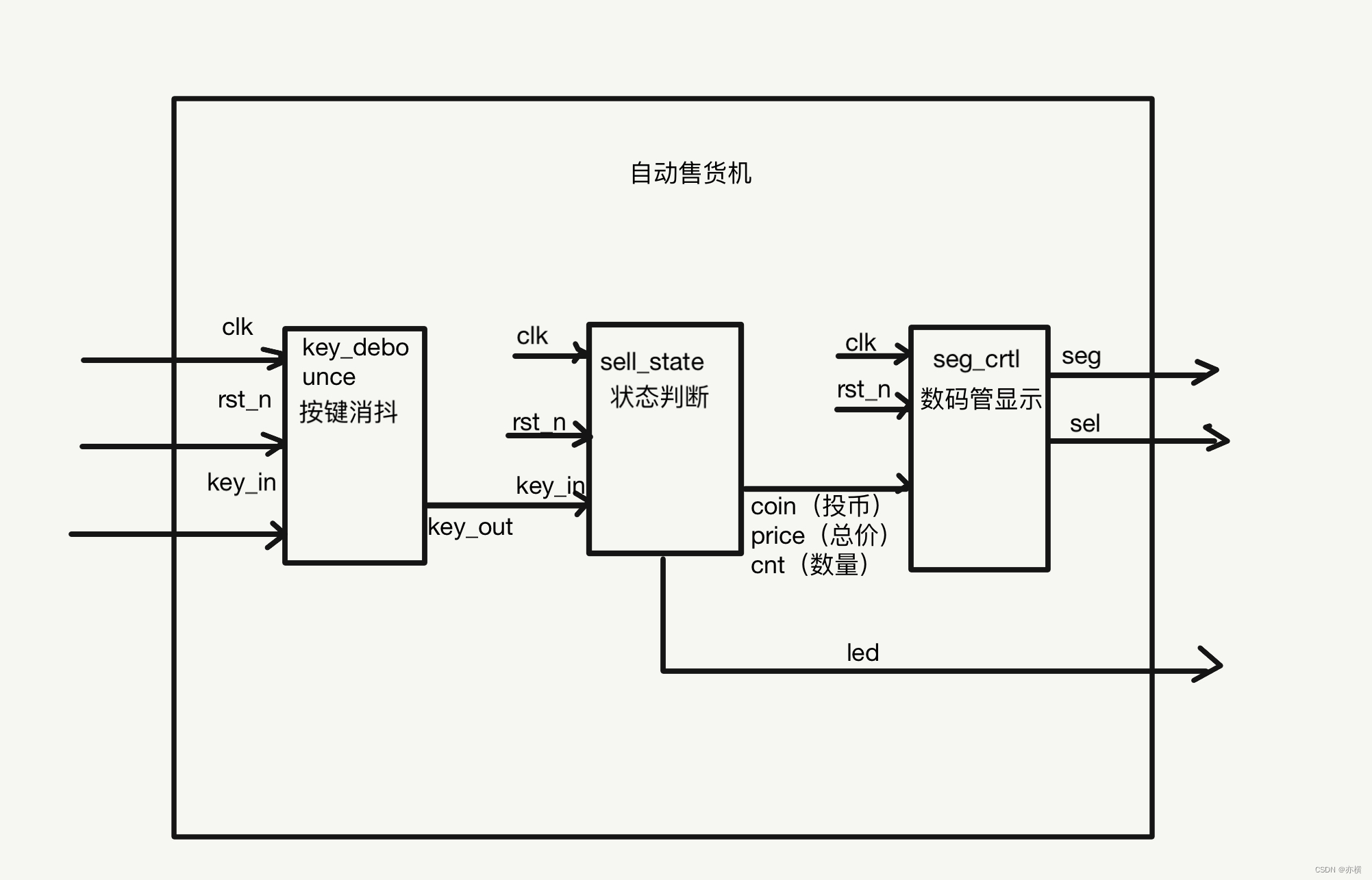

模块划分

三、代码实现

auto_sell(顶层模块)

module auto_sell(input clk,input rst_n,input [3:0] key_in,output [3:0] led,output [5:0] sel,output [7:0] seg

);wire [9:0] key_out ;

wire [9:0] price ;

wire [9:0] cnt ;

wire [9:0] coin ;key_debounce key_debounce0(.clk (clk),.rst_n (rst_n),.key_in (key_in),.key_out (key_out)

);seg_ctrl seg_ctrl0(.clk (clk),.rst_n (rst_n),.seg (seg),.sel (sel),.coin (coin),.price (price),.cnt (cnt)

);sell_state sell_state0(.clk (clk),.rst_n (rst_n),.key_in (key_out),.led (led),.coin (coin),.price (price),.cnt (cnt)

);endmodule

key_debounce(按键消抖模块)

//4按键消抖

module key_debounce(input clk,input rst_n,input [3:0]key_in, // 按键输出,1是没有按下,0是按output reg [3:0]key_out // 消抖后的按键输出,此时1为按下

);parameter TIME_DELAY = 1_000_000; // 延时时间20msreg [19:0]cnt0 ; // 计数器reg [19:0]cnt1 ; // 计数器reg [19:0]cnt2 ; // 计数器reg [19:0]cnt3 ; // 计数器wire add_cnt0 ; // 计数开始标志wire end_cnt0 ; // 计数结束标志wire add_cnt1 ; // 计数开始标志wire end_cnt1 ; // 计数结束标志wire add_cnt2 ; // 计数开始标志wire end_cnt2 ; // 计数结束标志wire add_cnt3 ; // 计数开始标志wire end_cnt3 ; // 计数结束标志reg [3:0]key_before ; // 前一时刻电平状态reg [3:0]key_now ; // 当前时刻电平状态wire flag_fall0 ; // 抖动标志wire flag_fall1 ; // 抖动标志wire flag_fall2 ; // 抖动标志wire flag_fall3 ; // 抖动标志reg flag_timing0; // 计时标志,1为在计时reg flag_timing1; // 计时标志,1为在计时reg flag_timing2; // 计时标志,1为在计时reg flag_timing3; // 计时标志,1为在计时// 当前按键电平设置always @(posedge clk or negedge rst_n) beginif (!rst_n)key_now <= 4'b1111;elsekey_now <= key_in;end// 前一时刻按键电平设置always @(posedge clk or negedge rst_n) beginif (!rst_n)key_before <= 4'b1111;elsekey_before <= key_now;end// 边沿检测(前一个时刻高电平,下一个时刻低电平,就是出现了下降沿,相反是上升沿),开始抖动assign flag_fall0 = (key_before[0] && !key_now[0]);assign flag_fall1 = (key_before[1] && !key_now[1]);assign flag_fall2 = (key_before[2] && !key_now[2]);assign flag_fall3 = (key_before[3] && !key_now[3]);// 计时标志判断0always @(posedge clk or negedge rst_n) beginif (!rst_n)flag_timing0 <= 1'b0;else if (flag_fall0) flag_timing0 <= 1'b1;else if (end_cnt0) flag_timing0 <= 1'b0;else flag_timing0 <= flag_timing0 ;end// 计时标志判断1always @(posedge clk or negedge rst_n) beginif (!rst_n)flag_timing1 <= 1'b0;else if (flag_fall1) flag_timing1 <= 1'b1;else if (end_cnt1) flag_timing1 <= 1'b0;else flag_timing1 <= flag_timing1 ;end// 计时标志判断2always @(posedge clk or negedge rst_n) beginif (!rst_n)flag_timing2 <= 1'b0;else if (flag_fall2) flag_timing2 <= 1'b1;else if (end_cnt2) flag_timing2 <= 1'b0;else flag_timing2 <= flag_timing2 ;end// 计时标志判断3always @(posedge clk or negedge rst_n) beginif (!rst_n)flag_timing3 <= 1'b0;else if (flag_fall3) flag_timing3 <= 1'b1;else if (end_cnt3) flag_timing3 <= 1'b0;else flag_timing3 <= flag_timing3 ;end// 计数器0always @(posedge clk or negedge rst_n) beginif (!rst_n)cnt0 <= 20'd0;else if (add_cnt0) begin if (end_cnt0)cnt0 <= 20'd0;elsecnt0 <= cnt0 + 1'd1;endelse cnt0 <= 20'd0;end// 计数器1always @(posedge clk or negedge rst_n) beginif (!rst_n)cnt1 <= 20'd0;else if (add_cnt1) begin if (end_cnt1)cnt1 <= 20'd0;elsecnt1 <= cnt1 + 1'd1;endelse cnt1 <= 20'd0;end// 计数器2always @(posedge clk or negedge rst_n) beginif (!rst_n)cnt2 <= 20'd0;else if (add_cnt2) begin if (end_cnt2)cnt2 <= 20'd0;elsecnt2 <= cnt2 + 1'd1;endelse cnt2 <= 20'd0;end// 计数器3always @(posedge clk or negedge rst_n) beginif (!rst_n)cnt3 <= 20'd0;else if (add_cnt3) begin if (end_cnt3)cnt3 <= 20'd0;elsecnt3 <= cnt3 + 1'd1;endelse cnt3 <= 20'd0;endassign add_cnt0 = flag_timing0; //开始计数条件assign end_cnt0 = ((cnt0==TIME_DELAY-1) && add_cnt0); //结束计时条件assign add_cnt1 = flag_timing1; //开始计数条件assign end_cnt1 = ((cnt1==TIME_DELAY-1) && add_cnt1); //结束计时条件assign add_cnt2 = flag_timing2; //开始计数条件assign end_cnt2 = ((cnt2==TIME_DELAY-1) && add_cnt2); //结束计时条件assign add_cnt3 = flag_timing3; //开始计数条件assign end_cnt3 = ((cnt3==TIME_DELAY-1) && add_cnt3); //结束计时条件// 消抖后的按键输出always @(posedge clk or negedge rst_n) beginif (!rst_n)key_out[0] <= 1'b0;else if (end_cnt0)key_out[0] <= ~key_now[0];elsekey_out[0] <= 1'b0;end// 消抖后的按键输出always @(posedge clk or negedge rst_n) beginif (!rst_n)key_out[1] <= 1'b0;else if (end_cnt1)key_out[1] <= ~key_now[1];elsekey_out[1] <= 1'b0;end// 消抖后的按键输出always @(posedge clk or negedge rst_n) beginif (!rst_n)key_out[2] <= 1'b0;else if (end_cnt2)key_out[2] <= ~key_now[2];elsekey_out[2] <= 1'b0;end // 消抖后的按键输出always @(posedge clk or negedge rst_n) beginif (!rst_n)key_out[3] <= 1'b0;else if (end_cnt3)key_out[3] <= ~key_now[3];elsekey_out[3] <= 1'b0;end

endmodule

sell_state(状态机判断及逻辑模块)

module sell_state(input clk,input rst_n,input [3:0] key_in,output reg [3:0] led,output reg [9:0] coin, //投币总价output reg [9:0] price,//商品总价output reg [9:0] cnt //商品数量

);reg [4:0] state_c ;

reg [4:0] state_n ;reg [9:0] A_select;

reg [9:0] B_select;localparamIDLE = 5'b00001 ,GOODS = 5'b00010 ,NUM = 5'b00100 ,PAY = 5'b01000 ,OUT = 5'b10000 ;wire IDLE_GOODS ;

wire GOODS_NUM ;

wire NUM_PAY ;

wire PAY_OUT ;

wire OUT_IDLE ;//状态转移条件

assign IDLE_GOODS = IDLE && ( key_in == 4'b0100 ) ;

assign GOODS_NUM = GOODS && ( key_in == 4'b0100 ) && ( A_select || B_select ) ;

assign NUM_PAY = NUM && ( key_in == 4'b0100 ) && ( cnt != 0 ) ;

assign PAY_OUT = PAY && ( key_in == 4'b0100 ) && ( coin >= price ) ;

assign OUT_IDLE = OUT && ( key_in == 4'b0100 ) ;//状态机第一段

always @(posedge clk or negedge rst_n)beginif(!rst_n)state_c <= IDLE ;elsestate_c <= state_n ;

end//状态机第二段

always @(*)begincase(state_c)IDLE : beginif(IDLE_GOODS)state_n <= GOODS ;elsestate_n <= state_c ;endGOODS: beginif(GOODS_NUM)state_n <= NUM ;elsestate_n <= state_c ;endNUM : beginif(NUM_PAY)state_n <= PAY ;elsestate_n <= state_c ;endPAY : beginif(PAY_OUT)state_n <= OUT ;elsestate_n <= state_c ;endOUT : beginif(OUT_IDLE)state_n <= IDLE ;elsestate_n <= state_c ;endendcase

end//商品选择A或B

always @(posedge clk or negedge rst_n)beginif(!rst_n)beginA_select <= 1'b0 ;B_select <= 1'b0 ;endelse if(state_c == GOODS)beginif(key_in==4'b0001)beginA_select <= 1'b1 ;B_select <= 1'b0 ;endelse if(key_in==4'b0010)beginA_select <= 1'b0 ;B_select <= 1'b1 ;endelse beginA_select <= A_select ;B_select <= B_select ;endend else beginA_select <= A_select ;B_select <= B_select ;end

end//商品数量选择

always @(posedge clk or negedge rst_n)beginif(!rst_n)cnt <= 1'b0 ;else if(state_c == NUM)beginif(key_in==4'b0001)cnt <= cnt + 1 ;else if(key_in==4'b0010)cnt <= cnt - 1 ;else cnt <= cnt ;end elsecnt <= cnt ;

end//投币数量

always @(posedge clk or negedge rst_n)beginif(!rst_n)coin <= 1'b0 ;else if(state_c == PAY)beginif(key_in==4'b0001)coin <= coin + 1'b1 ;else if(key_in==4'b0010)coin <= coin + 3'd5 ;else coin <= coin;end elsecoin <= 1'b0 ;

end//商品总价

always @(posedge clk or negedge rst_n)beginif(!rst_n)price <= 1'b0 ;else if(state_c == PAY)beginif(A_select)price <= 3 * cnt ;//A商品三元else if(B_select)price <= 5 * cnt ;//B商品三元else price <= price ;end elseprice <= 1'b0 ;

end//确认出货

always @(posedge clk or negedge rst_n)beginif(!rst_n)led <= 4'b0000 ;else if(state_c == OUT)led <= 4'b1111 ;else if(state_c == GOODS)beginif(key_in==4'b0001)led <= 4'b0001 ;else if(key_in==4'b0010)led <= 4'b0010 ;elseled <= led ;end elseled <= led ;

endendmodule

seg_ctrl(数码管显示模块)

module seg_ctrl(input clk,input rst_n,input [9:0] coin,input [9:0] price,input [9:0] cnt,output reg [7:0] seg,output reg [5:0] sel

);wire [9:0] change ;//找零

wire [9:0] change_bit ;//找零的个位数字

wire [9:0] change_Ten ;//找零的十位数字

wire [9:0] Bit ;//总消费个位数字

wire [9:0] Ten ;//总消费十位数字assign Bit = price%10 ;//取总价钱个位

assign Ten = (price/10)%10 ;//取总价钱十位

assign change_bit = change%10 ;//取找零个位

assign change_Ten = (change_Ten/10)%10;//取找零十位//投的币大于等于消费总和,找剩余的钱,小于消费总和,全部退回

assign change=(coin>=price)?(coin-price):coin;//每位数码管显示

reg [7:0] seg0;

reg [7:0] seg1;

reg [7:0] seg2;

reg [7:0] seg3;

reg [7:0] seg4;

reg [7:0] seg5;//第一位数码管显示商品数量

always@(posedge clk or negedge rst_n)beginif(!rst_n)beginseg0<=8'b1100_0000;endelse case(cnt)4'd0 : seg0 <= 8'b1100_0000;4'd1 : seg0 <= 8'b1111_1001;4'd2 : seg0 <= 8'b1010_0100;4'd3 : seg0 <= 8'b1011_0000;4'd4 : seg0 <= 8'b1001_1001;4'd5 : seg0 <= 8'b1001_0010;4'd6 : seg0 <= 8'b1000_0010;4'd7 : seg0 <= 8'b1111_1000;4'd8 : seg0 <= 8'b1000_0000;4'd9 : seg0 <= 8'b1001_0000;default: seg0 <= 8'b1100_0000;endcase

end//第二位显示是否能出货

always@(posedge clk or negedge rst_n)beginif(!rst_n)beginseg1 <= 8'b1100_0000;endelse if(coin>=price && price != 0)seg1 <= 8'b1111_1001;elseseg1 <= 8'b1100_0000;

end//第三位数码管显示消费总和个位

always@(posedge clk or negedge rst_n)beginif(!rst_n)beginseg2<=8'b1100_0000;endelse case(Bit)4'd0 : seg2 <= 8'b1100_0000;4'd1 : seg2 <= 8'b1111_1001;4'd2 : seg2 <= 8'b1010_0100;4'd3 : seg2 <= 8'b1011_0000;4'd4 : seg2 <= 8'b1001_1001;4'd5 : seg2 <= 8'b1001_0010;4'd6 : seg2 <= 8'b1000_0010;4'd7 : seg2 <= 8'b1111_1000;4'd8 : seg2 <= 8'b1000_0000;4'd9 : seg2 <= 8'b1001_0000;default: seg2 <= 8'b1100_0000;endcase

end//第四位数码管显示消费总和十位

always@(posedge clk or negedge rst_n)beginif(!rst_n)beginseg3<=8'b1100_0000;endelse case(Ten)4'd0 : seg3<= 8'b1100_0000;4'd1 : seg3<= 8'b1111_1001;4'd2 : seg3<= 8'b1010_0100;4'd3 : seg3<= 8'b1011_0000;4'd4 : seg3<= 8'b1001_1001;4'd5 : seg3<= 8'b1001_0010;4'd6 : seg3<= 8'b1000_0010;4'd7 : seg3<= 8'b1111_1000;4'd8 : seg3<= 8'b1000_0000;4'd9 : seg3<= 8'b1001_0000;default: seg3<= 8'b1100_0000;endcase

end//第五位数码管显示找零个位

always@(posedge clk or negedge rst_n)beginif(!rst_n)beginseg4<=8'b1100_0000;endelse case(change_bit)4'd0 : seg4 <= 8'b1100_0000;4'd1 : seg4 <= 8'b1111_1001;4'd2 : seg4 <= 8'b1010_0100;4'd3 : seg4 <= 8'b1011_0000;4'd4 : seg4 <= 8'b1001_1001;4'd5 : seg4 <= 8'b1001_0010;4'd6 : seg4 <= 8'b1000_0010;4'd7 : seg4 <= 8'b1111_1000;4'd8 : seg4 <= 8'b1000_0000;4'd9 : seg4 <= 8'b1001_0000;default: seg4 <= 8'b1100_0000;endcase

end//第六位数码管显示找零十位

always@(posedge clk or negedge rst_n)beginif(!rst_n)beginseg5<=8'b1100_0000;endelse case(change_Ten)4'd0 : seg5 <= 8'b1100_0000;4'd1 : seg5 <= 8'b1111_1001;4'd2 : seg5 <= 8'b1010_0100;4'd3 : seg5 <= 8'b1011_0000;4'd4 : seg5 <= 8'b1001_1001;4'd5 : seg5 <= 8'b1001_0010;4'd6 : seg5 <= 8'b1000_0010;4'd7 : seg5 <= 8'b1111_1000;4'd8 : seg5 <= 8'b1000_0000;4'd9 : seg5 <= 8'b1001_0000;default: seg5 <= 8'b1100_0000;endcase

end//根据哪位数码管亮显示对应的

always @(posedge clk or negedge rst_n) beginif(!rst_n)beginseg<=8'b1100_0000;endelse begincase(sel)6'b111110:seg<=seg0;6'b111101:seg<=seg1;6'b111011:seg<=seg2;6'b110111:seg<=seg3;6'b101111:seg<=seg4;6'b011111:seg<=seg5;endcaseend

endparameter CNT_1MS = 50000 ;

reg [15:0] cnt_1ms ;//1ms计数器

always @(posedge clk or negedge rst_n) beginif(!rst_n)begincnt_1ms <= 0 ;endelse if(cnt_1ms==CNT_1MS)begincnt_1ms <= 0 ;endelsecnt_1ms <= cnt_1ms+1 ;

end//位选,每1ms切换数码管显示

always @(posedge clk or negedge rst_n) beginif(!rst_n)beginsel <= 6'b111110 ;endelse if(cnt_1ms == CNT_1MS-1)sel <= { sel[4:0] , sel[5] } ;else sel<=sel ;

endendmodule

四、上板验证

KEY1确认>A商品>3件,九元>付款11元>退款两元,商品出货

可以看出,需求功能实现了。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!