alu电路 计算机组成原理实验,计算机组成原理-实验三-多功能ALU设计实验

实验要求:

本实验要求设计一个具有8种运算功能的32位ALU,并能够产生运算结果的表示:结果为零标志ZF(Zero Flag)、进借位标志位CF()溢出标志OF(Overflow Flag)、符号位标志SF(Sign Flag)和奇偶标志PF(Parity Flag),标志位值解释见代码。ALU通过4根控制线ALU_OP[3:0]来选择其8种功能,功能见表所示,多余的8位用于后继运算的拓展备用。

功能表

ALU_OP[3:0]ALU功能功能说明

0000and按位与运算

0001or按位或运算

0010xor按位异或运算

0011nor按位或非运算

0100add算术加运算

0101sub算术减运算

0110slt若A

0111sllB逻辑左移A所指定的位数

实验IDE采用Vivado,开发语言Verilog。

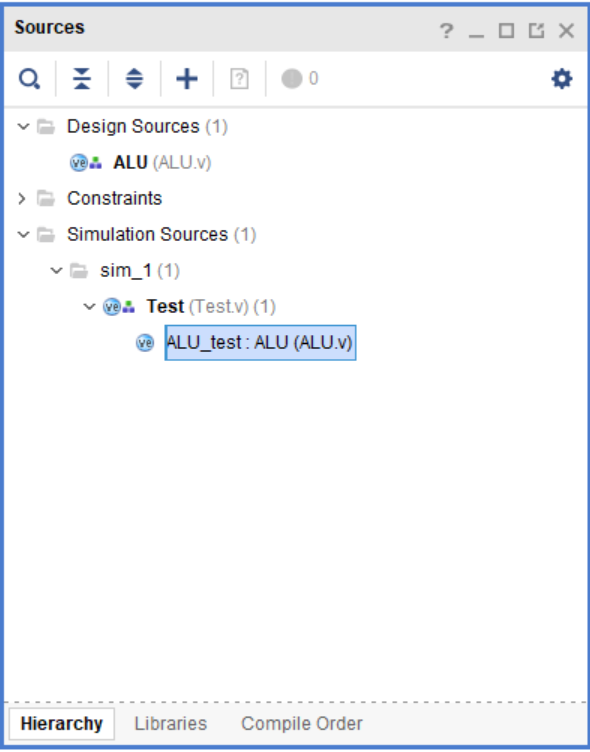

程序模块结构图:

ALU运算器模块代码:`timescale 1ns / 1ps

//ALU模块

module ALU(OP,A,B,F,ZF,CF,OF,SF,PF);

parameter SIZE = 32;//运算位数

input [3:0] OP;//运算操作

input [SIZE:1] A;//左运算数

input [SIZE:1] B;//右运算数

out

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!