Verilog-实现使用计数器得到特定时间的高脉冲信号

文章目录

- 一、概述

- 二、实现方法及代码

- 1、框图,端口及相关信号

- 2、代码实现

一、概述

本篇博客主要介绍:使用计数器来得到自己想要的的一段脉冲信号。

二、实现方法及代码

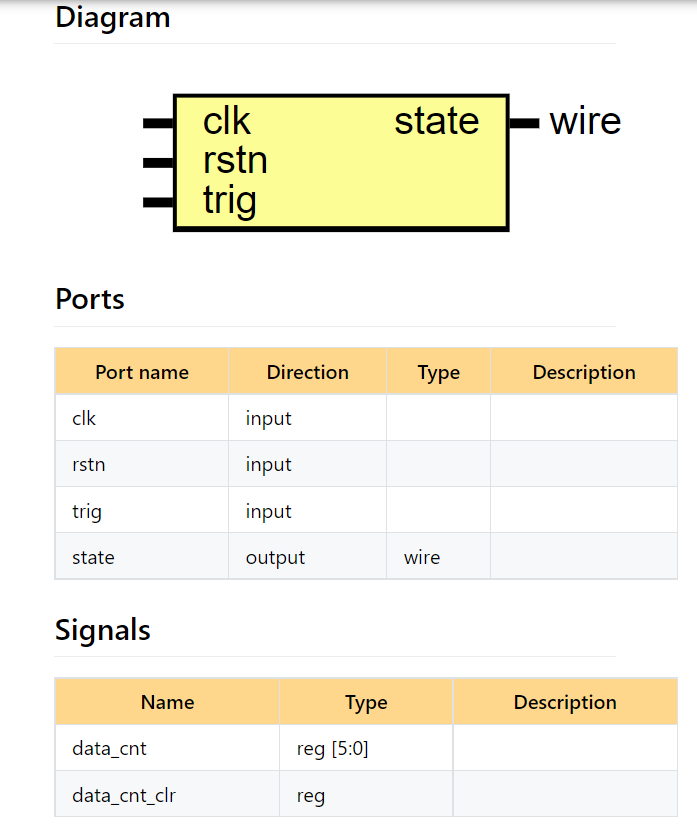

1、框图,端口及相关信号

2、代码实现

Verilog实现`timescale 1ns/1ps

module data_cnt (input clk, //50MHZ 20nsinput rstn,input trig, //触发信号 一个时钟周期output wire state //得到1us的高脉冲信号

);//define

reg [5:0] data_cnt; //1us 50

reg data_cnt_clr;//----------------1us计数器----------------//

always @(posedge clk or negedge rstn) beginif (!rstn) data_cnt <= 6'd0;else if(!data_cnt_clr) // 等于0 data_cnt = 0data_cnt <= 6'd0;else data_cnt <= data_cnt + 1'b1;

end//---------------得到一个1us的高脉冲信号state----------------//

always @(posedge clk or negedge rstn) beginif (!rstn) begindata_cnt_clr <= 1'b0; endelse if(trig == 1 && data_cnt == 6'd0)begindata_cnt_clr <= 1'b1; endelse if(data_cnt == 50 - 1) begindata_cnt_clr <= 1'b0;endelsebegindata_cnt_clr <= data_cnt_clr; end

endassign state = data_cnt_clr;endmodule`timescale 1ns / 1ps

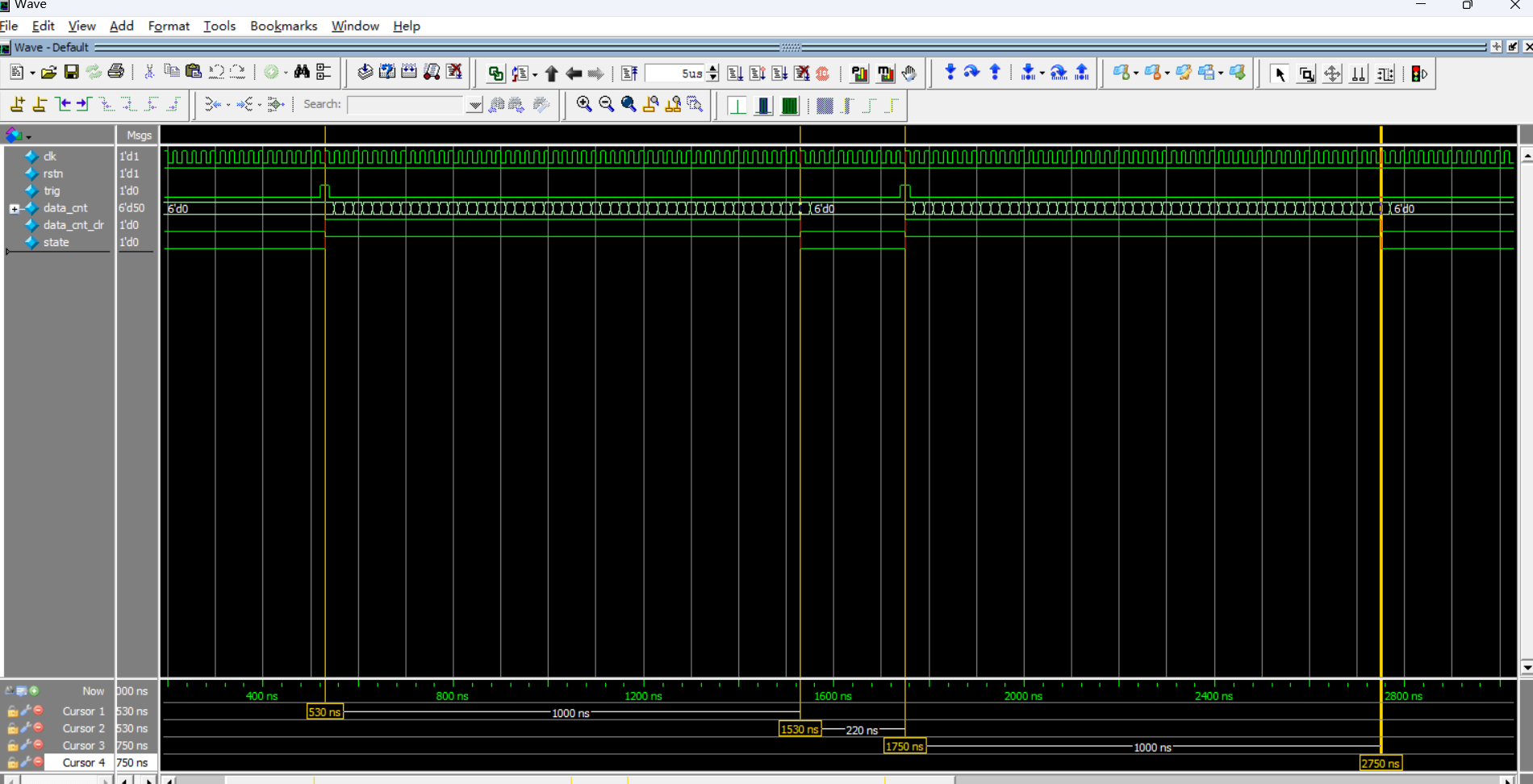

module data_cnt_tb;// Parameters// Portsreg clk ;reg rstn ;reg trig ;wire state;data_cnt data_cnt_dut (.clk (clk ),.rstn (rstn ),.trig (trig ),.state (state ));initial beginbeginclk = 0;rstn = 0;trig = 0;#20 rstn = 1;#500 trig = 1;#20 trig = 0;#1200trig = 1;#20 trig = 0;endendalways#10 clk = ! clk ;endmodule

本篇随笔为学习记录所用,如有错误,请各位指正批评。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!