数字电路之同步D触发器

由于同步RS触发器具有R端和S端是1,1的情况,不满足电路的逻辑功能,基于此,引出同步D触发器

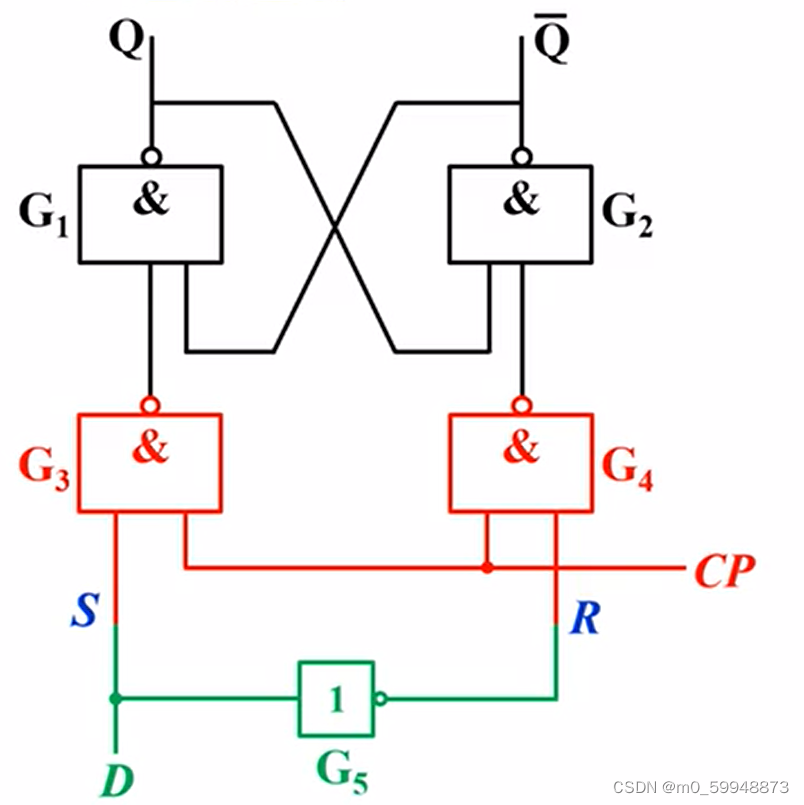

一、同步D触发器的电路组成

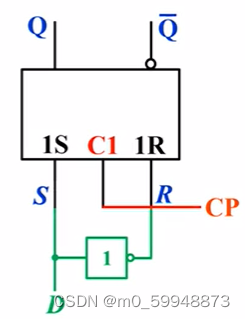

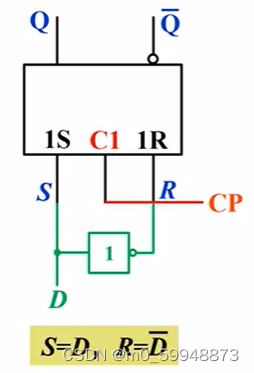

1)逻辑符号

这样的话,同步D触发器就没有约束条件

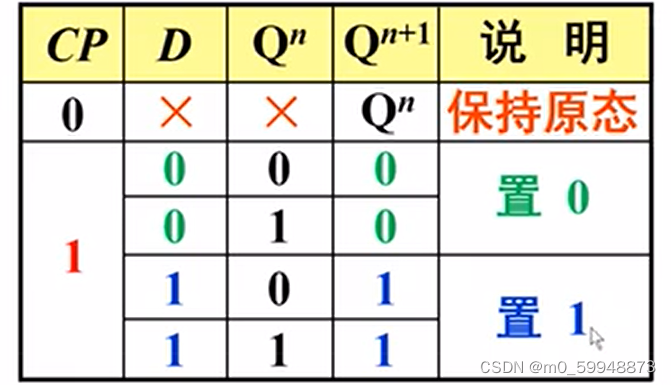

二、同步D触发器的逻辑功能

1)cp为0

当CP(时钟)为0时,触发器是不受D端输入信号控制的。保持原状态不变(对于这里不理解的,可以看篇同步SR电路数字电路之RS触发器(与非门)_m0_59948873的博客-CSDN博客)

2)cp为1

当CP(时钟)为1时,触发器可接受D端输入信号控制的,其状态翻转到和D状态相同。

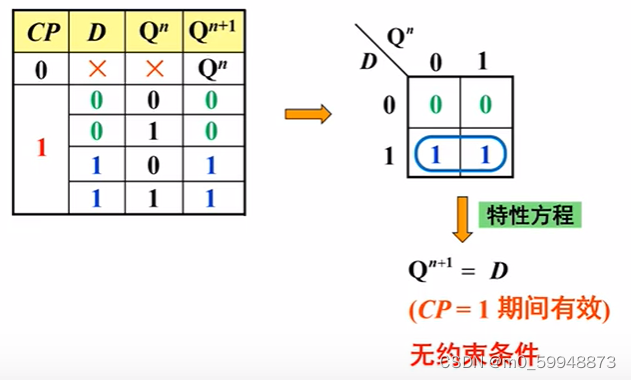

三、特性表和特性方程

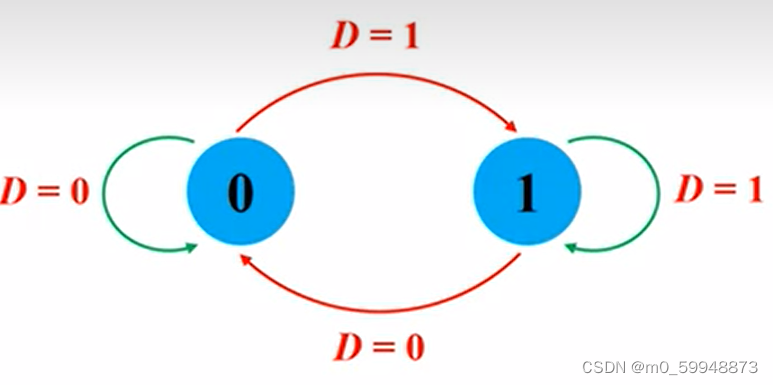

四、状态转移图

由特性表可知,由0状态转到1状态,D=1;由1状态转到0状态,D=0;

0状态保持,D=0; 1状态保持,D=1;

五、同步触发器的特点

1、时钟电平控制,输入无约束问题,忧郁同步RS触发器

2、CP=1时跟随,下降沿到来时锁存

3、存在空翻现象,即输出Q随着输入D的快速翻转而翻转,限制了同步触发器的使用

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!