verilog实现分频(奇数分频和偶数分频,通用版)

大家好,最近写了一些分频器的设计,发现奇数分频和偶数分频是比较常用分频效果,所以写了一个比较简单的分频代码,适用于奇数分频和偶数分频(不考虑占空比),代码已经经过测试,需要可自取。

一、上代码

`timescale 1ns / 1psmodule CLK_DIV_ODDandEVEN

#(

parameter Multiple = 6 //Multiple表示的是倍频倍数。

)

(

input sys_rst,

input sys_clk,

output clk_div ,

output [15:0] cnt

);reg [15:0] cnt=16'b0;

always@(posedge sys_clk)

beginif(sys_rst) //复位信号,高有效begincnt <= 16'b0; endelseif(cnt == (Multiple -1))begincnt <=16'b0; endelsebegincnt <= cnt + 1'b1 ; end

endreg clk_div=1'b0;

always@(posedge sys_clk)

beginif(sys_rst) //复位信号,高有效begin clk_div <= 1'b0;endelseif(cnt <= (Multiple /2 ))begin clk_div <= 1'b0 ; endelsebegin clk_div <= 1'b1 ; end

endendmodule

二、上验证代码

`timescale 1ns / 1psmodule CLK_DIV_ODDandEVEN_TB;// Inputsreg sys_rst;reg sys_clk;// Outputswire clk_div;wire [15:0] cnt;// Instantiate the Unit Under Test (UUT)CLK_DIV_ODDandEVEN uut (.sys_rst(sys_rst), .sys_clk(sys_clk), .clk_div(clk_div), .cnt(cnt));initial begin// Initialize Inputssys_rst = 1;sys_clk = 0;// Wait 100 ns for global reset to finish#100;sys_rst = 0;forever #500 sys_clk=~sys_clk;// Add stimulus hereendendmodule三、上仿真结果

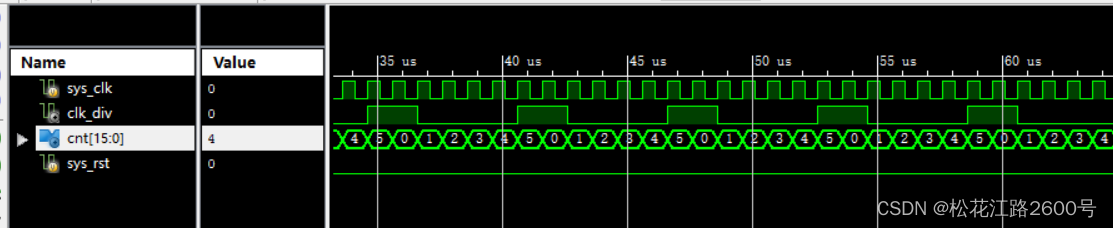

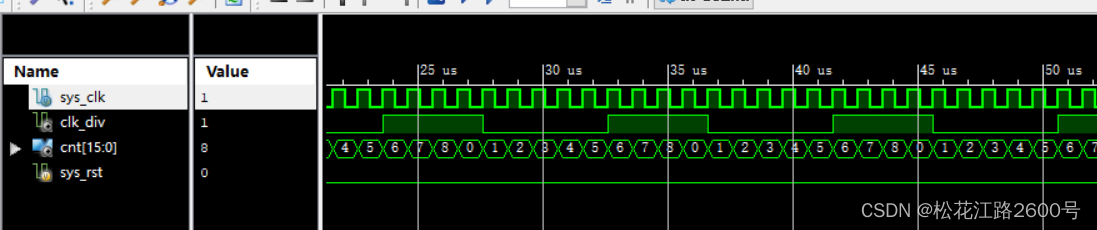

由图1和图2可知,通过改变代码中参量multiple可实现任意倍数分频效果。multiple表示分频倍数。

下面对代码和仿真结果进行说明:

①sys_clk是系统时钟,本代码中作为被分频时钟。

②clk_div是分频后时钟。

③cnt是计数器,作为分频计数使用。

④sys_rst是复位信号,高有效。

感谢关注!

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!