从头开始学51单片机之5:中断系统

5.1 中断系统概述

- 中断技术是MCU实现实时处理和控制的关键技术,可以极大提高MCU工作效率和处理问题的灵活性。MCU的中断系统包含其实现中断功能的各种软硬件总称。

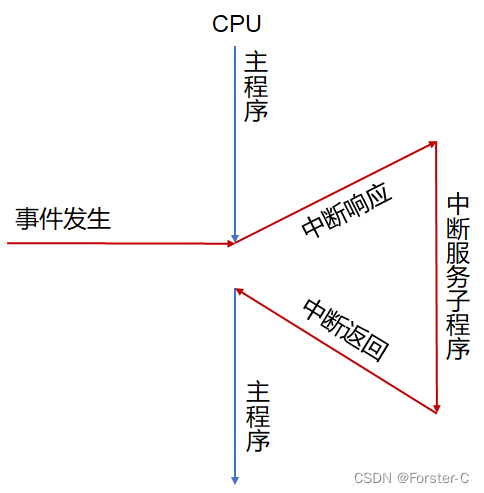

- 中断的概念:CPU执行程序时,MCU外部或内部发生某一事件,CPU暂时中止当前的工作,转到中断服务程序处理所发生的事件;处理完该事件后,CPU再回到原来被中止的地方,继续原来的工作。这个过程称为中断,CPU处理事件的过程,称为CPU的中断响应过程。

- 中断源:向CPU发出中断请求的来源

- 中断请求:中断源提出的服务请求

- 主程序:原来正在运行的程序

- 断点:主程序被断开的位置(本质上是地址值)

- 中断源分类:内部中断源和外部中断源

- MCU中断处理步骤:中断请求 -> 中断响应 -> 中断处理 -> 中断返回

5.2 51系列单片机的中断系统

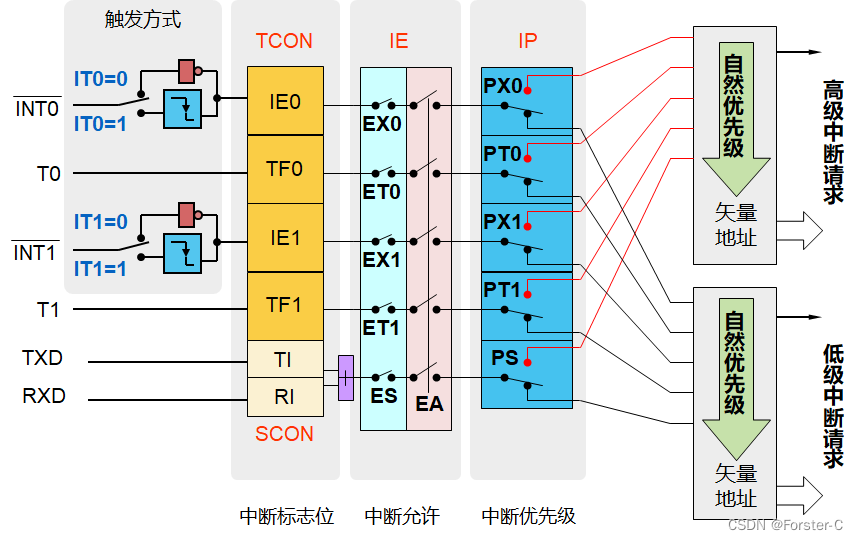

1. 51系列单片机中断系统结构

- 以AT89S51为例,可以提供5个中断源(AT89S52有6个中断源),具有2个中断优先级

- 有4个用于中断控制的寄存器:IE、IP、TCON、SCON

2. 51系列单片机中断源

| 1 | 外部中断源0请求,P3.2引脚 | IE0 | 有两种信号触发方式:电平触发和边沿触发 | |

| 2 | 外部中断源1请求,P3.3引脚 | IE1 | ||

| 3 | T0 | 定时器/计数器T0溢出中断 | TF0 | 内部中断 |

| 4 | T1 | 定时器/计数器T1溢出中断 | TF1 | |

| 5 | TX/RX | 串口中断请求 | TI/RI | 串口接收中断标志RI 串口发送中断标志TI |

3. 51系列单片机中断寄存器

| TCON | ||||||||

| 位地址 | 8FH | 8EH | 8DH | 8CH | 8BH | 8AH | 89H | 88H |

| TCON (88H) | TF1 | TF0 | IE1 | IT1 | IE0 | IT0 | ||

| IT0 | 外部中断0的触发方式选择位,可由软件置”1“或清”0“ 0:电平触发方式,低电平有效。CPU响应中断后不能硬件或软件使IE0清零,因此中断返回前必须撤销引脚上的低电平,否则将再次引起中断,导致出错 1:边沿触发方式,负跳变有效。CPU响应中断后硬件自动使IE0清零。要求外部输入的高电平或低电平的持续时间必须大于12个时钟周期,才能保证检测到先高后低的负跳变 | |||||||

| IE0 | 外部中断请求0的中断请求标志位 0:无中断请求 1:有中断请求,当CPU响应该中断时,则程序转向中断服务程序 | |||||||

| IT1 | 外部中断1的请求方式选择位,定义与IT0类似 | |||||||

| IE1 | 外部中断请求1的中断请求标志位,定义与IE0类似 | |||||||

| TF0 | T0溢出中断请求标志位,T0可对内部时钟信号或从外部输入(P3.4)的脉冲进行计数。当计数器溢出时,即表明定时时间已到或计数值已满,这时由硬件将TF0置”1“,并向CPU发出中断请求,CPU响应TF0中断时,硬件自动将TF0清”0“,TF0也可由软件清”0“ | |||||||

| TF1 | T1的溢出中断请求标志位,功能与TF0类似 | |||||||

| SCON | ||||||||

| 位地址 | 9FH | 9EH | 9DH | 9CH | 9BH | 9AH | 99H | 98H |

| SCON (98H) | TI | RI | ||||||

| RI | 串行口接收中断请求标志位。当串行口接受完一帧数据后,RI由硬件自动置1,向CPU申请中断。转向中断服务程序后,RI必须用软件清零 | |||||||

| TI | 串行口接收中断请求标志位。当串行口接受完一帧数据后,RI由硬件自动置1,向CPU申请中断。转向中断服务程序后,RI必须用软件清零 | |||||||

| IE | ||||||||||

| 位地址 | AFH | AEH | ADH | ACH | ABH | AAH | A9H | A8H | ||

| IE (A8H) | EA | ES | ET1 | EX1 | ET0 | EX0 | ||||

| EA | 中断允许总控制位。当EA=0时,CPU禁止所有的中断请求;当EA=1时,CPU开放中断。此时每个中断源的中断是否允许,还取决于各中断源的中断允许控制位的状态 | |||||||||

| EX0 | 外部中断0中断允许位。若EX0=1,则允许外部中断0中断;否则,禁止其中断 | |||||||||

| ET0 | 定时器/计数器T0的溢出中断允许位。若ET0=1,则允许定时器/计数器T0溢出时提出的中断请求;否则,禁止其中断 | |||||||||

| EX1 | 外部中断1中断允许位 | |||||||||

| ET1 | 定时器/计数器T1的溢出中断允许位 | |||||||||

| ES | 串行口中断允许位 | |||||||||

| IP | ||||||||

| 位地址 | BFH | BEH | BDH | BCH | BBH | BAH | B9H | B8H |

| IP (B8H) | PS | PT1 | PX1 | PT0 | PX0 | |||

| PX0 | 外部中断0的中断优先级控制位。若PX0=1,则外部中断0为高中断优先级;否则,为低中断优先级 | |||||||

| PT0 | 定时器/计数器T0中断优先级控制位 | |||||||

| PX1 | 外部中断1的中断优先级控制位 | |||||||

| PT1 | 定时器/计数器T1中断优先级控制位 | |||||||

| PS | 串行口中断优先级控制位 | |||||||

- 51系列单片机复位后IP被清零,所有中断源均设定为低优先级

- 当同一优先级的中断源同时向CPU请求中断时,CPU按照自然优先级依次响应

- 基本原则:低优先级不看了一打断高优先级;高优先级可以打断低优先级,实现中断嵌套;同级中断由自然优先级决定最终嵌套顺序

5.3 中断处理过程

1. 中断响应

- 中断响应的条件:中断源有请求 + CPU总中断允许开放(EA=1) + 中断允许寄存器IE相应位为1;无高级中断服务程序在执行中 + 现行指令执行到最后1个机器周期且已结束 + 若现行指令为RETI或需访问SFR中IE或IP的指令时,执行完该指令且紧随其后的另1条指令也已执行完

- 中断响应的过程:1)保护断点,执行一条由中断系统提供的硬件LCALL指令把被中断程序的断点压入堆栈;2)将程序转向中断服务程序的入口位置,相应的中断服务程序的入口地址装入PC

2. 中断处理

- 保护现场:先将在中断服务程序中要使用的累加器A、PSW、工作寄存器等内容压入堆栈

- 中断服务:完成具体任务

- 恢复现场:将原来压入堆栈的工作寄存器、PSW、累加器A等内容弹回

3. 中断返回

- 中断服务完成后,MCU返回断点位置,继续执行原来的程序

- 汇编指令中,由专门的指令RETI实现

4. 中断请求撤销

- 中断响应后,TCON和SCON中的中断请求标志位需要及时清除,否则会造成中断混乱

| 定时中断 | 定时中断响应后,硬件自动把中断标志位(TF0、TF1、TF2)清零,是自动撤除 |

| 外部中断 | 1)边沿触发:硬件自动清零 2)电平触发:在中断响应后把中断请求输入端从低电平强制改为高电平,需配合硬件电路和软件代码实现 |

| 串行口 | TI和RI不会自动清零,需用软件方法清除 |

5. 中断响应时间

-

从查询中断请求标志位到转向中断区入口地址所需的机器周期数

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!