关于STM32·GPIO位结构电路的解读

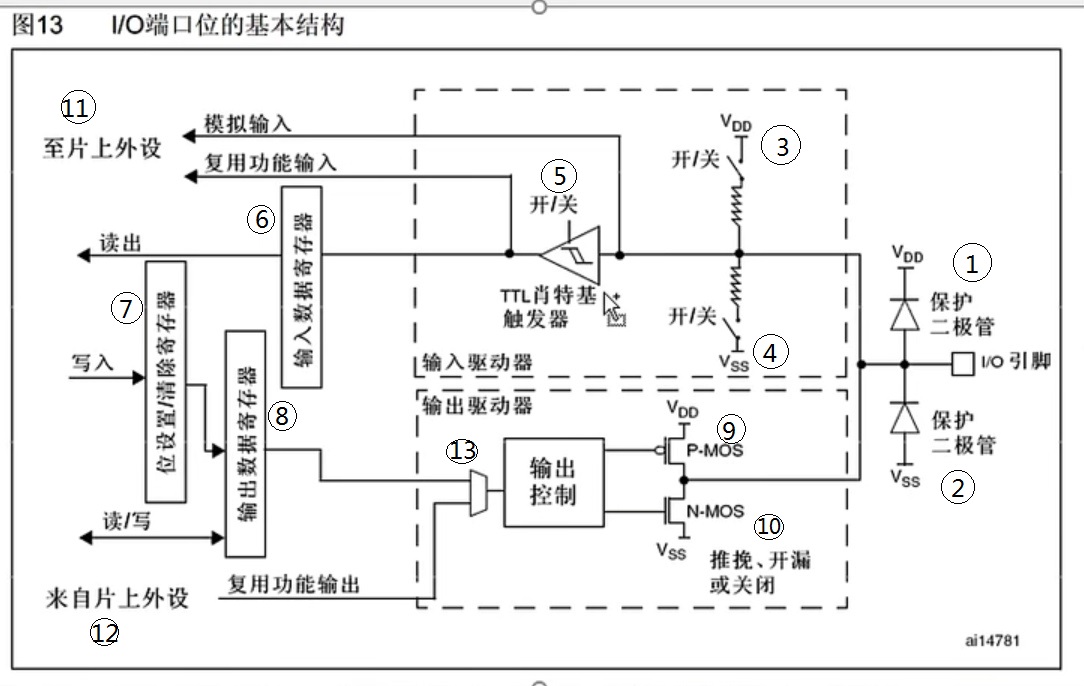

如图为GPIO的结构电路图:

上一篇文章已经对STM32F103的GPIO作了基础的介绍,讲到了其基本结构,可配置的8种输入输出模式,引脚电平等。这篇文章呢,我将继续对GPIO位结构电路图进行解读。

编号模块或元件名称

保护二极管(接VDD);

保护二极管(接VSS);

上拉电阻(接VDD);

下拉电阻(接VSS);

施密特触发器;

输入数据寄存器;

位设置/清除寄存器;

输出数据寄存器;

P-MOS(接VDD);

N-MOS(接VSS);

连接到片上外设的输入线路;

连接到片上外设的输出线路;

数据选择器;

注:后文在引用上述名称时将以编号代替!

保护二极管1,2

这两个二极管是对输入电压进行限幅的,其中1接VDD,3.3V;2接VSS,0V.

若输入电压>3.3V,则1导通,输入电压产生的电流直接进入VDD,从而避免电压过高而伤害内部电路。

若输入电压<0V(这里的电压是相对于VSS的,所以存在负压),则2导通,电流直接从VSS流出去,而不从内部电路汲取电流,也可以保护内部电路。

若输入电压在(0V , 3.3V) 内,则1,2都不导通。

上拉电阻和下拉电阻

3接VDD,4接VSS,开关可通过程序进行配置,接通哪个就为哪种输出模式。无论是上拉输入模式还是下拉输入模式都是为了输入提供一个默认的输入电平,因为对应一个数字的端口,输入只有两种:高电平和低电平。

若输入引脚不接,即两个开关都断开,则为浮空输入模式。此时输入引脚处于浮空状态,引脚的输入电平极易受外界干扰而改变,从而导致输入数据不稳定。所以在使用浮空输入时,端口要连接一个连续的驱动源,不能出现悬空的状态。

若接入3,则当引脚悬空时,还有3来保证引脚的高电平。上拉输入:默认为高电平的输入模式。

若接入4,同理。

注:3,4的阻值都较大,是弱上拉和弱上拉,其目的是尽量不影响正常的输入操作。

施密特触发器(上篇文章已述其作用于执行逻辑,此仅作补充)

经过施密特触发器整形的波形就可以直接写入6,再用程序读取6中对应某一位的数据即可知道端口的输入电平。

连接到片上外设的输入线路

这两个线路连接至片上外设的端口,其中模拟输入连接在ADC上,因为ADC需要接收模拟量,完成数模转换,所以这条线路在5之前;复用功能输入连接在其他需要读取端口的外设上,例:串口的输入引脚,因为此线路接收数字量,所以接在5之后。

位设置/清除寄存器

可用来单独操作8中某一位,而不影响其他位。

因为8同时控制16个端口,并且只能整体读写,所以若想单独控制某一个端口而不影响其他端口有以下三种方法:

先读出8,然后用按位与和按位或的方式更改一位,最后将更改后的数据写回去,(在C语言中体现为&=和|=)这种方法麻烦且效率不高,对IO口的 操作不太适用。

通过设置7,例:如果要对某一位进行置1的操作,在位设置寄存器的对应位写1即可,其余位写0即可,其内部电路会自动将8中对应位置为1,而写0的位则不变。同理,通过在位清除寄存器中对应位写1就可以完成清0操作。

(补充)读写STM32中“位带”区域;在STM32中,专门分配的有一段地址区域,这段地址映射了RAM和外设寄存器所有的位,读写这段地址中的数据,相当于读写了所映射位置的某一位。

输出数据寄存器,连接到片上外设的输出线路

这两个部分控制输出部分,两种方式通过13接到了输出控制部分。

若选择8进行控制,即为普通IO口输出,改写8的某一位就可以操作对应的某一端口。

复用功能输出:与开漏,推挽输出相似,不同之处在于复用的输出引脚电平由片上外设控制,在此模式中,8和13之间是断开的。

P-MOS,N-MOS

MOS管就是一种电子开关,用信号控制开关的导通和断开,而开关则负责将IO口接到VDD或VSS,在此处可以选择推挽,开漏和关闭三种输出模式。

在推挽输出模式下,9,10都有效,8为1时,9导通,10断开,输出接到VDD,输出高电平;8为0时,9断开,10导通,输出接到VSS,输出低电平;此模式下高低电平均有较强驱动能力,也叫“强推输出模式”。在此模式下,STM32对IO口具有绝对控制权。

在开漏输出模式下,9无效,10工作,8为1时,10断开,此时输出相当于断开,为高阻模式;8为0时,10导通,输出接到VSS,也就是输出低电平,所以此模式下只有低电平有驱动能力,高电平则无。所以开漏模式可以作为通信协议的驱动方式,例:I2C通信的引脚,在多机通讯的情况下,此模式可避免各个设备的相互干扰;可用于输出5V的电平信号,例:在IO口接上拉电阻到5V的电源(在输出低电平时,10接VSS;输出高电平时,由外部的上拉电阻拉高至5V,用于兼容5V电平的设备。)

在关闭模式下(引脚配置为输入模式时),9,10均无效,输出关闭,端口电平由外部信号来控制。

注:1.在8种可配置输入输出模式中,只有模拟输入会关闭数字的输入功能

2.对至多有一个输出但可有多个输入的解释:因为在输入模式下,输出驱动器是断开的,端口只能输入;而在输出模式下,输入驱动器正常运作,可以存在输入

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!