基于FPGA的简易示波器、频谱仪

基于FPGA的简易示波器、频谱仪

工程文件下载:基于FPGA的简易示波器、频谱仪

主要功能包括:

(1)可以采集四个通道的输入信号。如果信号是周期的,可以对信号进行同步,可调整触发电平和触发方式(上升沿,下降沿,瞬态触发);

(2)调整信号坐标轴位置,对信号进行上下左右平移,时间轴缩放,纵轴缩放,对频谱进行幅度缩放;

(3)能够显示英文和数字,计算并显示信号的频率,周期,峰峰值,平均值,坐标轴刻度;

(4)显示信号的频谱幅度,可以设定一个频谱阈值,进行检峰,在侧边栏显示所选谱峰的具体频率;

(5)内部可以产生正弦、方波、三角波信号,可调整频率,供调试使用;

(6)使用4*4行列按键进行控制,6位数码管显示采样频率,单位Hz,如果数值大于数码管位数,则以科学计数法表示,如50E6表示采样频率为50MHz。

采用的是学校提供的Xilinx Basys3开发板,芯片是Xilinx xc7a35tftg256,Verilog语言,平台是Vivado 2017.4。

IP核:

使用的Basys自带的ADC模块,调用XADC IP核进行控制。另外还调用了FFT IP核、块存储生成器(Block Memory Generator)IP核、Clock Wizard IP核、除法器(divider)IP核。均包含在工程文件中。

块内存初始化文件:

一共三个初始化文件:正弦函数表(8位二进制数保存,所以宽度8 bit,深度64)、4*4按键功能的说明图(图片是108*108的一位黑白图片,深度11664,宽度1 bit)、字符的字模数据(字模尺寸8*16,共64个字符,深度512,宽度16 bit)。三个coe文件均包含在工程文件中。

操作说明:

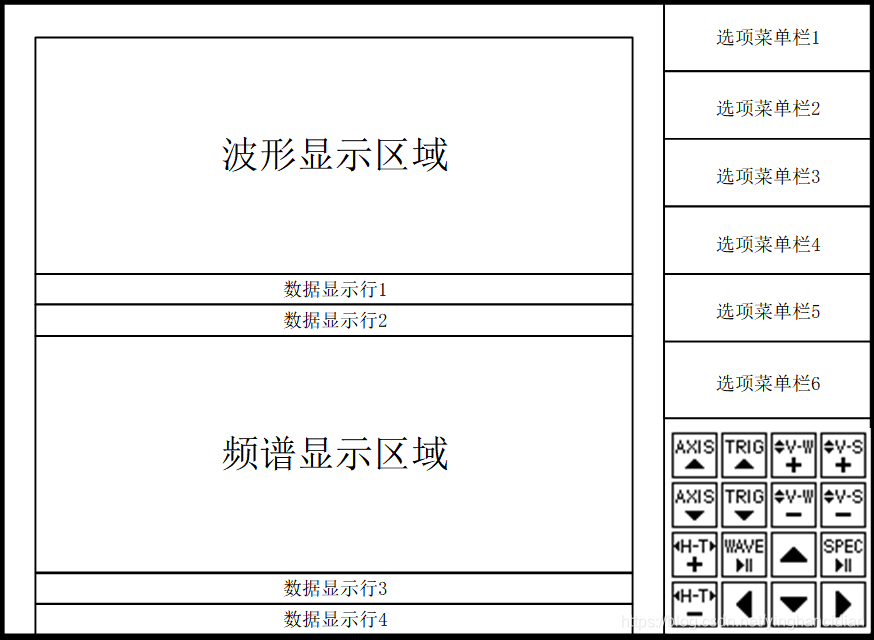

工程使用VGA输出,分辨率640*480,显示界面设计如下:

屏幕上方显示波形,数据显示行显示波形信息(水平垂直分划,信号周期,频率,峰峰值,平均值);下方显示频谱,数据显示行显示频谱信息(水平频率分划,带宽,频谱分辨率)。

侧边上方有6栏,分别是输入通道选择(4个输入通道和内部信号),内部信号频率,触发模式(上升沿,下降沿,瞬态触发),触发位置(左中右),频谱检峰输出,频谱检峰阈值调整。

右下方是4*4按键的功能示意图。

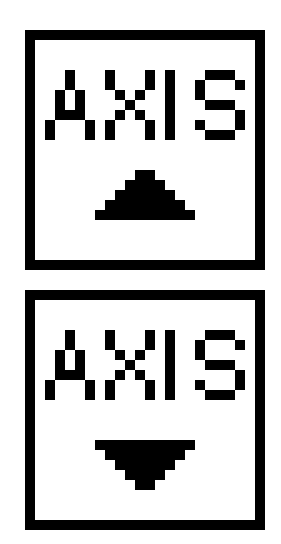

调整坐标轴位置: 上下调整波形界面的横坐标位置,在屏幕左侧以箭头标示。

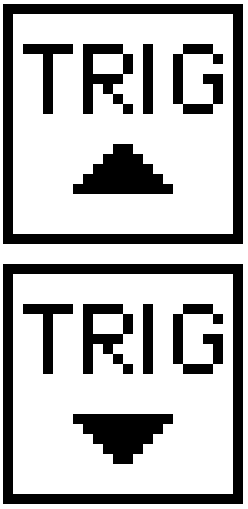

调整触发电平位置: 上下调整波形界面的触发电平高度,在屏幕以箭头表示。

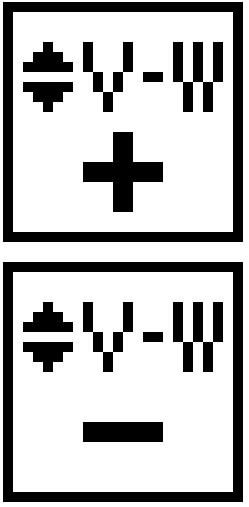

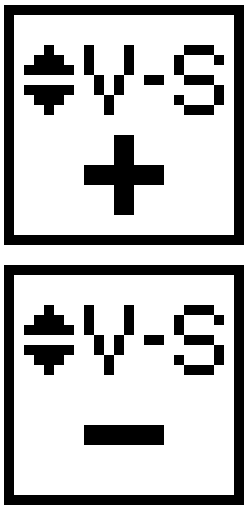

波形幅度缩放: 调整信号波形的纵向缩放尺度。

频谱幅度缩放: 调整频谱的纵向缩放尺度。

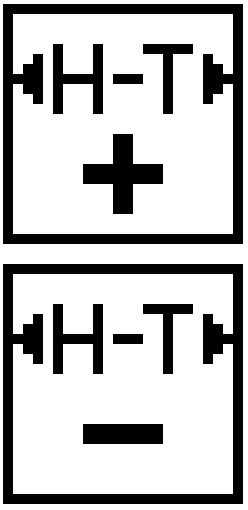

水平时基缩放: 调整水平方向的时间尺度。

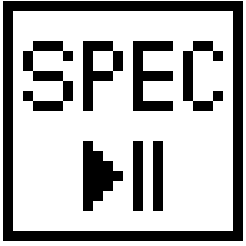

暂停波形刷新:

暂停频谱刷新:

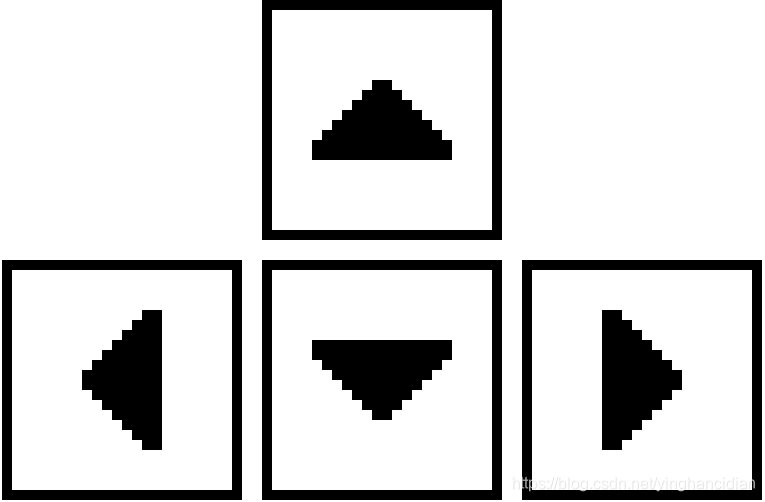

方向键:调整侧边栏的选项 上下选择栏目,左右调整选项

结果展示:

内部正弦波信号3.125 kHz:

内部正弦波信号15.625 kHz:

内部方波信号3.125 kHz:

如果要移植,更改约束文件即可

这个工程是本科毕设作品,能力有限,还有很多错误和不足之处。以后有时间我会介绍一些主要的模块。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!