数字系统设计实验五:verilog的延时仿真

1.问题描述:

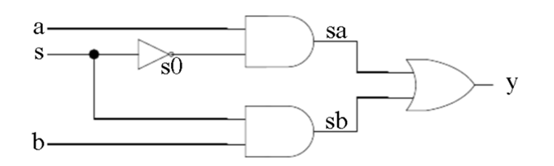

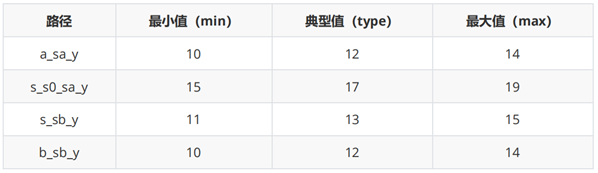

如下图所示电路,若其延迟时间设定如表所示,试写Verilog HDL程序设计该电路。

2.问题分析:

本题希望进行的是基于门延时的verilog仿真,在代码中定义的延时是无法通过综合编译为实际电路的,即无法综合,但实际的电路中总是会存在延时,这对我们进行仿真后,门级网表的功能能否正常实现存在着一定的影响,因此,在仿真中加入延时信息,可以帮助我们使仿真更接近实际电路。

在这题中,我们可以通过specify块来定义从a,b,c到y分别的延时,但是,s->y有两个通路,即有两个延时,在specify中无法实现两条通路的延时。针对这个问题,可以将s分为s和s0两个输入,由数据比较可知,s经过的反相器的延时为4(固定值),只用通过固定的反相器延时将s转变为~s即可。

延时的数据分为最小值,典型值,最大值,这个数据是工艺、温度、电源电压波动等因素引起的,在代码中,这三种延时可以用冒号间隔的方式表示。

3.代码:

由于specify语句中的参数必须是输入输出端口,所以需要用两个模块来描述,delay模块描述了specify端口延时,用delay_test模块将其例化。

主模块和例化模块:

`timescale 1ns / 1ps

//

// Company:

// Engineer: jeffery

module delay_test(a,b,s,y);

input a,b,s;

output y;

wire s0;

not #4 not1(s0,s);//定义not反相器延时为4delay my_delay(.a(a),.b(b),.s(s),.s0(s0),.y(y));endmodulemodule delay(a,b,s0,s,y);input a,b,s,s0;

output y;

wire sa,sb;

//首先进行组合逻辑模块的逻辑定义and and0(sa,a,s0),and1(sb,b,s);

or or1(y,sa,sb);//然后进行延时的定义specify(a=>y)=(10:12:14);(s=>y)=(11:13:15);(b=>y)=(10:12:14);endspecifyendmoduleTb文件:

`timescale 1ns / 1ps

//

// Company:

// Engineer: jeffery

//

module tb();

reg a,b,s;//需要在下面的过程语句中进行赋值

wire y;

delay_test my_delay_test(.y(y),.a(a),.b(b),.s(s));initial begin//aa=0;b=0;s=0; //初始化信号,这时y=0;#20 a=1;b=0;s=0; //a变,y上升#20 a=0;b=0;s=0; //a变,y下降//b#20 a=0;s=1;b=0;//初始化信号,这时y=0#20 a=0;s=1;b=1;//b变,y上升#20 a=0;s=1;b=0;//b变,y下降//s#20 a=0;b=1;s=0;//初始化信号,这时y=0#20 a=0;b=1;s=1;//s变,y上升#20 a=0;b=1;s=0;//s变,y下降//~s#20 a=1;b=0;s=1;//初始化信号,这时y=0#20 a=1;b=0;s=0;//s到s非变,y上升#20 a=1;b=0;s=1;//s到s非变,y下降endendmodule4.测试结果:

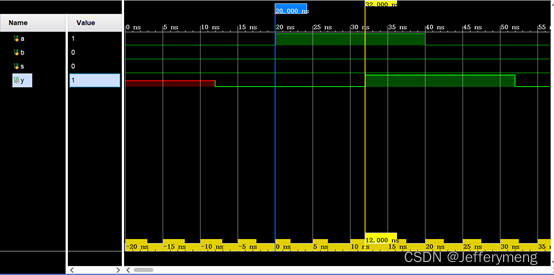

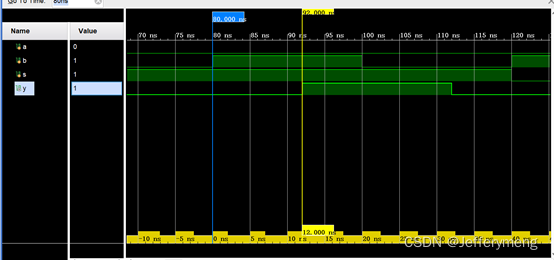

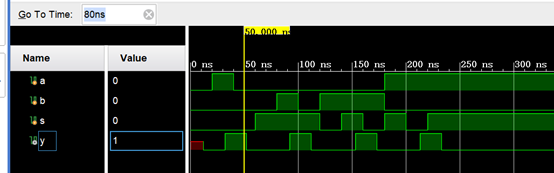

上面两张图展示了如何用waveform工具中的curse进行延时测量,最后一张图是测试信号和结果的整体波形,y的初始值没有赋予,默认为x。具体的测量图片不再多余展示。测试结果如下:

a——>y 延时为12ns;

b——>y 延时为12ns;

s——>y 延时为13ns;

s——>s0——>y延时为17ns;

可知,通过仿真得到的结果都是典型值。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!