商汤科技FPGA优化验证岗笔试(一)解析

商汤科技FPGA优化验证岗笔试(一)解析

选择题

-

.

面积优化:资源共享、寄存器配平、串行化

速度优化:流水线设计、寄存器配平、关键路径法、乒乓操作法、树形结构法 -

.

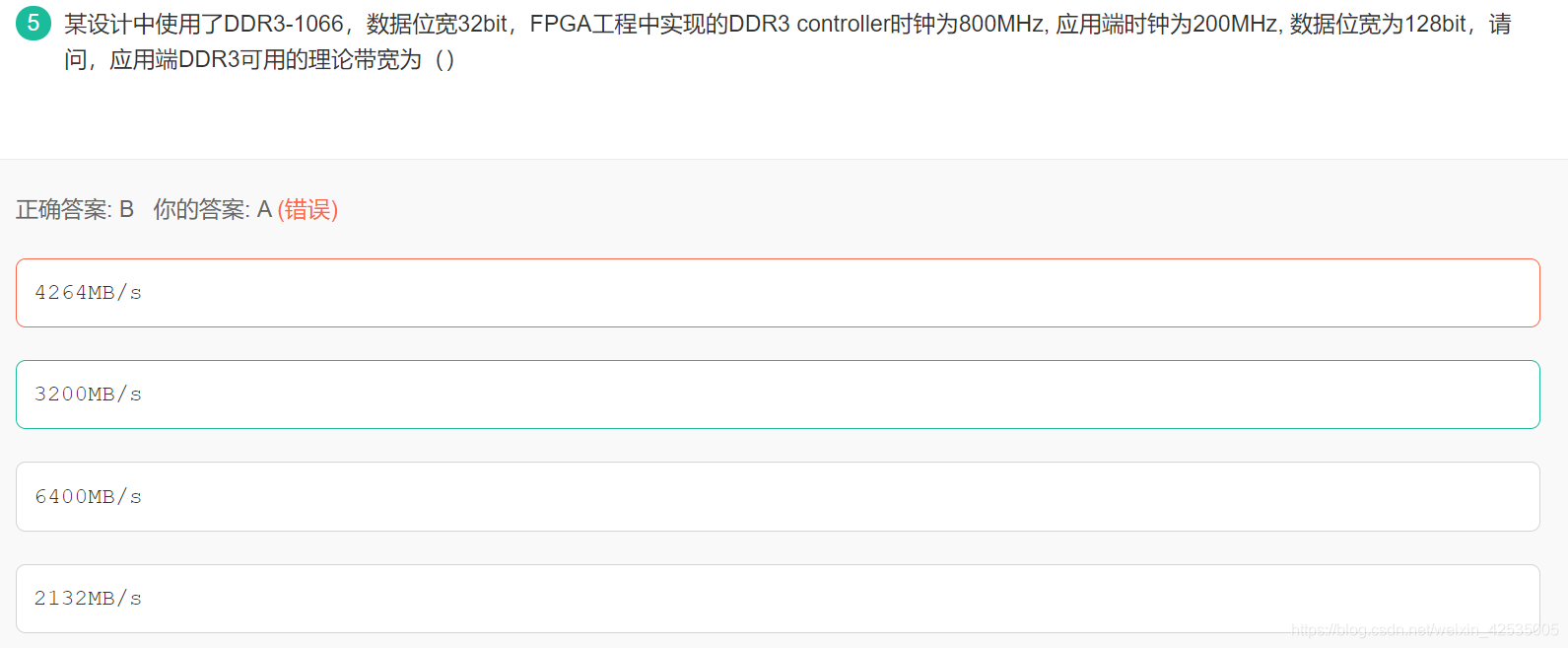

DDR3-1066 理论带宽 = 1066 * 32 / 8 = 4264

FPGA内存带宽 = 800 * 32 / 8 = 3200

应用端带宽 = 200 * 128 / 8 = 3200

取瓶颈3200

个人理解:

如果不考虑应用端的限制,DDR3-1066,数据位宽32bit,其理论物理速率为:

1066 * 32 / 8 = 4264MB/s。

由于应用端时钟为200MHz, 数据位宽为128bit,所以其速率最快为:

200 * 128 / 8 = 3200MB/s

所以选B。

问答题

1. 解释名词:建立时间,保持时间和亚稳态。

- 建立时间为在时钟沿到达寄存器之前,数据需要稳定的时间,如果不满足寄存器的建立时间,则可能会产生亚稳态;

- 保持时间为在时钟沿到达寄存器之后,数据需要稳定的时间,如果不满足寄存器的建立时间,则可能会产生亚稳态;

- 建立时间与保持时间都是器件的固有属性,需要对时钟频率、组合逻辑延时进行改变以满足建立时间,对组合逻辑演示进行改变以满足保持时间

- 亚稳态即在时钟上升沿到来时,数据不满足寄存器的建立时间或者保持时间,使寄存器采到的数据的值不确定的状态,该状态会随着后面的组合逻辑与时序电路进行传播,造成极大的危害,需要避免,避免的方法有增加寄存器。

2. 异步FIFO设计注意事项有哪些?

- ①fifo深度计算

fifo深度应大于或等于(写数据时钟频率减去读数据时钟频率)乘上(最大猝发传输数据长度除以写数据时钟频率)。 - ②判断fifo满和空

通过读写指针判断fifo的空和满。读写指针要比存储地址多一位,用于判断满。

但由于两个指针的时钟域不同,所以需要将写指针同步到读时钟域进行判断fifo是否读空,将读指针同步到写时钟域进行判断fifo是否写满。

在读写时钟频率差距不是很大时,可将读写指针转换为格雷码进行同步,因为在读写时钟频率差距不是很大时,通常的计数器加一改变的bit数过多,而格雷码只是跳变一个bit。

fifo空条件:写指针与读指针相等。

fifo满条件:在格雷码领域判断,最高位和次高位相反,其余位相等。

1.存储体的使用,对于异步FIFO存储体通常采用memory compiler 生成DPSRAM包含两套独立的时钟和读写相关的信号

2.空满标志的产生,全等为空。高位取反其他位相等为满。有的设计还学要设计almost empty/full信号,保证数据传输的可靠性。

3.指针同步 采用每次只有1bit变化的Grraycode进行跨域的传输,保证读写地址同步的安全性

异步FIFO通过比较读写地址判断满空标志,但是读写地址属于不同的时钟域,在比较前需要对读写地址进行同步处理,如将写地址同步到读时钟再与读地址进行FIFO比较,判断FIFO空状态。但多位地址重新进行同步时,一些位可能滞后其他位一个时钟周期,取决于各个引线上的传播特性。可以将地址转换为格雷码来解决,格雷码相

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!