复旦微开发过程中遇到的问题总结(二)

一,将bin文件放到flash中0地址处能识别并且启动吗?

xlinx的放在0地址处可以识别启动,我尝试复旦微这个没反应

要用procise生成,第一个必须是FSBL.out。只能是procise生成的BOOT.bin。

备注注意:

备注注意:

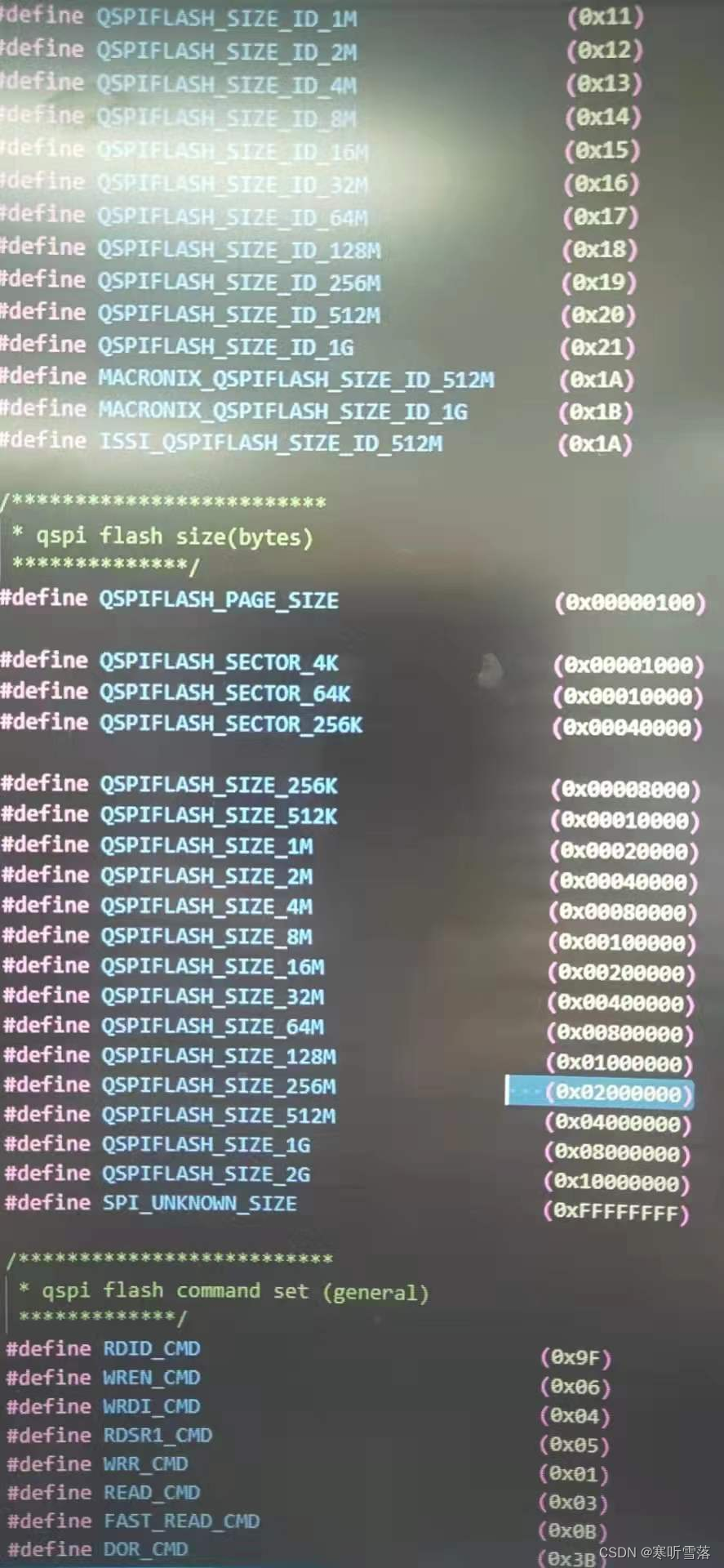

二,qspips_v1_0中,fmsh_qspips_flash.h文件中驱动文件有个256m的宏?应该对应0x10000000

答案:前面宏指的是小b,后面的值是大B

三, 用第三方软件下载的程序是放在flash中么,在哪个位置?怎么擦除都无法破坏现有程序

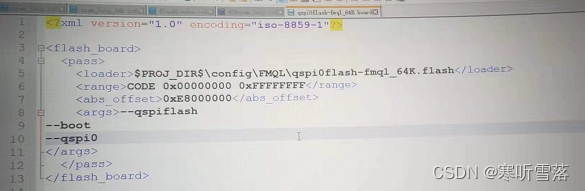

默认是flash 0地址上,看下board文件就知道烧哪了,如果能启动肯定是0地址处。

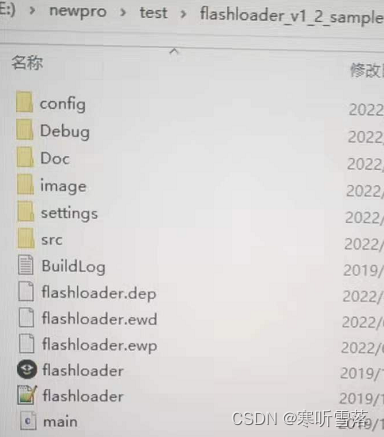

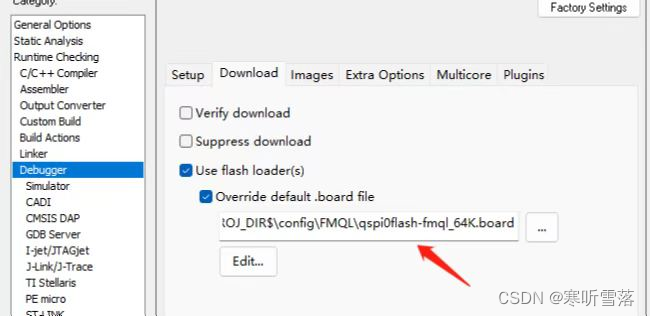

首先确保使用最新的procise版本烧写,新版本procise烧写flash很稳定了。用下面的软件烧写。

其次,把下面这个文件修改到flash 0地址

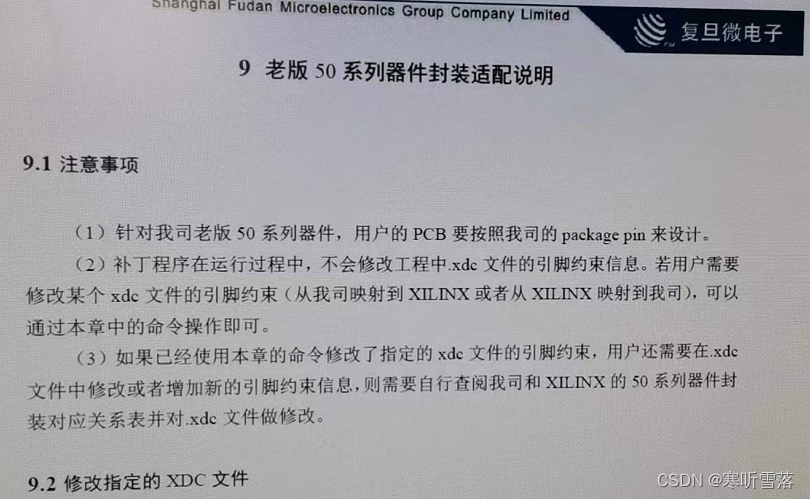

四,老版的50和新版的50系列有什么差别?这次的更新补丁说是不需要再单独对其进行引脚映射,那xdc文件就不用变了吗(不用映射成xlinx的引脚的)?以前映射后的引脚不用映射,因为我们会把器件库换成复旦微的。

注意mig的ip里面有个xdc,也要转过来,根本上就是xdc有变化。

也可以用反映射命令转回来,现在打开设计开到的io,都是复旦微的封装了。现在内侧一个版本,连exe都不用装,很快会释放出来。

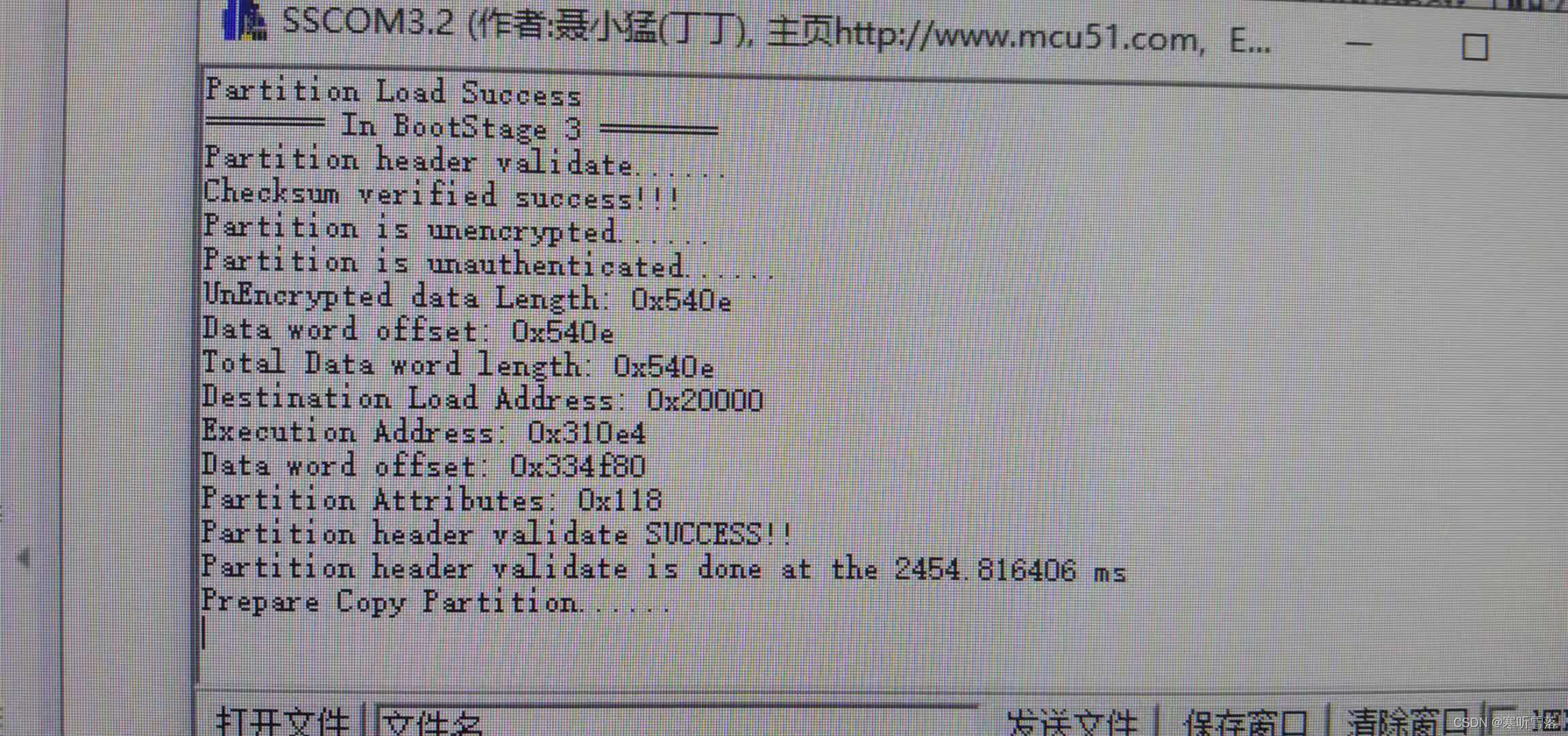

五,flash固化后报:prepare copy partition....

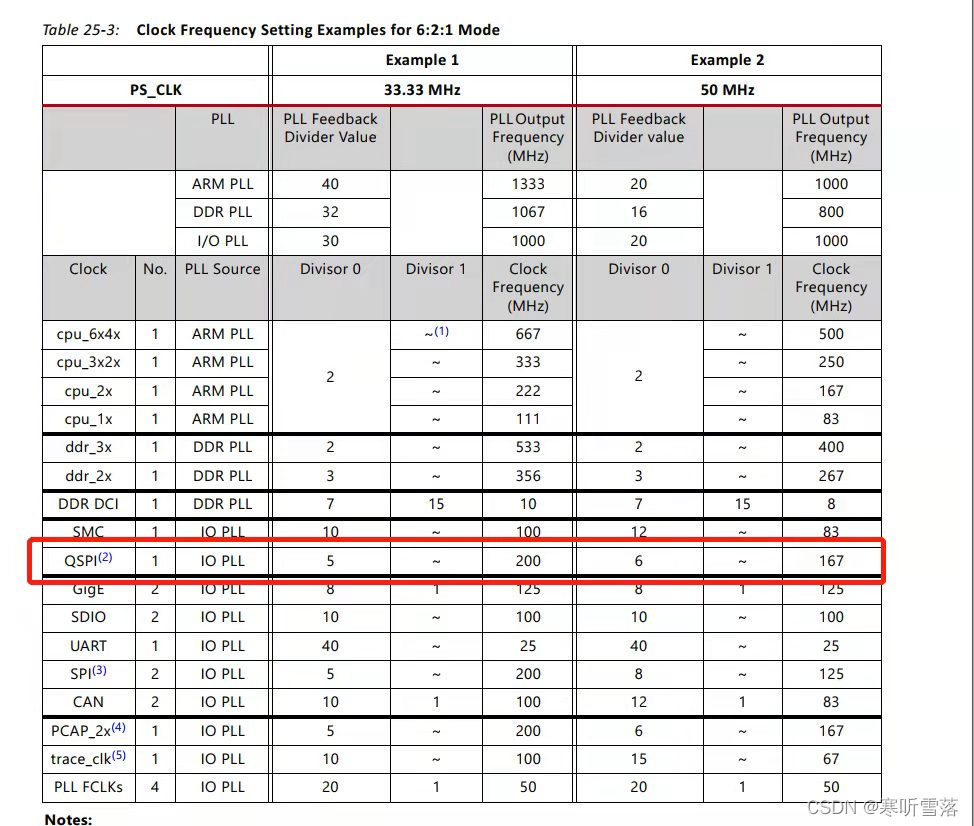

flash默认时钟是200M,修改时钟为50-100M之间,我改的120M

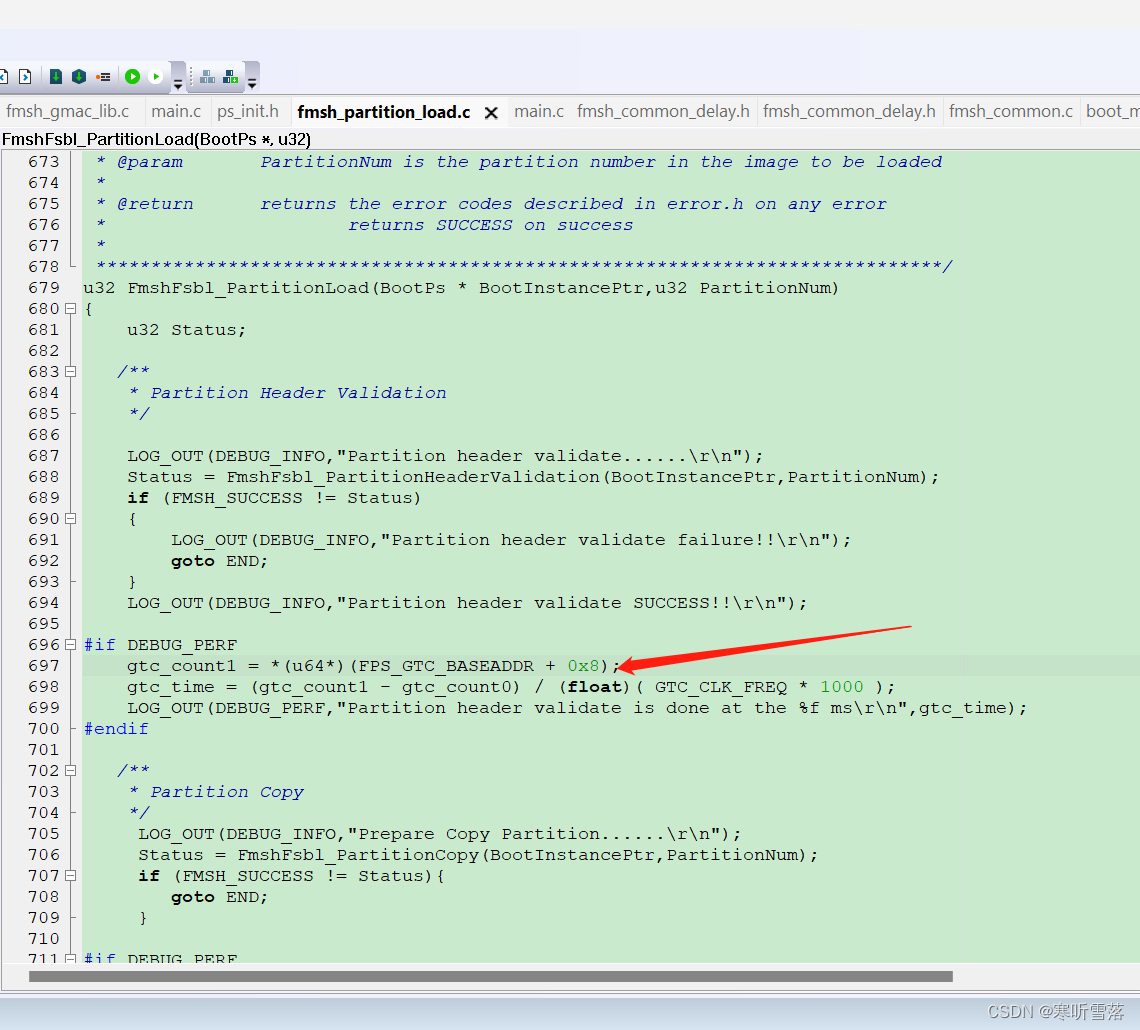

六,现象:iar ps中dma中断增加计时器,可以读取时间,计算一下代码的执行时间。zynq中使用get current函数不起作用:

六,现象:iar ps中dma中断增加计时器,可以读取时间,计算一下代码的执行时间。zynq中使用get current函数不起作用:

处理办法:zynq有一个get time函数,不受中断的影响。get_current_time是读去全局时钟计数,不受中断影响。用法参考:

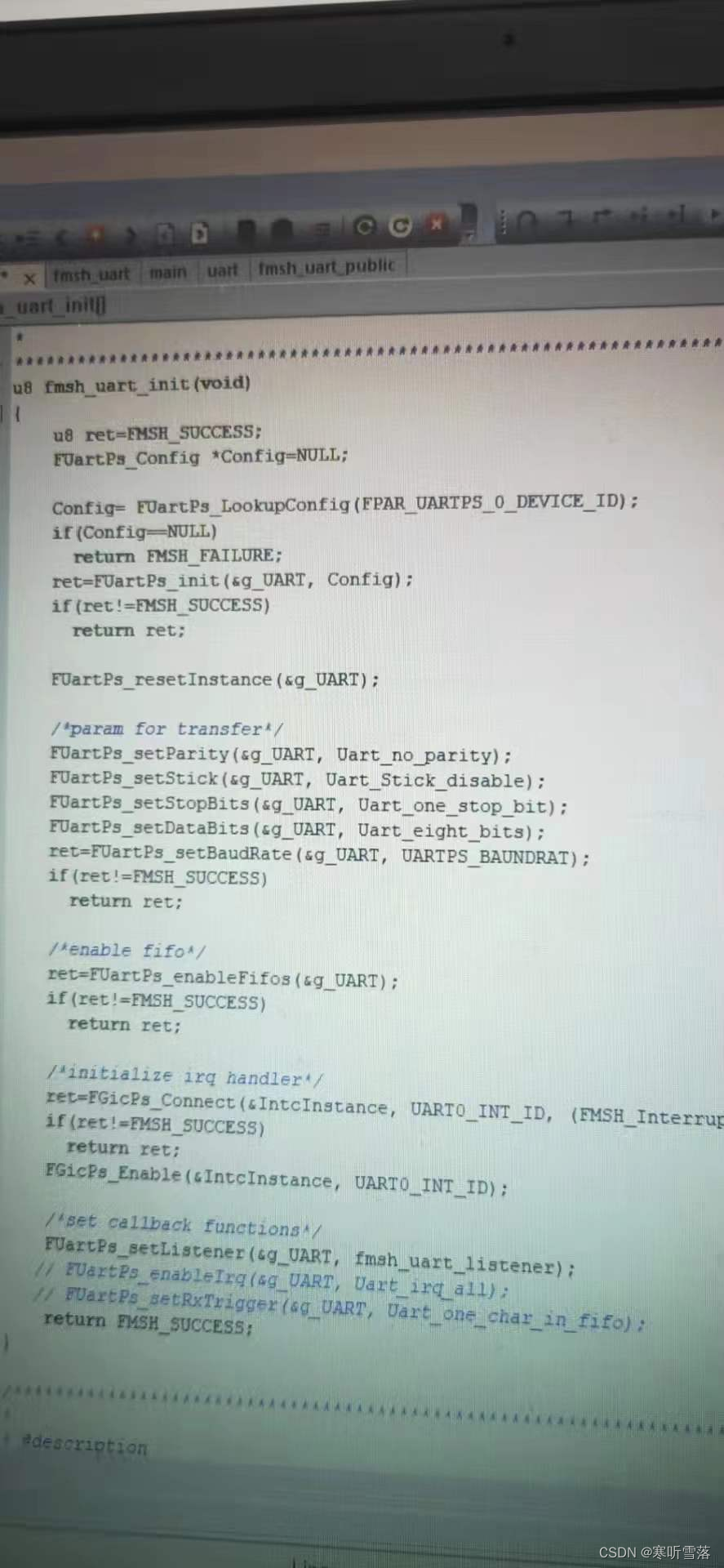

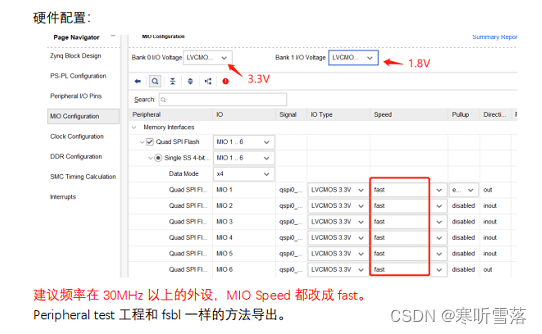

七,这个串口中断进不去是什么原因?

解决办法:参考官方例程,其次bank电压也要配置正确,PL串口电压要配置为3.3V,具体参考appn101文档。电压配置不正确的话,串口只能发送不能接收。

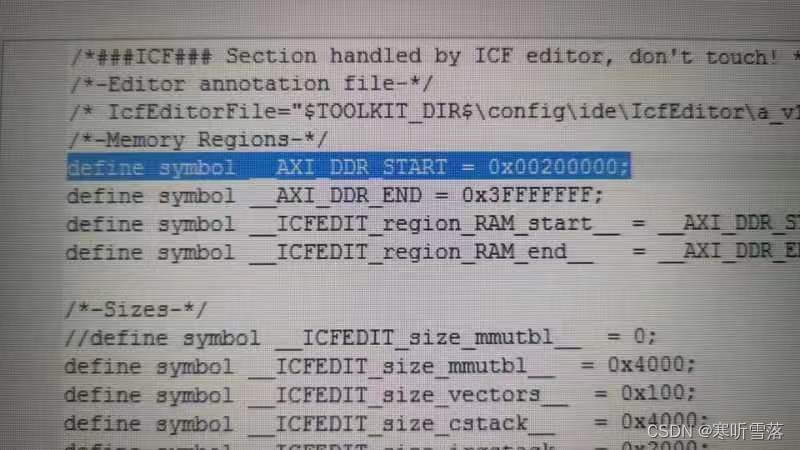

八,注意:这里前面1M是保留的,不能被应用程序使用。这一点Xilinx和复旦微差不多。

八,注意:这里前面1M是保留的,不能被应用程序使用。这一点Xilinx和复旦微差不多。

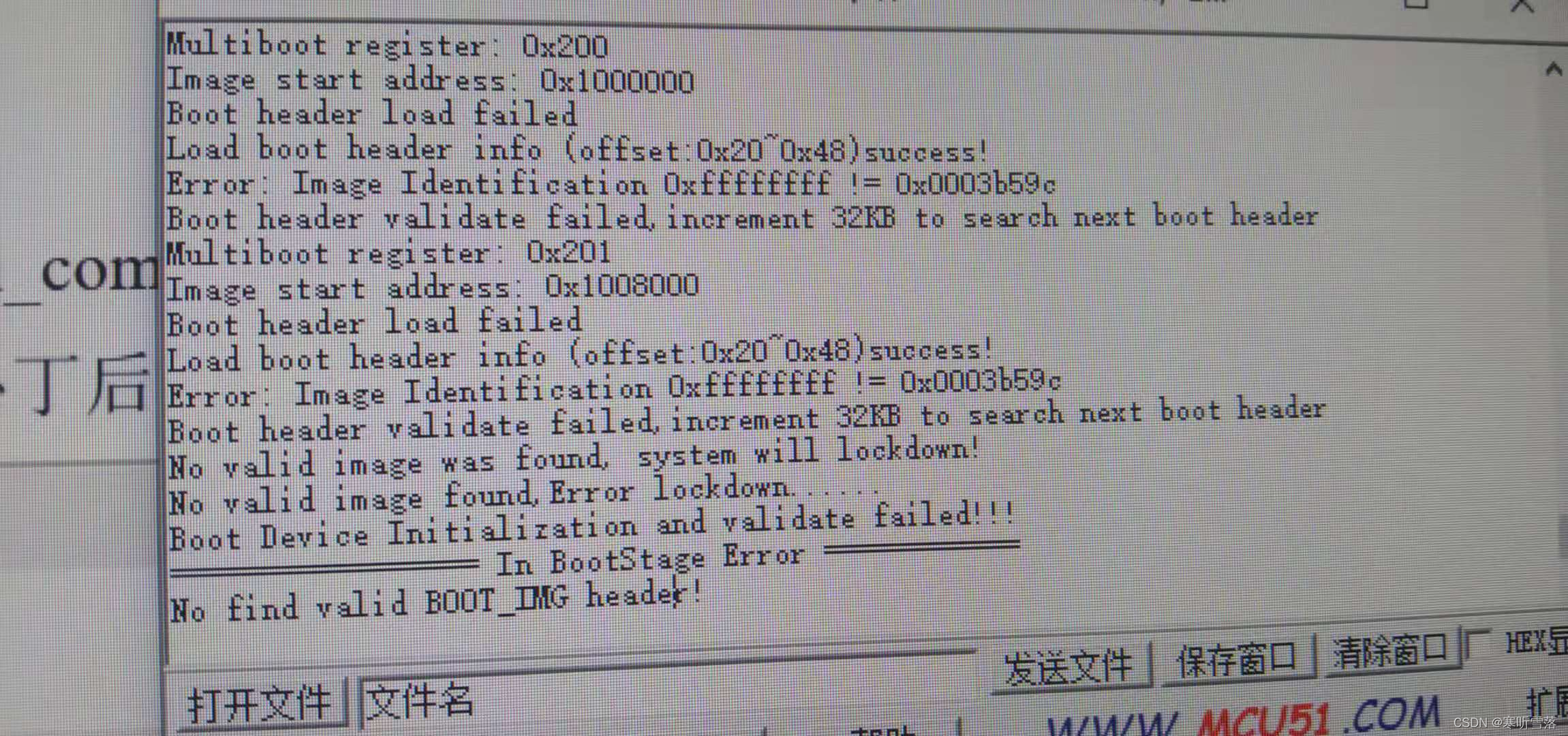

九,BOOT.BIN使用flash loader烧写进去:No find valid BOOT_IMG header!

十,如果板子如果用进口的,硬件不需要改设计,jtag只有一个(45系列的jtag是两个)。

可以用一个jtag,但调试比较麻烦。

十一,程序在sram中运行,但是访问ddr内存地址的话会很慢,有毫秒级的延迟。可以根据sram的地址空间呢,测试一下访问sram的延迟

app在ahb和axi这两个地址空间都可以。有fsbl的话地址不能相互冲突。建议优先使用第二个AHB_SRAM的地址:0xE1FE0000~0xE1FFFFFF。因为第一个axi ram不修改的话容易与fsbl地址冲突。

十二,SPI FLASH支持1线烧写固话程序吗?线接错了具体如何操作

答:可以发单线写命令。

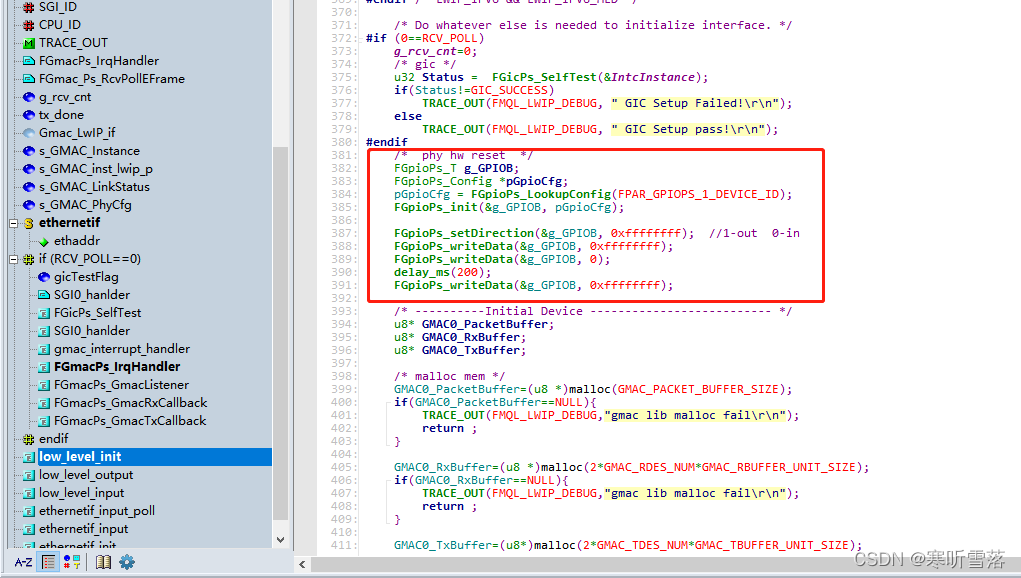

十三,phy如何gpio复位?

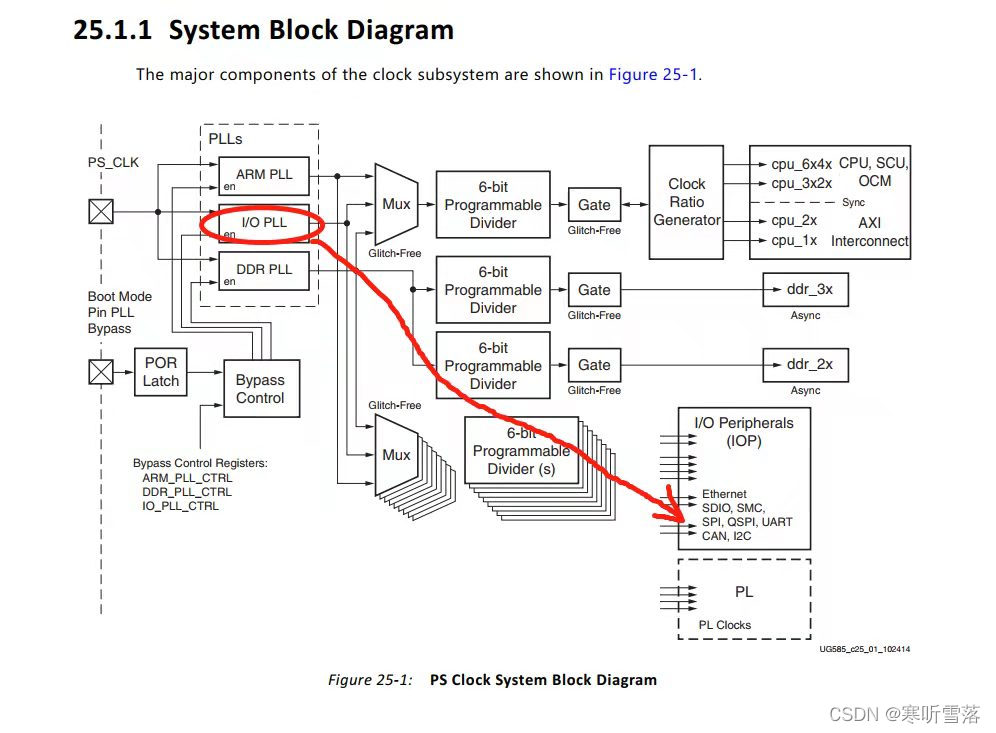

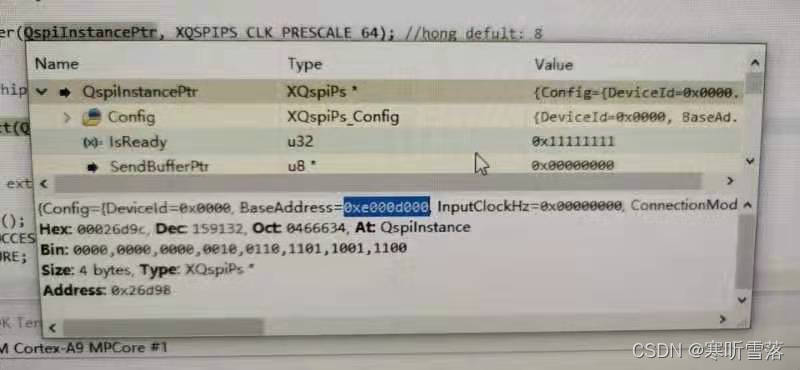

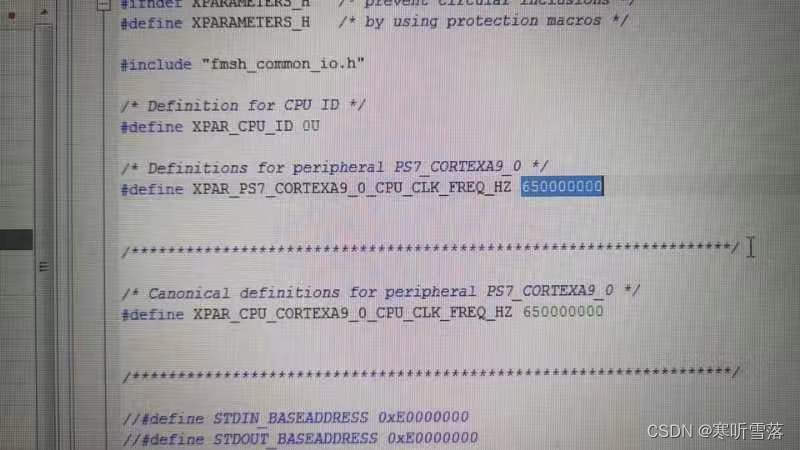

十四,修改200Mqspi的时钟系数,最好直接从vivado中修改,从iar中修改很多时候不生效

如果修改下面IAR的位置是不起作用的,要直接从vivado改完导出到IAR

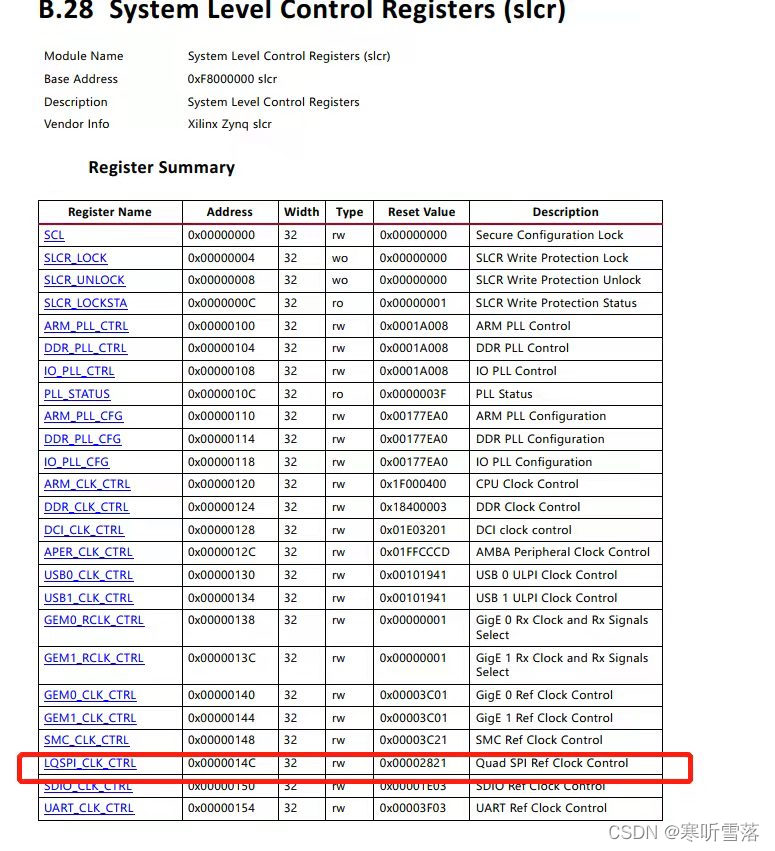

附录:QSPI时钟应该配置的数据和寄存器应该配置的值

附录:QSPI时钟应该配置的数据和寄存器应该配置的值

十五,现象:程序运行在ddr,模拟串口在线调试时候,串口打印特别慢,间隔一两秒才打印出来

十五,现象:程序运行在ddr,模拟串口在线调试时候,串口打印特别慢,间隔一两秒才打印出来

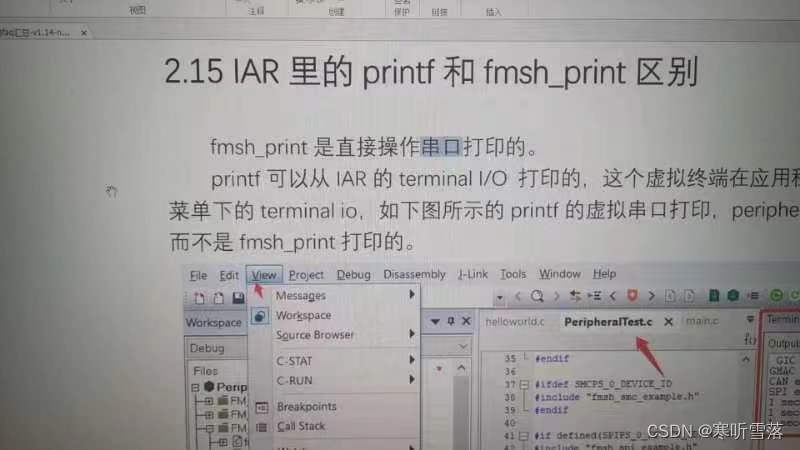

原因分析:printf是输出到模拟串口,fmsh_print是输出到真实串口

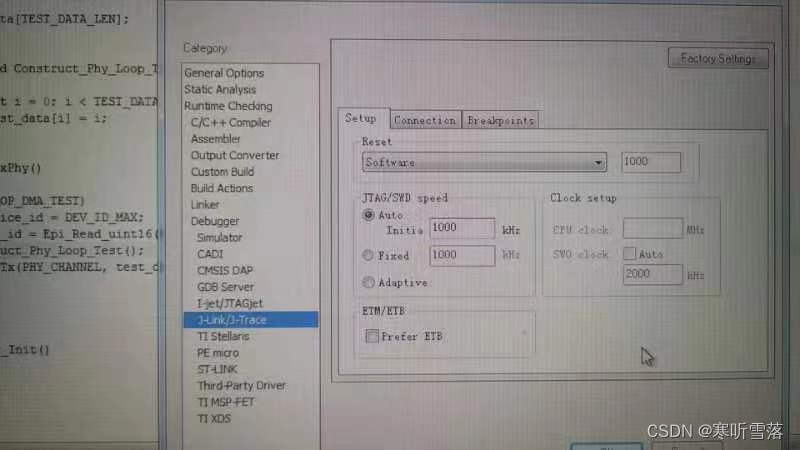

实际配置:JLINK 1000K=1MHZ

解决办法:CPU改成800MHZ,JLINK改成6M

十六,现象:使用qspi 启动,级联模式下,把JLINK挂到PL的JTAG上去下载ps的程序。可以正常扫描到PL和PS,但是无法下载PS程序到FLASH

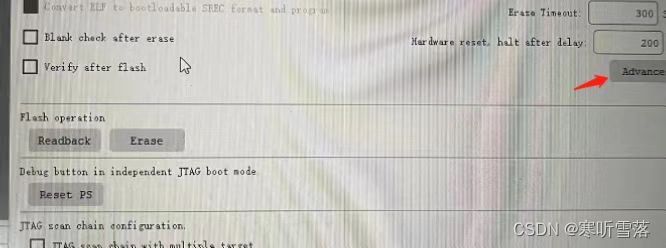

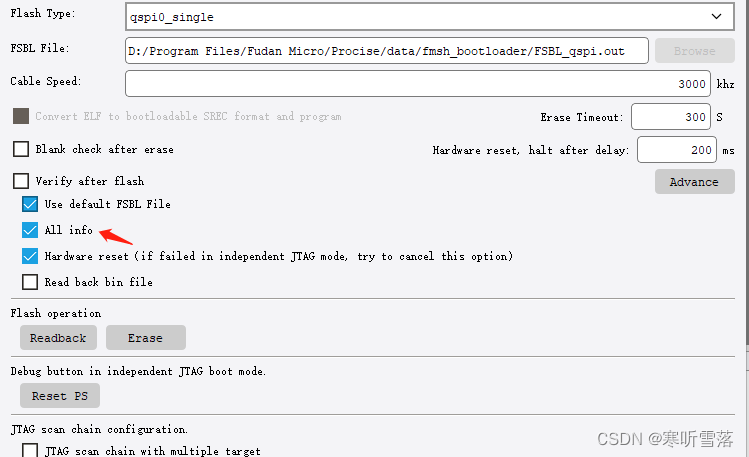

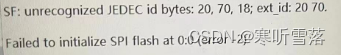

解决办法:点击advance,勾选All info烧结,会在BOOT.bin目录下生成一个log文件,查看log内容

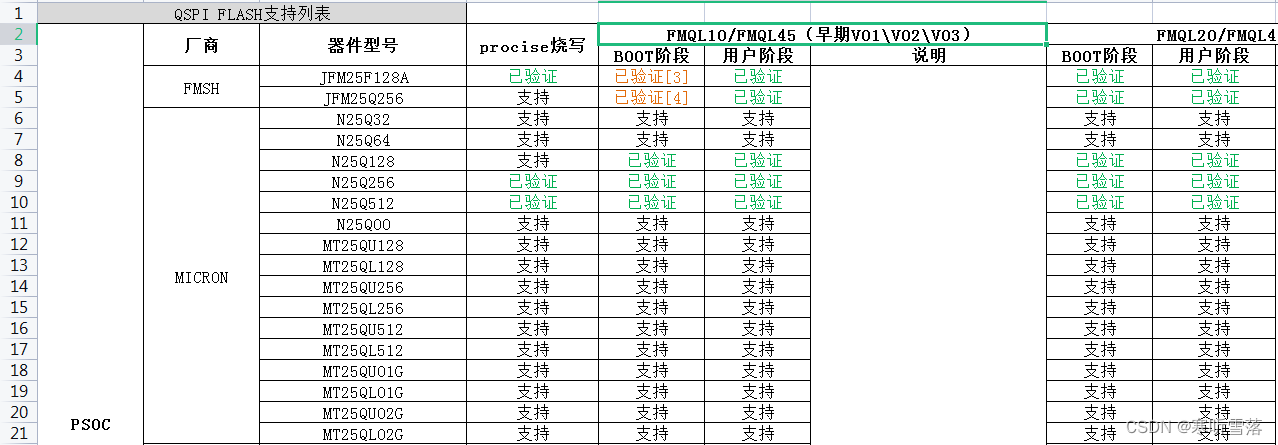

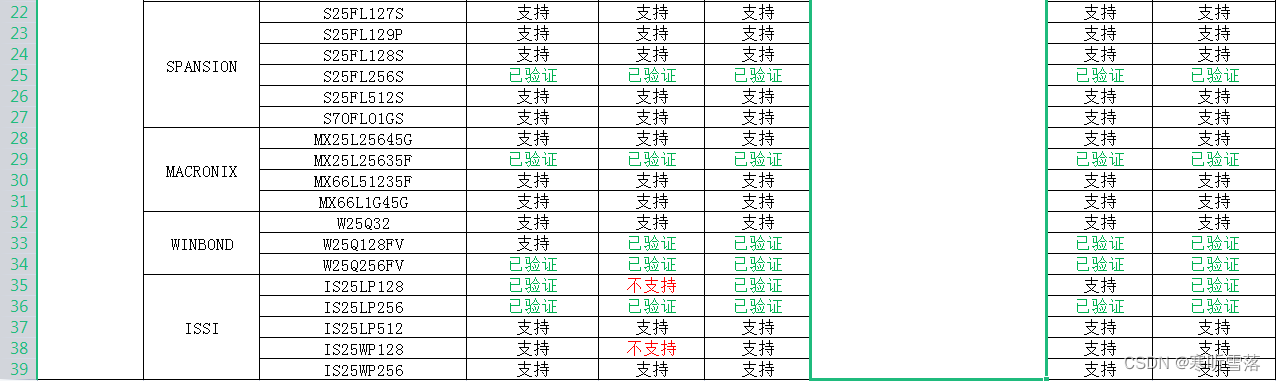

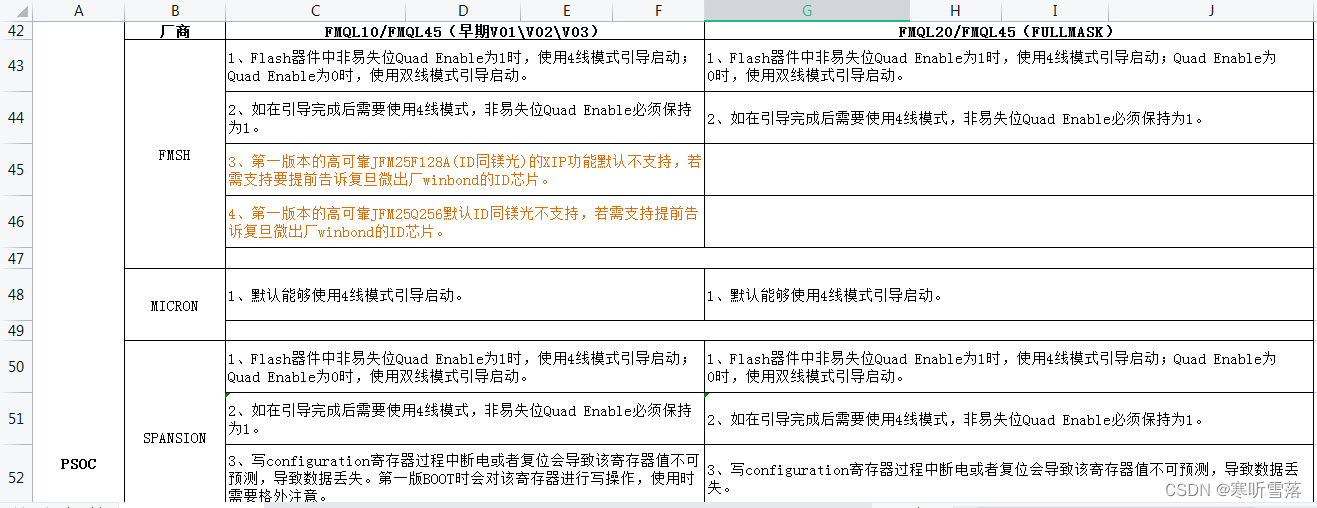

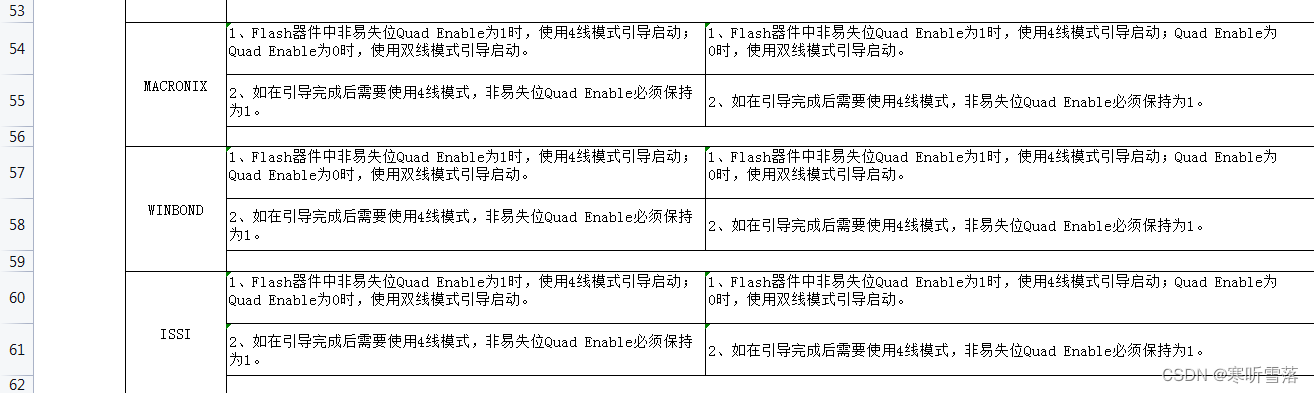

最终log显示不支持该类型的flash,所以flash选型要根据Procise支持列表没有更新过支持的类型

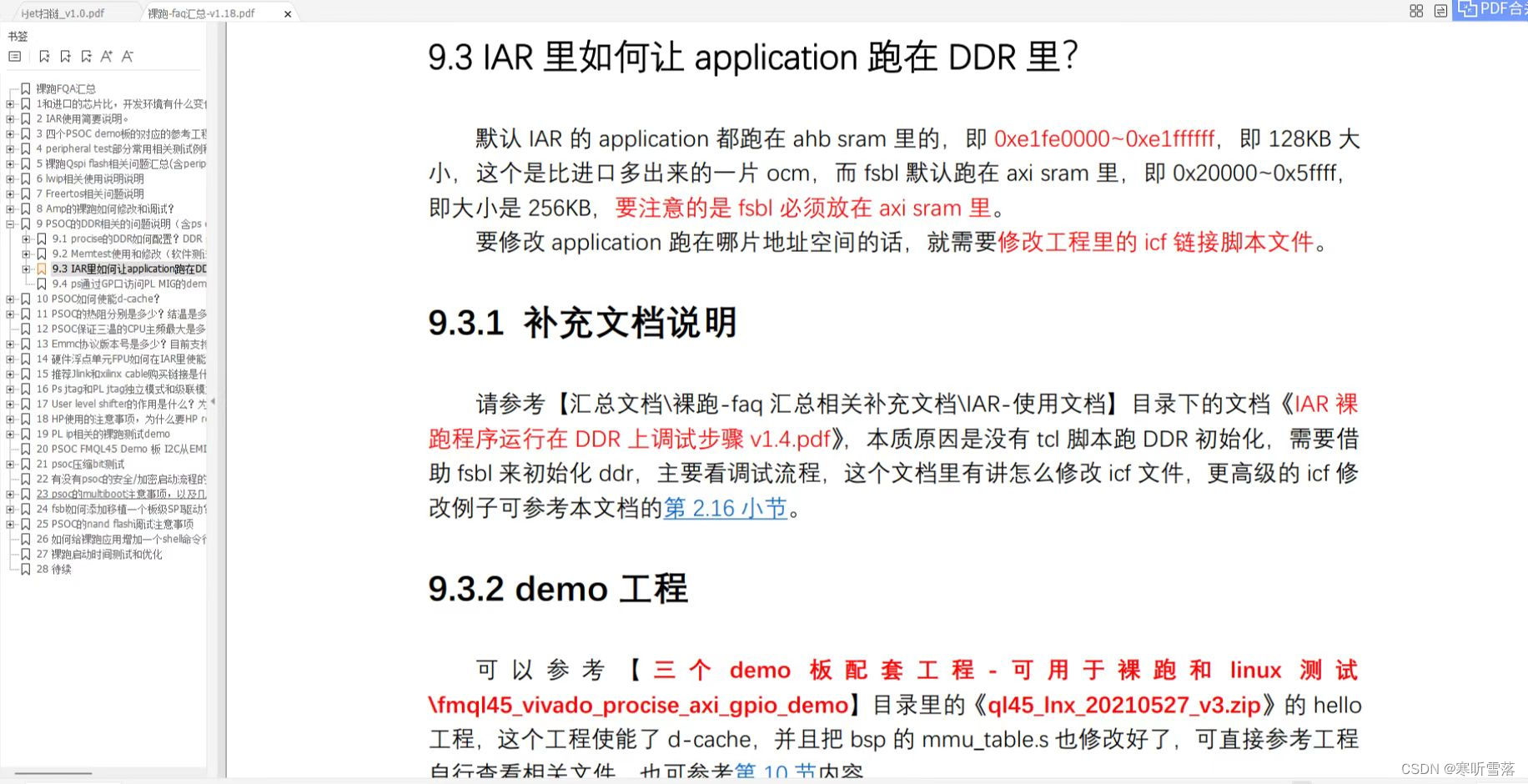

十七,应用程序运行在ddr上,参考具体例程:

十八,复旦微用第三方烧写工具烧写到flash,启动时候fsbl是新的,但app总是跳到之前烧写过的一个程序中?全片擦除flash,只会把fsbl给擦掉,这个旧的用户程序一直存在。从新下载,还是擦除都会从那个旧的用户程序启动。

原因:检查一下打包boot.bin时是否有问题,应该就是打包成boot.bin出现的问题。

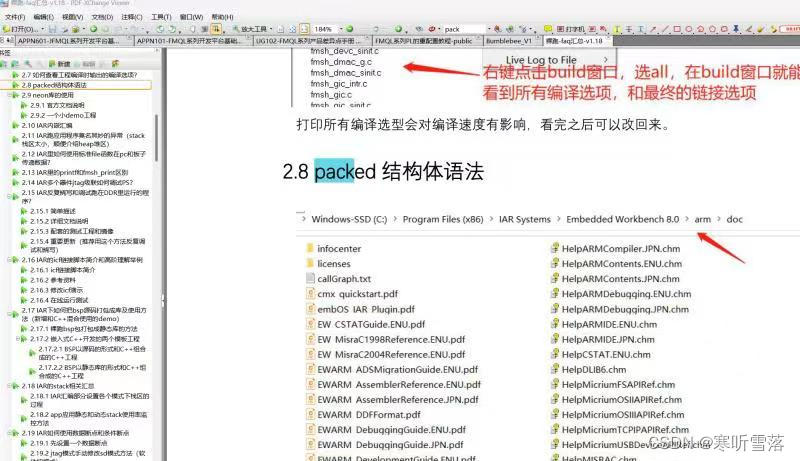

十九,现象:用pack关键字为了保持单字节对齐,编译没有问题,可是在执行过程中会直接异常

解决办法:参考packed结构体语法

二十,7045的GTX参考时钟输入LVDS电平是可以直接用的。

二十一,现象:QSPI启动时候,级联模式下用JTAG扫描,vivadio扫描不到FPGA,但是用jlink 仿真器,process上可以扫描到一个FPGA,还是不能扫到ps。改成jtag独立模式正常扫描pl和ps。

解释:级联模式下,使用Xilinx仿真器接到Bank0的PLJtag上,在vivado或者Procise下应该能同时扫到PS和PL。使用Arm仿真器接到Bank0的PLJtag上, 在Procise下应该能同时扫到PS和PL。

操作步骤:优先使用级联模式,JTAG独立级联模式都可以,QSPI启动级联模式不行,独立模式可以扫到PS和PL。

原因分析:与flash里面固化的版本有关,具体来说是qspi0上接的flash里固化的版本。

二十二,现象:fmql AI100的禁用某段ddr地址的cache功能后无法再访问

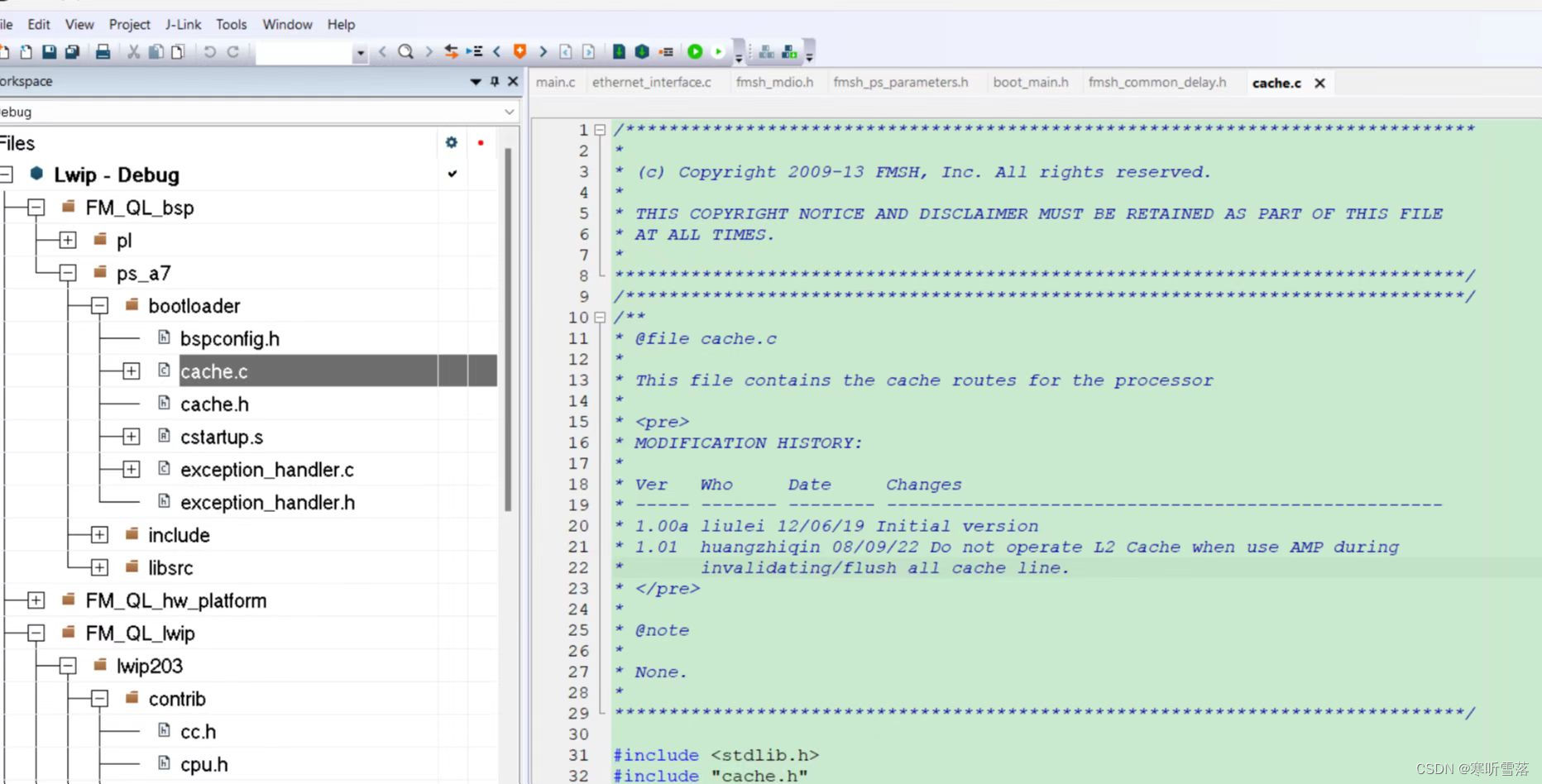

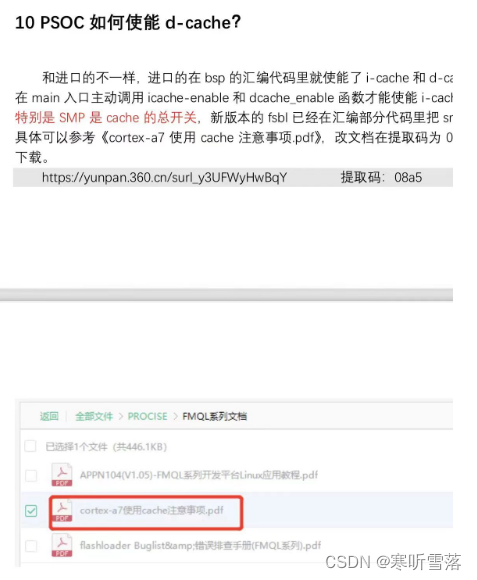

原因:cache功能不是默认打开的,cache需要命令打开的 。cache代码的函数可以参考:

二十三,FMK50支持进口的1.8V供电的英飞凌的flash S25FS512SDSBHV21吗?表格没有

不支持

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!