FPGA学习笔记(2)

程序语句

assign

assign 语句是连续赋值语句,一般是将一个变量的值不间断地赋值给另一变量,格式一般为:

assign a = b (逻辑运算符)c…;

assign 语句的功能属于组合逻辑的范畴,应用范围可以概括为一下几点: (1)持续赋值; (2)连线; (3)对 wire 型变量赋值,wire 是线网,相当于实际的连接线。

always

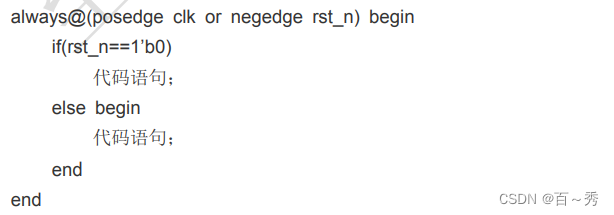

always 语句是条件循环语句,执行机制是通过对一个称为敏感变量表的事件驱动来实现的always 语句的基本格式是:

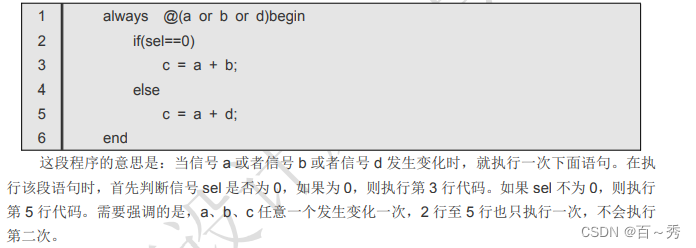

always @(敏感事件)begin

程序语句

end

always 是“一直、总是”的意思,@后面跟着事件。整个 always 的意思是:当敏感事件的条件 满足时,就执行一次“程序语句”。敏感事件每满足一次,就执行“程序语句”一次。

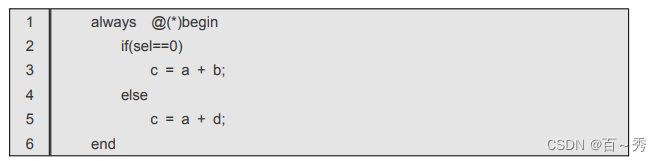

当敏感信号非常多时很容易就会把敏感信号遗漏,为避免这种情况可以用“*”来代替。

这种条件信号变化结果立即变化的 always 语句被称为“组合逻辑”。

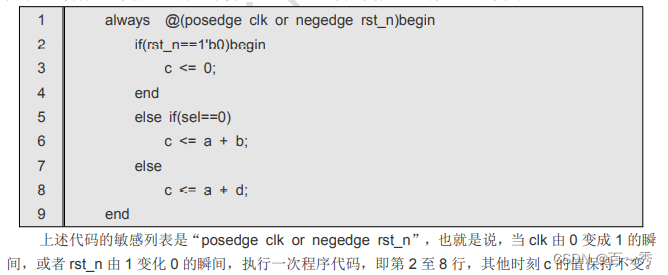

这种信号边沿触发,即信号上升沿或者下降沿才变化的 always,被称为“时序逻辑”,

注:rst_n==1‘b0中 1'b0代表是 1位宽 二进制 数字0 if(rst_n==1'b0)表示低电平复位

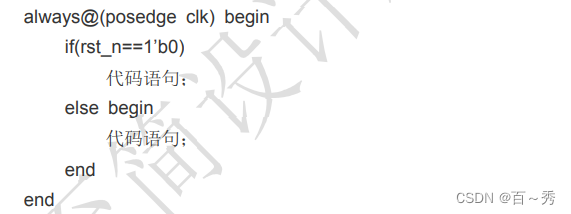

同步复位代码结构:

异步复位代码结构:

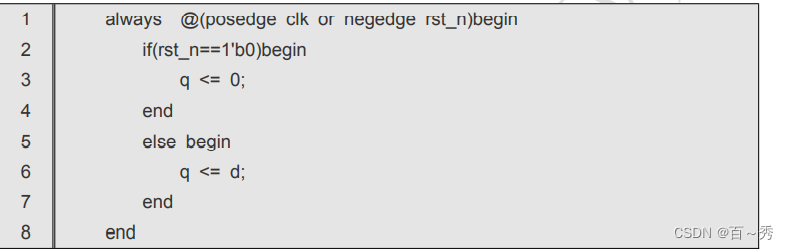

D触发器代码:

rst_n(复位)低电平有效,clk上升沿时将d赋值给q。

时钟

注:1、不要使用代码产生时钟信号,产生的时钟信号不稳定。

2、不要将信号放在时序逻辑敏感列表。例如:( always @(posedge d )begin )

阻塞赋值与非阻塞赋值

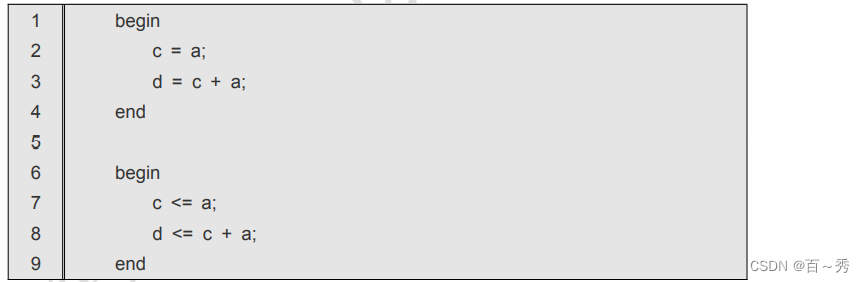

阻塞赋值使用 “=”语句;非阻塞赋值使用“<=”语句。

阻塞赋值:在一个“begin…end”的多行赋值语句,先执行当前行的赋值语句,再执行下一行 的赋值语句。

非阻塞赋值:在一个“begin…end”的多行赋值语句,在同一时间内同时赋值。

在上述例子中,前四行为阻塞赋值、后四行为非阻塞赋值。设初始值 c = 0、a = 1、d = 0;则阻塞赋值的结果为 c = 1、d = 2。非阻塞赋值的结果为 c = 1、d = 1。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!