verilog刷题:valid ready握手无气泡

题目

牛客网刷题 31,数据累加输出

描述

实现串行输入数据累加输出,输入端输入8bit数据,每当模块接收到4个输入数据后,输出端输出4个接收到数据的累加结果。输入端和输出端与上下游的交互采用valid-ready双向握手机制。要求上下游均能满速传输时,数据传输无气泡,不能由于本模块的设计原因产生额外的性能损失。

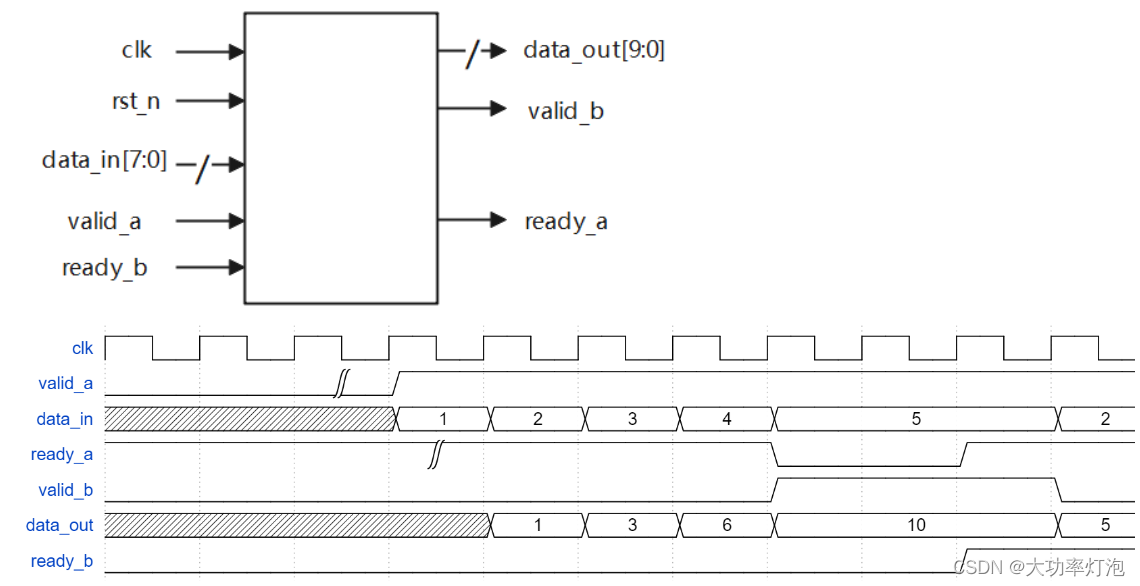

电路的接口如下图所示。valid_a用来指示数据输入data_in的有效性,valid_b用来指示数据输出data_out的有效性;ready_a用来指示本模块是否准备好接收上游数据,ready_b表示下游是否准备好接收本模块的输出数据;clk是时钟信号;rst_n是异步复位信号。

输入描述:

input clk ,

input rst_n ,

input [7:0] data_in ,

input valid_a ,

input ready_b

输出描述:

output ready_a ,

output reg valid_b ,

output reg [9:0] data_out

比较纠结的是输出各个信号相互纠缠,关键是理解ready_a信号的产生;

`timescale 1ns/1nsmodule valid_ready(input clk , input rst_n ,input [7:0] data_in ,input valid_a ,output ready_a ,input ready_b ,output reg valid_b ,output reg [9:0] data_out

);reg[1:0] count;//countalways@(posedge clk or negedge rst_n)if(!rst_n)count <= 2'd0;else if(valid_a && ready_a)count <= count+1; //此处加1自动归0,如果接收5个数,需要给出判断条件//valid_b //数据有效时1, 为1时检测到ready为1拉0,其它情况0always@(posedge clk or negedge rst_n)if(!rst_n)valid_b <= 1'b0;else if(valid_b == 1'b1 && ready_b) //valid_b <= 1'b0;else if(valid_b == 1'b0 && count==3) //valid_b <= 1'b1;//ready_a 无气泡体现在此, 组合逻辑判定是否 valid_b 和 !ready_b ,上级传输无气泡assign ready_a = !(valid_b && !ready_b); //data //注意需要清累加和always@(posedge clk or negedge rst_n)if(!rst_n)data_out <= 10'd0;else if(valid_a && ready_a)if(count==0)data_out <= data_in;elsedata_out <= data_out+ data_in;endmodule

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!