主从D触发器的实现及建立保持时间详解

主从D触发器的实现及建立保持时间详解

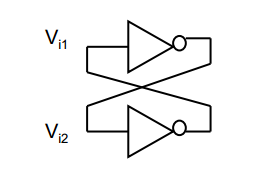

1. 双稳态电路

双稳态电路原理图如下图所示,可以用来构成存储单元(锁存器,触发器),SRAM等。

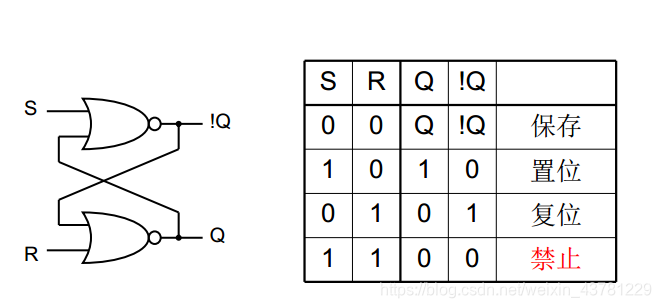

2. RS锁存器

电路结构及真值表如下图所示:

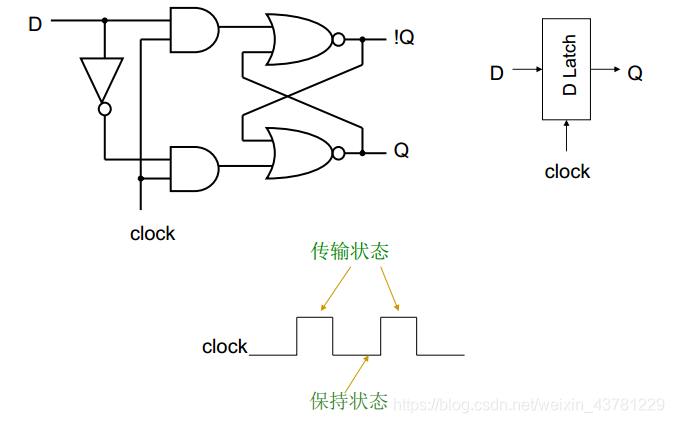

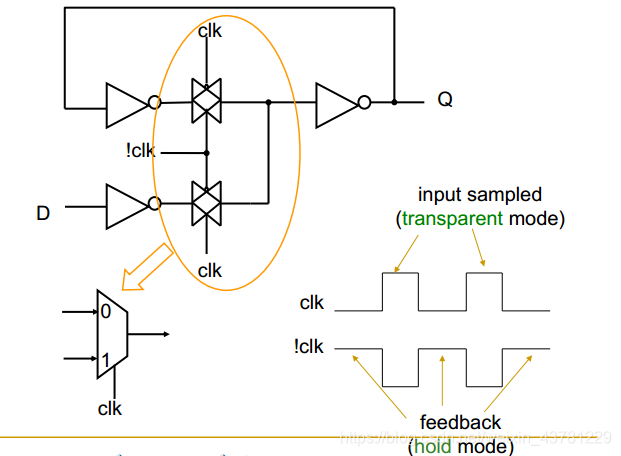

3. 带时钟信号的D锁存器

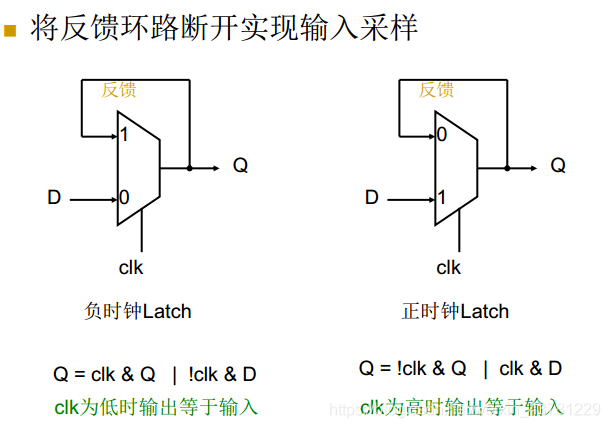

4. 基于二选一电路的D锁存器

5. D锁存器电路(传输们实现二选一)

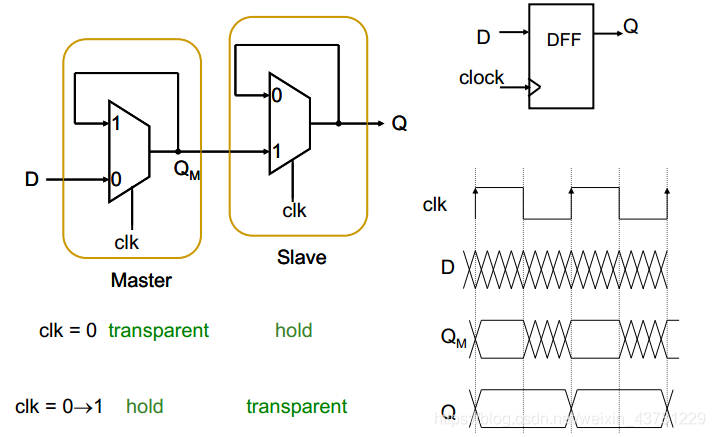

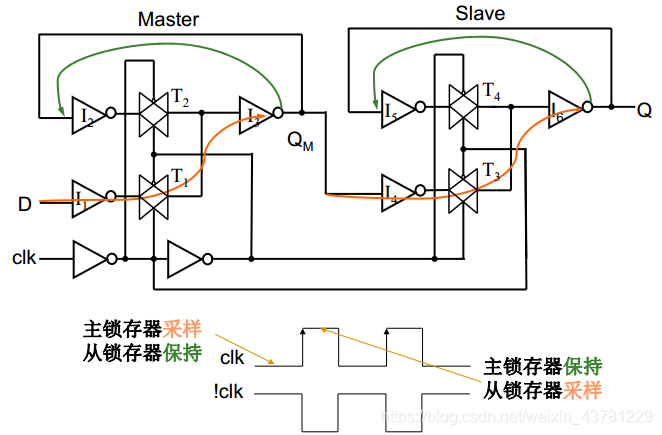

6. 主从D触发器

电路实现如下

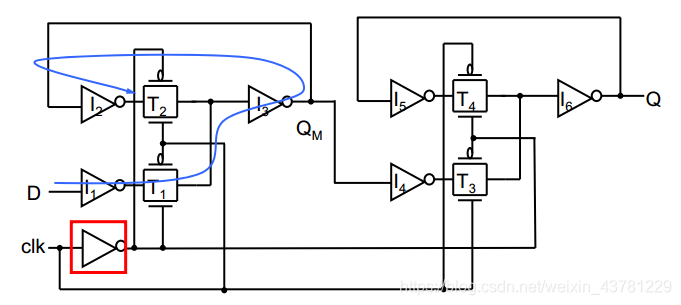

从下面这张图便可以很容易的感知建立时间的起因

在clk上升沿前, D需要稳定多少时间使得QM采样到的值是正确的。

D需要通过I1、 T1、 I3、 I2,忽略时钟反相器的延时

tsetup=3tp_inv+tpd_tx

I2、 I3满足建立时间,所以I4在clk的上升沿就稳定了。

传输延时为信号通过T3、 I6的时间

tc-d=tpd_inv+tpd_tx

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!