VHDL 4-16译码器 三位十进制加法计数器 原理图文件创作bdf创作

本文讲述vhdl中如何进行原理图文件编辑,即bdf文件的设计,设计内容为以下三点,详细制作过程,图文描述,逐一讲解步骤PDF以及源程序均在文末链。

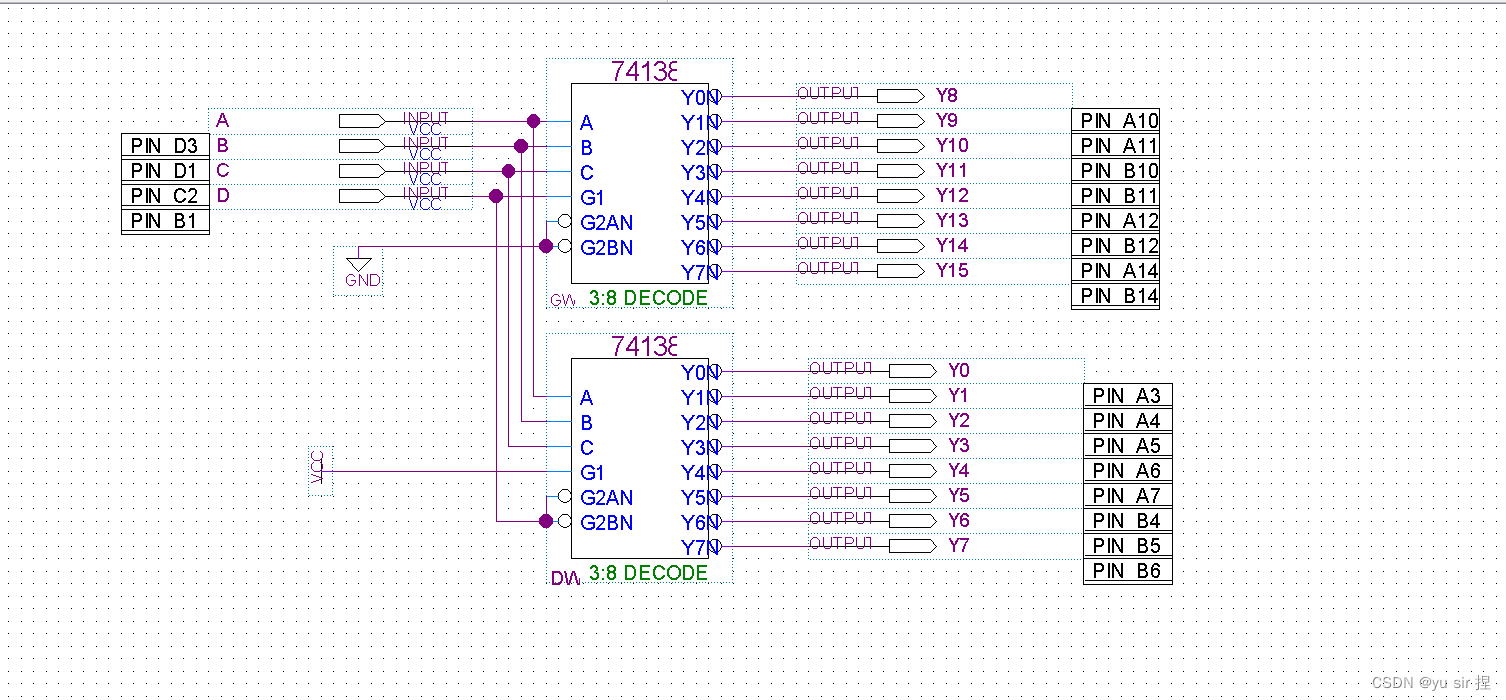

1.在图形编辑器中采用 MF 图元(74138)设计一个 4-16 译码器,以 decod***.gdf 命名保存。 将器件设定为 EP3C16F256C8。输入 D、C、B、A 绑定到 B1,C2,D1,D3 管脚,输出 Y0…Y15 按顺序绑定到 A3,A4,A5,A6,A7,B4,B5,B6,A10,A11,B10,B11,A12,B12,A14,B14 管脚。进行波形仿 真,验证功能正确。分析节点 A 到节点 y15 的最短延时。

2.在图形编辑器中设计一个 3 位的十进制加法计数器,以***cnt3.gdf 命名保存。器件设定为 EP3C16F256C8。要求能够从 0 计数到 999。从 999 归零时产生一个高电平的报警信号。进 行波形仿真,验证功能正确。分析此电路的最高计数频率。

3.在上述设计基础上增加加法计数/减法计数控制功能和置数功能,并使其计数到 119 就归 零。文件名修改为***119.gdf

链接:https://pan.baidu.com/s/1qTwgY2DjKI66gGNc_qDvmw

提取码:nm7p

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!