基于Vivado上用Verilog和vivado上的IP核中的锁相实现PLL锁相环进行倍频、分频

- 1,锁相环原理图

- 2,RTL代码设计+IP核的端口例化

- 3,端口的约束文件

- 4,testbench代码

- 5,RTL代码+Testbench测试代码生成的门级网表:Netlist

- 6,前仿真波形验证

- 7,可生成Bitstream然后下载到板级进行验证!

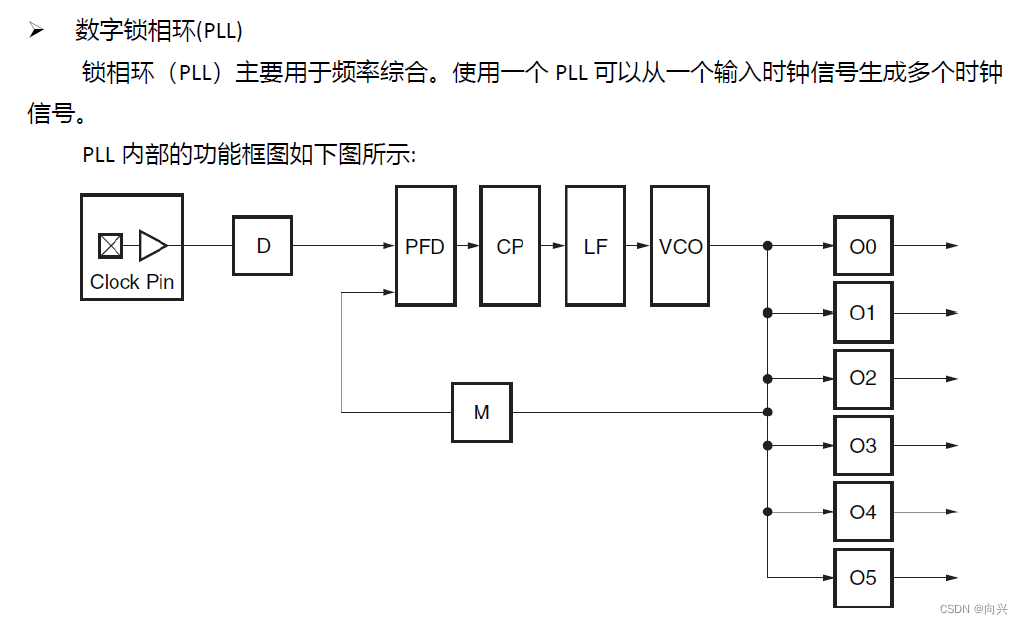

1,锁相环原理图

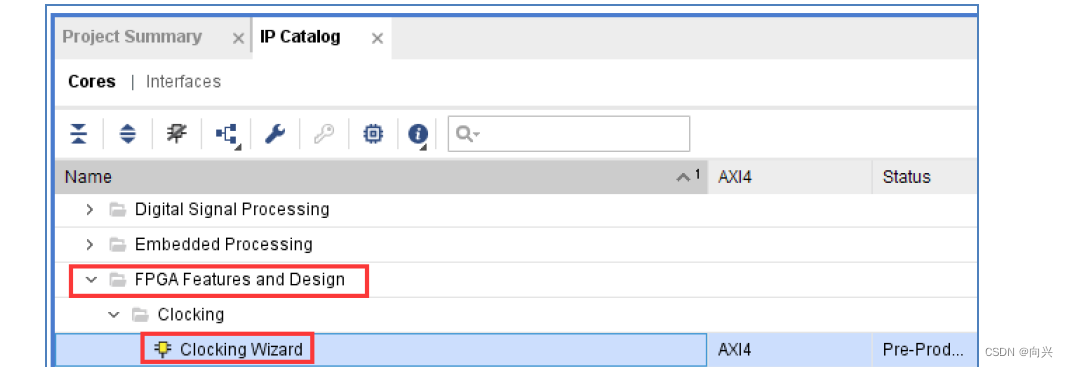

选择IP核

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!