使用D触发器设计8进制计数器数字电路

一.实验目的

1.掌握使用逻辑方法设计时序逻辑数字电路。

2. 掌握使用原理图完成时序逻辑电路的设计。

3. 掌握时序逻辑电路的编译、调试、仿真、烧录方法。

4. 理解时序逻辑数字电路的设计思想。

二.实验要求

使用D触发器设计8进制计数器数字电路,并完成电路的仿真和烧录过程。

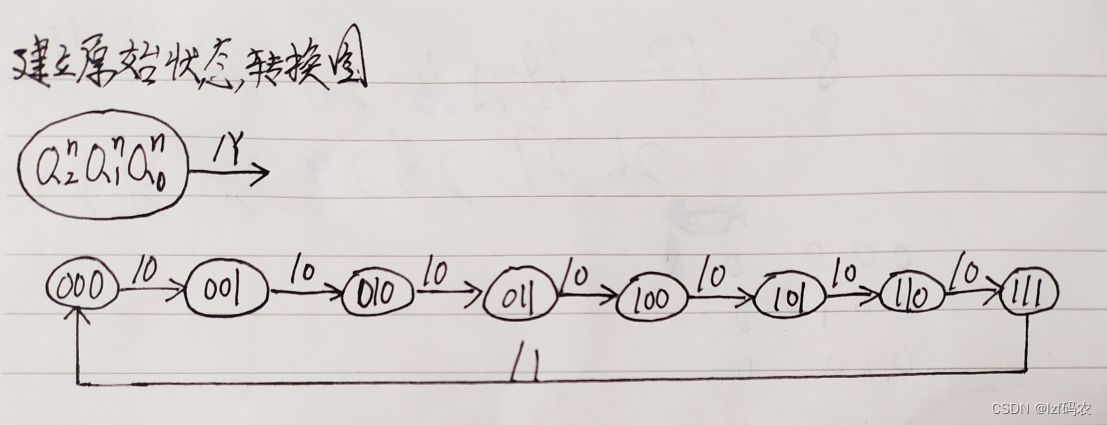

建立原生状态图:

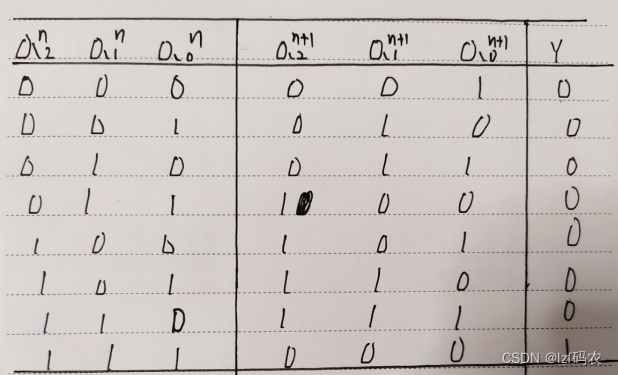

状态转移表:

时钟方程:

CP0=CP1=CP2=CP

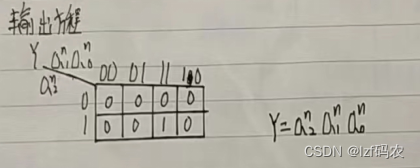

输出函数的卡诺图和输出方程:

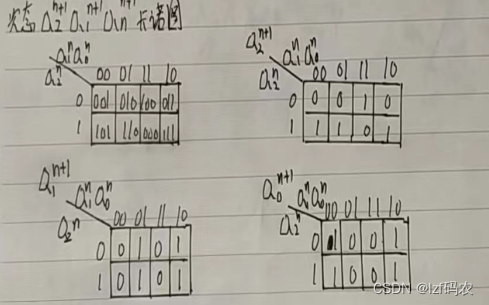

次态卡诺图:

次态卡诺图得:

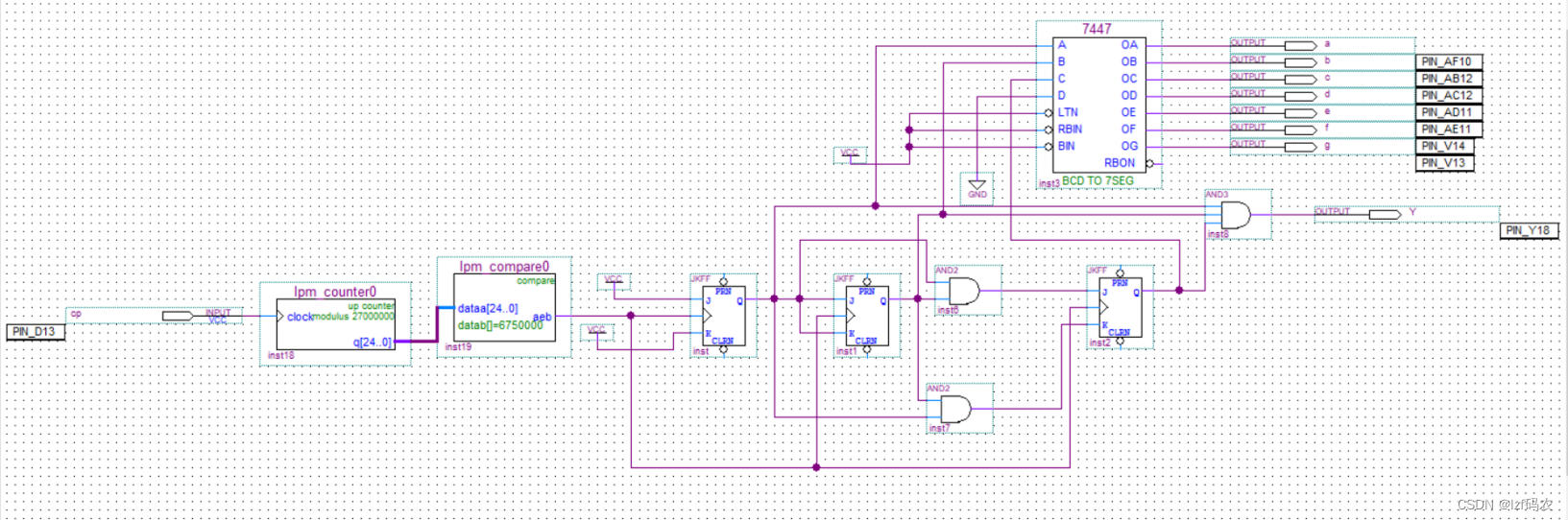

设计电路图

主要有3个jk触发器、一个显示译码器(共阳级)、一个能产生CP周期为1秒钟的时钟信号的模块器件和一些简单的逻辑器件

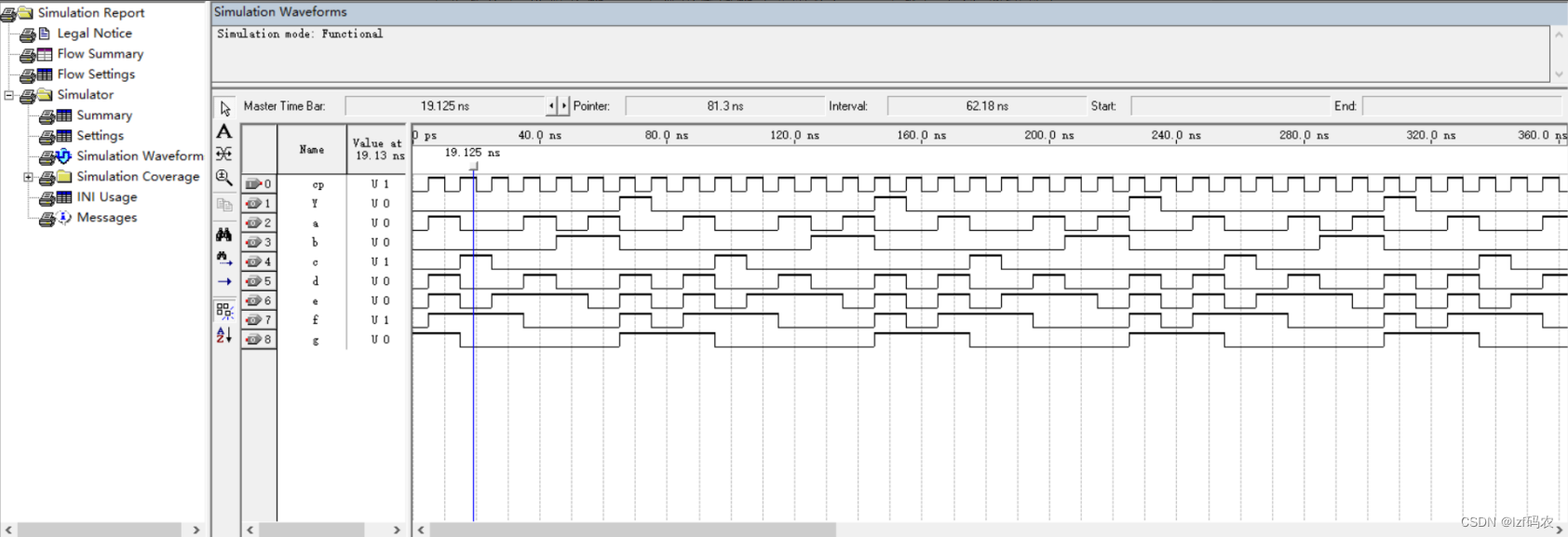

正确仿真结果如下:

烧录结果

省略

以上就是使用D触发器设计8进制计数器数字电路过程,若对各位有帮助,请点点个赞或关注!!

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!