【FPGA算法加速】使用FPGA硬件编程编程语言Verilog编写HDL程序中向量的使用案例

1、向量

向量用于使用一个名称对相关信号进行分组,以便于操作。

例如,wire [7:0] w;声明一个名为w的 8 位向量,相当于有 8 条单独的连线。

向量的声明将维度放在向量名称之前,这与 C 语法相比是不寻常的。

但是部分选择在矢量名称之后具有您所期望 的尺寸。

wire [7:0] w; // 8位线

reg [4:1] x; // 4位线

output reg [0:0] y; // 输出端口y为向量

input wire [3:-2] z; // 输入为6位向量允许负范围

output [3:0] a; // 4位输出线。除非另有说明,否则类型为“wire”

wire [0:7] b; // 8 位线,其中 b[0] 是最高有效位

wire [99:0] my_vector; // 申明100个向量

assign out = my_vector[10]; // 输出部分向量成员

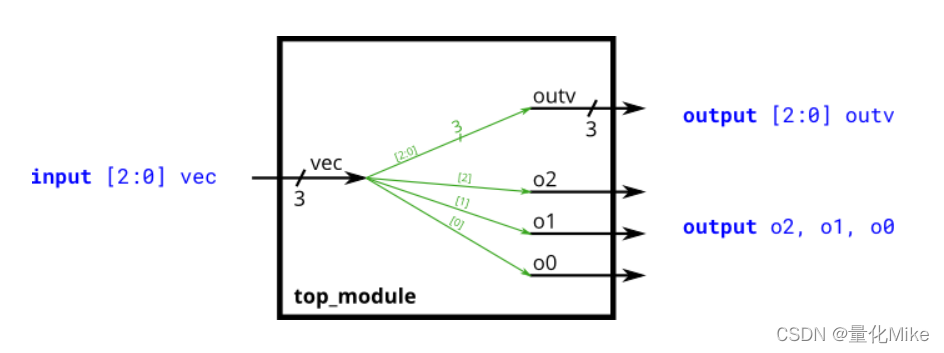

构建一个具有一个 3 位输入的电路,然后输出相同的向量,并将其拆分为三个单独的 1 位输出。将输出连接o0到输入向量的位置 o0、o1、o2位置。在图中,旁边带有数字的刻度线表示向量(或“总线”)的宽度,而不是为向量中的每个位绘制单独的线。

module top_module ( input wire [2:0] vec,output wire [2:0] outv,output wire o2,output wire o1,output wire o0 ); // Module body starts after module declarationassign outv = vec;assign o2 = vec[2];assign o1 = vec[1];assign o0 = vec[0];endmodule

2、向量反转

一个 32 位向量可以被视为包含 4 个字节(位 [31:24]、[23:16] 等)。构建一个将反转4 字节字 的字节顺序的电路。

AaaaaaaaBbbbbbbbCcccccccDdddddddd => DddddddCcccccccBbbbbbbbAaaaaaaaa

当需要交换一条数据 的字节顺序时,通常会使用此操作,例如在小端 x86 系统和许多 Internet 协议中使用的大端格式之间。

module top_module (input [31:0] in,output [31:0] out

);assign out[31:24] = in[ 7: 0]; assign out[23:16] = in[15: 8]; assign out[15: 8] = in[23:16]; assign out[ 7: 0] = in[31:24]; endmodule3、按位与逻辑运算符

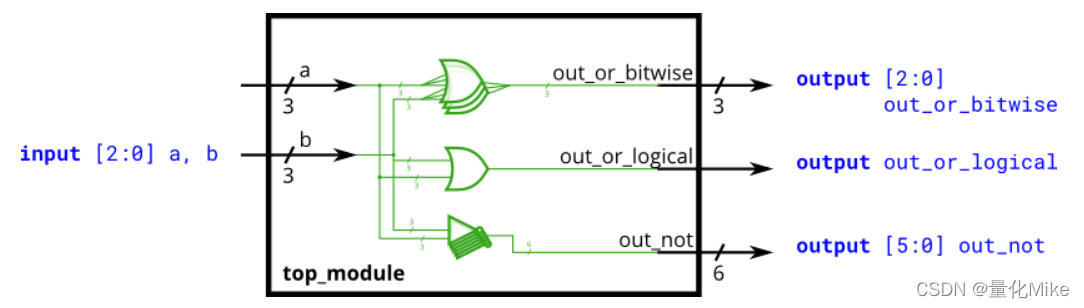

使用向量时,两种运算符类型之间的区别变得很重要。两个 N 位向量之间的按位运算复制向量的每个位的运算并产生 N 位输出,而逻辑运算将整个向量视为布尔值(真 = 非零,假 = 零)和产生 1 位输出。

module top_module( input [2:0] a,input [2:0] b,output [2:0] out_or_bitwise,output out_or_logical,output [5:0] out_not

);assign out_or_bitwise[2] = a[2] || b[2];assign out_or_bitwise[1] = a[1] || b[1];assign out_or_bitwise[0] = a[0] || b[0];assign out_or_logical = a || b;assign out_not[2:0] = ~a;assign out_not[5:3] = ~b;endmodule

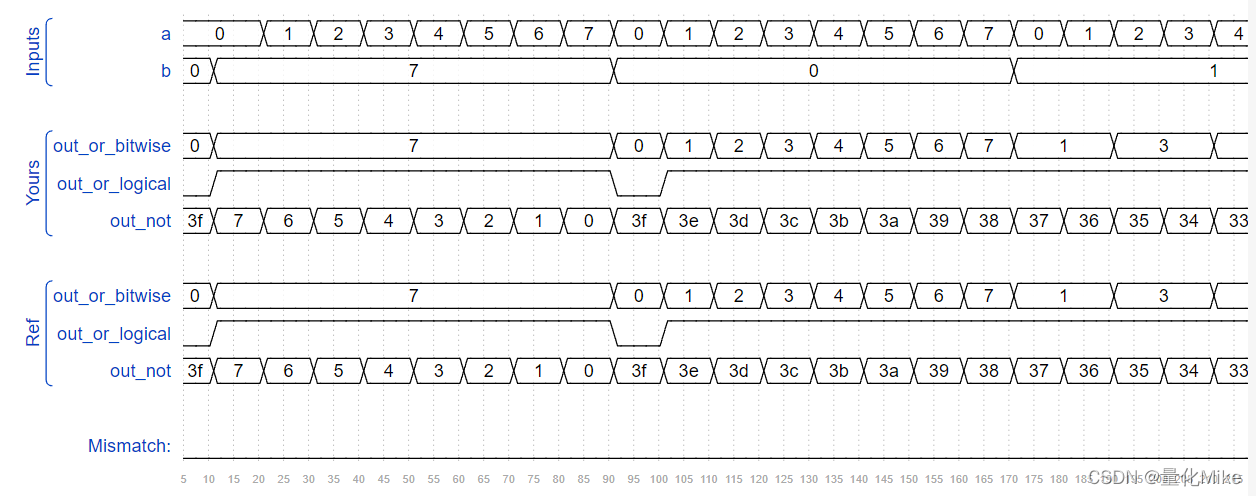

时序图:

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!