.net get set 初始化_RAM初始化的下板验证(Xilinx)

欢迎FPGA工程师加入官方微信技术群

点击蓝字关注我们FPGA之家-中国最好最大的FPGA纯工程师社群

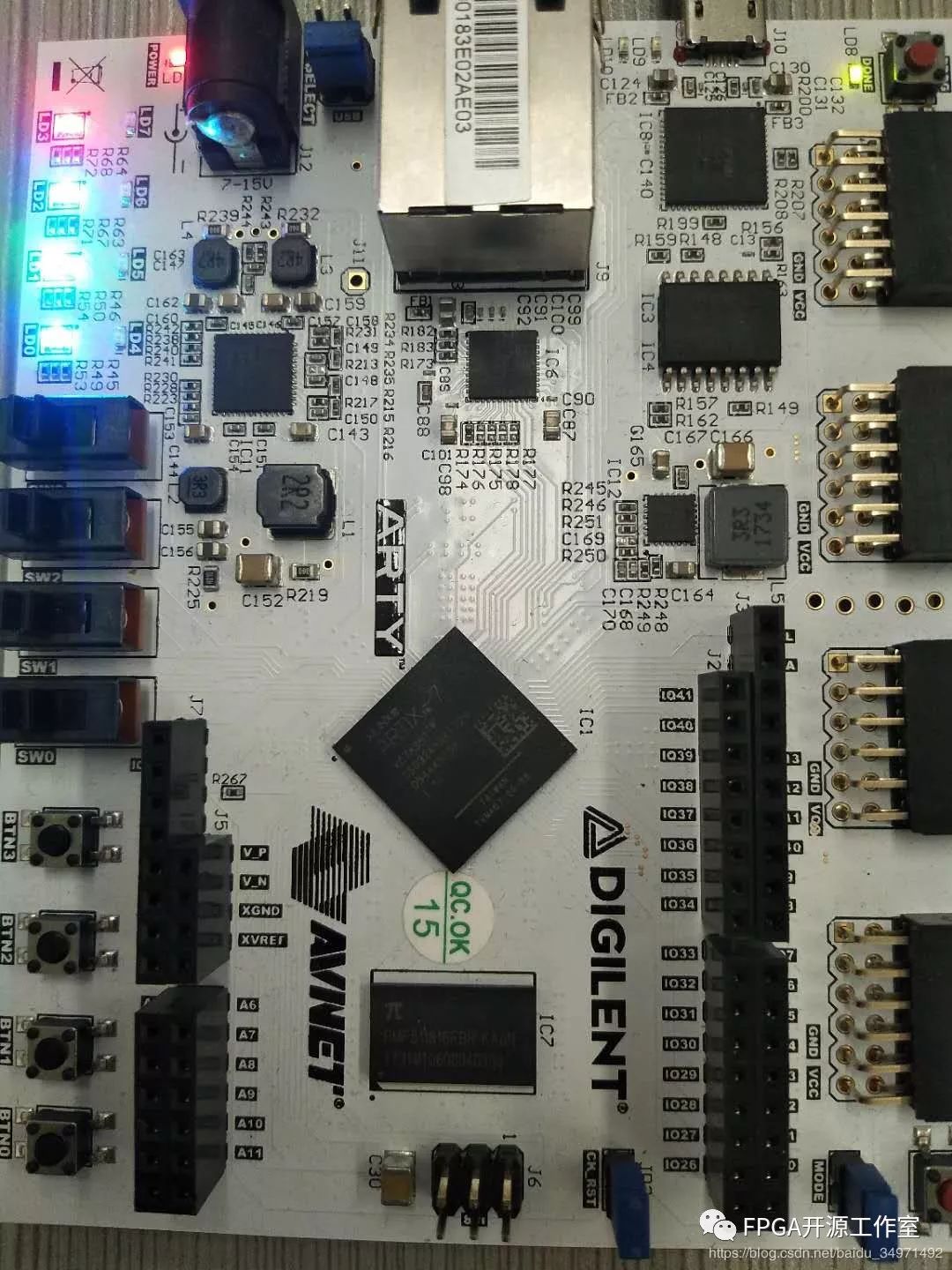

本实验基于xilinx ARTIX-7芯片验证实现,有时间有兴趣的朋友可在其他FPGA芯片上实现验证。

当大家看到《xilinx verilog语法技巧(三)–RAM的初始化》文章的时候很多人认为initial语句,$readmemb语句均是不可综合语句(只能用来写测试文件),但是xilinx的综合器已经悄然改变了这一点。

rams_init_file源码:

// Initializing Block RAM from external data file

// Binary data

// File: rams_init_file.v

module rams_init_file (clk, we, addr, din, dout);

input clk;

input we;

input [5:0] addr;

input [31:0] din;

output [31:0] dout;

reg [31:0] ram [0:63];

reg [31:0] dout;

initial begin

$readmemb("rams_init_file.data",ram);

end

always @(posedge clk)

begin

if (we)

ram[addr] <= din;

dout <= ram[addr];

end endmodule

rams_init_file.data源文件:

00001110110000011001111011000110

00101011001011010101001000100011

01110100010100011000011100001111

01000001010000100101001110010100

00001001101001111111101000101011

00101101001011111110101010100111

11101111000100111000111101101101

10001111010010011001000011101111

00000001100011100011110010011111

11011111001110101011111001001010

11100111010100111110110011001010

11000100001001101100111100101001

10001011100101011111111111100001

11110101110110010000010110111010

01001011000000111001010110101110

11100001111111001010111010011110

01101111011010010100001101110001

01010100011011111000011000100100

11110000111101101111001100001011

10101101001111010100100100011100

01011100001010111111101110101110

01011101000100100111010010110101

11110111000100000101011101101101

11100111110001111010101100001101

01110100000011101111111000011111

00010011110101111000111001011101

01101110001111100011010101101111

10111100000000010011101011011011

11000001001101001101111100010000

00011111110010110110011111010101

01100100100000011100100101110000

10001000000100111011001010001111

11001000100011101001010001100001

10000000100111010011100111100011

11011111010010100010101010000111

10000000110111101000111110111011

10110011010111101111000110011001

00010111100001001010110111011100

10011100101110101111011010110011

01010011101101010001110110011010

01111011011100010101000101000001

10001000000110010110111001101010

11101000001101010000111001010110

11100011111100000111110101110101

01001010000000001111111101101111

00100011000011001000000010001111

10011000111010110001001011100100

11111111111011110101000101000111

11000011000101000011100110100000

01101101001011111010100011101001

10000111101100101001110011010111

11010110100100101110110010100100

01001111111001101101011111001011

11011001001101110110000100110111

10110110110111100101110011100110

10011100111001000010111111010110

00000000001011011111001010110010

10100110011010000010001000011011

11001010111111001001110001110101

00100001100010000111000101001000

00111100101111110001101101111010

11000010001010000000010100100001

11000001000110001101000101001110

10010011010100010001100100100111

tb_rams_init_file测试顶层文件:

`timescale 1ns / 1ps

module tb_rams_init_file(

input clk,

input reset,

output [2:0] led_rgb0,

output [2:0] led_rgb1,

output [2:0] led_rgb2,

output [2:0] led_rgb3

);

reg [5:0] addr;

wire [31:0] dout;

reg [27:0] cnt;

assign led_rgb0 = dout[2:0];

assign led_rgb1 = dout[5:3];

assign led_rgb2 = dout[8:6];

assign led_rgb3 = dout[11:9];

always @(posedge clk ) begin

if(reset==1'b1) begin

cnt <= 28'd0;

addr <= 0;

end

else if(cnt == 28'd100000000)begin//1s

cnt <= 28'd0;

addr <= addr +1;

end

else begin

cnt <= cnt + 1;

addr <= addr;

end

end

rams_init_file u_rams_init_file(

.clk(clk),

.we(1'b0),

.addr(addr),

.din(32'b0),

.dout(dout));

endmodule

约束文件(根据自己板卡):

set_property PACKAGE_PIN E3 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property PACKAGE_PIN D9 [get_ports reset]

set_property IOSTANDARD LVCMOS33 [get_ports reset]

set_property PACKAGE_PIN E1 [get_ports led_rgb0[0]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb0[0]]

set_property PACKAGE_PIN G6 [get_ports led_rgb0[1]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb0[1]]

set_property PACKAGE_PIN F6 [get_ports led_rgb0[2]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb0[2]]

set_property PACKAGE_PIN G4 [get_ports led_rgb1[0]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb1[0]]

set_property PACKAGE_PIN G3 [get_ports led_rgb1[1]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb1[1]]

set_property PACKAGE_PIN J4 [get_ports led_rgb1[2]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb1[2]]

set_property PACKAGE_PIN H4 [get_ports led_rgb2[0]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb2[0]]

set_property PACKAGE_PIN J3 [get_ports led_rgb2[1]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb2[1]]

set_property PACKAGE_PIN J2 [get_ports led_rgb2[2]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb2[2]]

set_property PACKAGE_PIN K2 [get_ports led_rgb3[0]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb3[0]]

set_property PACKAGE_PIN K1 [get_ports led_rgb3[1]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb3[1]]

set_property PACKAGE_PIN H6 [get_ports led_rgb3[2]]

set_property IOSTANDARD LVCMOS33 [get_ports led_rgb3[2]]

测试效果:

视频结果展示

欢迎通信工程师和FPGA工程师关注公众号

全国第一大FPGA微信技术群

欢迎大家加入全国FPGA微信技术群,这个群体拥有数万工程师、一群热爱技术的工程师,这里的FPGA工程师相互帮助,相互分享,技术氛围浓厚!赶紧叫上小伙伴一起加入吧!!

用手指按住就可以加入FPGA全国技术群哦

FPGA之家元器件芯城

优势元器件服务,有需求请扫码联系群主:金娟 邮箱:293580331@qq.com 欢迎推荐给采购

ACTEL、AD部分优势订货(经营全系列):

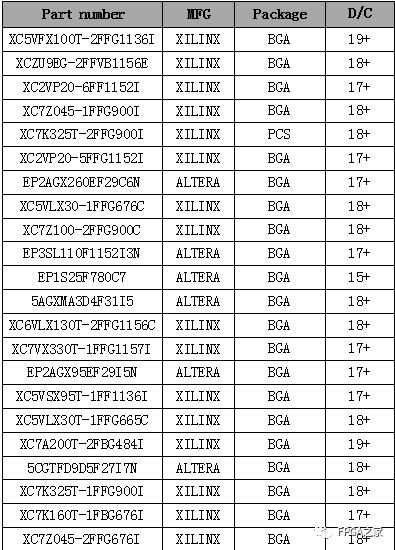

XILINX、ALTERA优势现货或订货(经营全系列):

(以上器件为部分型号,更多型号请咨询群主金娟)

服务理念:FPGA之家元器件自营芯城,旨在方便工程师快速方便购买器件服务,经过数年竭诚服务,我们的客服遍布国内大型上市公司、军工科研单位、中小企业、最大的优势是强调服务至上的理念、并且做到快速交货、价格优惠!

直营品牌:Xilinx ALTERA ADI TI NXP ST E2V、镁光 等百余元器件品牌,尤其擅长欧美对华禁运器件,欢迎工程师朋友把我们推荐给采购或者亲自咨询我们!我们将一如既往提供业内最佳服务!

FPGA技术群官方鸣谢品牌:Xilinx、 intel(Altera)、microsemi(,Actel)、LattIC e,Vantis,Quicklogic,Lucent等

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!