【RISC-V_SoC】多核处理器的实现

文章目录

- 多核处理器

- 1、功耗墙问题

- 多核处理器的访存结构

- 1、通用多核处理器的片上 Cache 结构

- 2、存储一致性模型

多核处理器

1、功耗墙问题

面对单芯片上的大量晶体管, 如何设计处理器有两种思路:

一种是单芯片设计复杂的单处理器核

一种是单芯片设计多个处理器核

1、复杂单处理器核以提高性能的主要方法:

通过微结构优化提高每个时钟周期发射执行的指令数

通过提高主频来提高性能

- 开关功耗与主频成正比, 与电压的平方成正比, 即在一定范围内功耗与主频的三次方成正比, 主频提高 10%导致功耗提高 30%。

2、设计多个处理器核以提高性能的方法:

通过增加处理器核的个数来提升处理器并行处理的性能。

- 当处理器核数目增加 N 倍时, 功耗也大致增加 N 倍, 性能也增加 N 倍 (此处性能主要指运行多个程序的吞吐率), 也就是说功耗随着性能的提高线性增长

多核处理器的访存结构

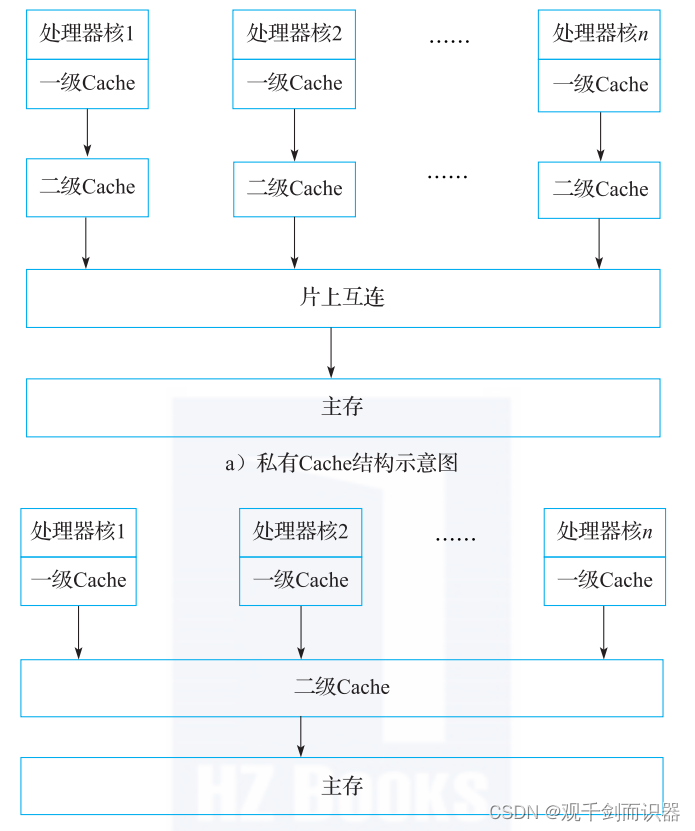

1、通用多核处理器的片上 Cache 结构

主流多核处理器的典型 Cache 结构是: 片内共享最后一级 Cache (Last Level Cache,简称 LLC), 片间共享内存

在共享 LLC 结构中, 主要有 UCA (Uniform Cache Access) 和 NUCA (Non- Uniform CacheAccess) 两种

2、存储一致性模型

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!