Verilog HDL 设计与综合/数字集成电路设计方法概述_part1

仅做笔记整理

课程链接

1.概述

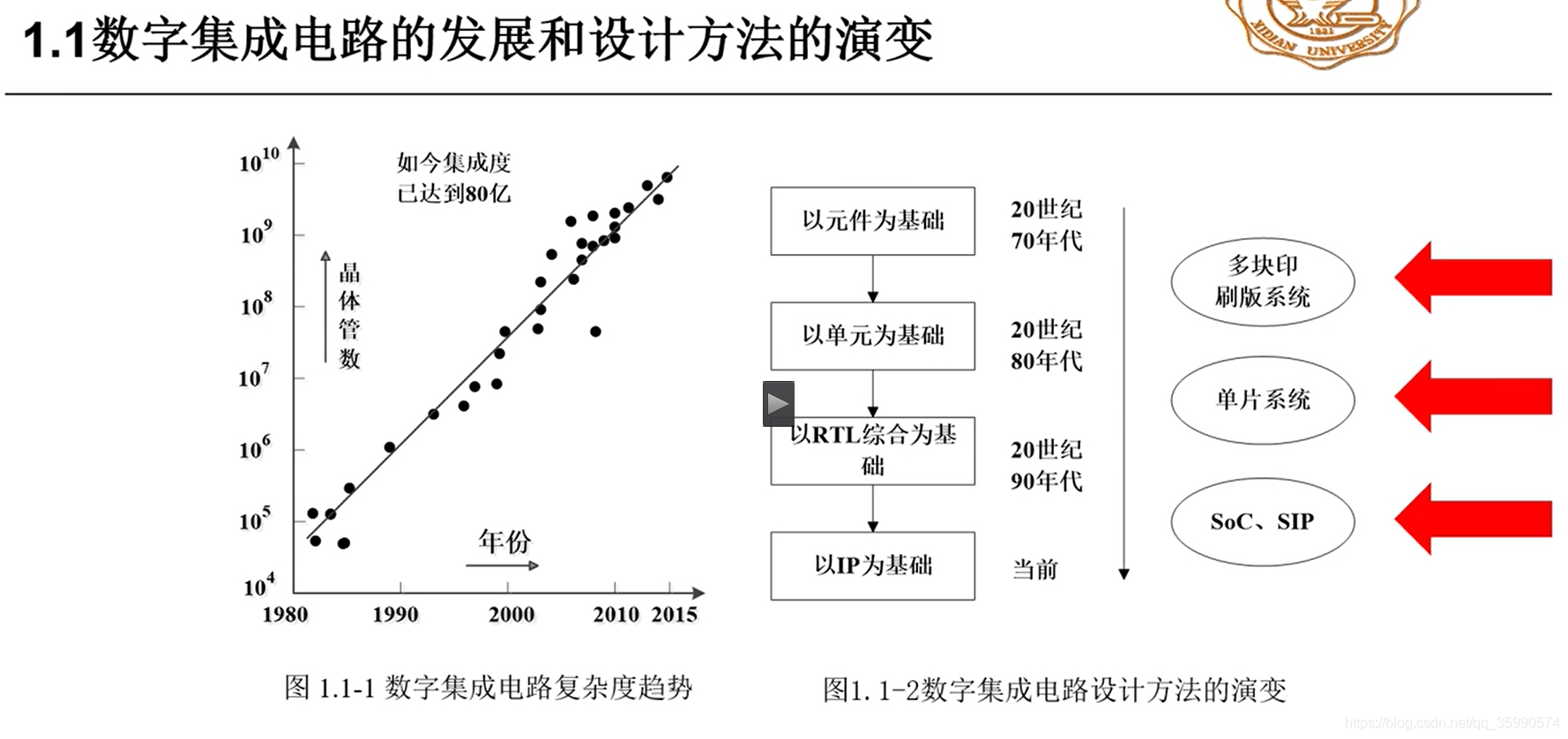

随着时间推移,数字电路设计方式:元件-单元-RTL-IP

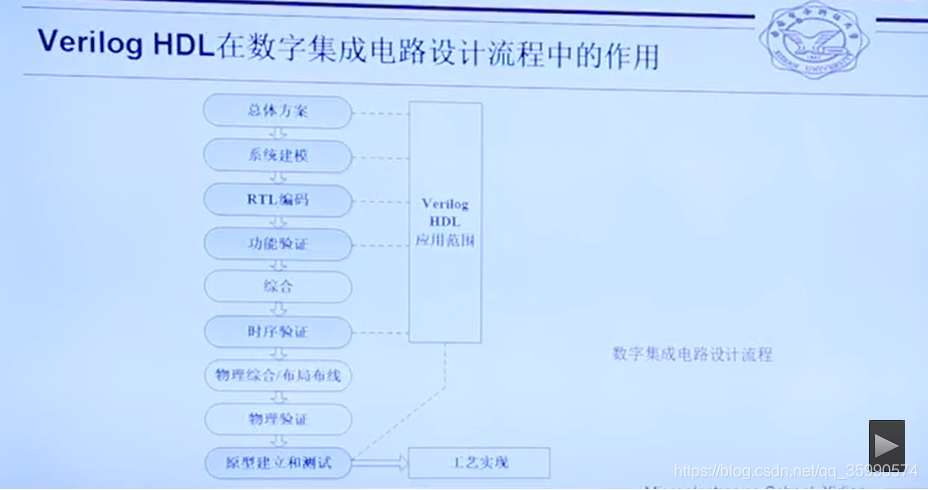

SV是系统级仿真和验证的语言

采用 Verilog HDl语言进行数字集成电路设计的优点在于:

(1)Verilog HDL在硬件描述方面具有效率高、灵活性强的优势;

(2)代码易于维护,可植性强;

(3)测试和仿真功能强大。

2.模块

模块是verilog HDL设计基本单元结构

输入信号 输出信号 输入输出信号

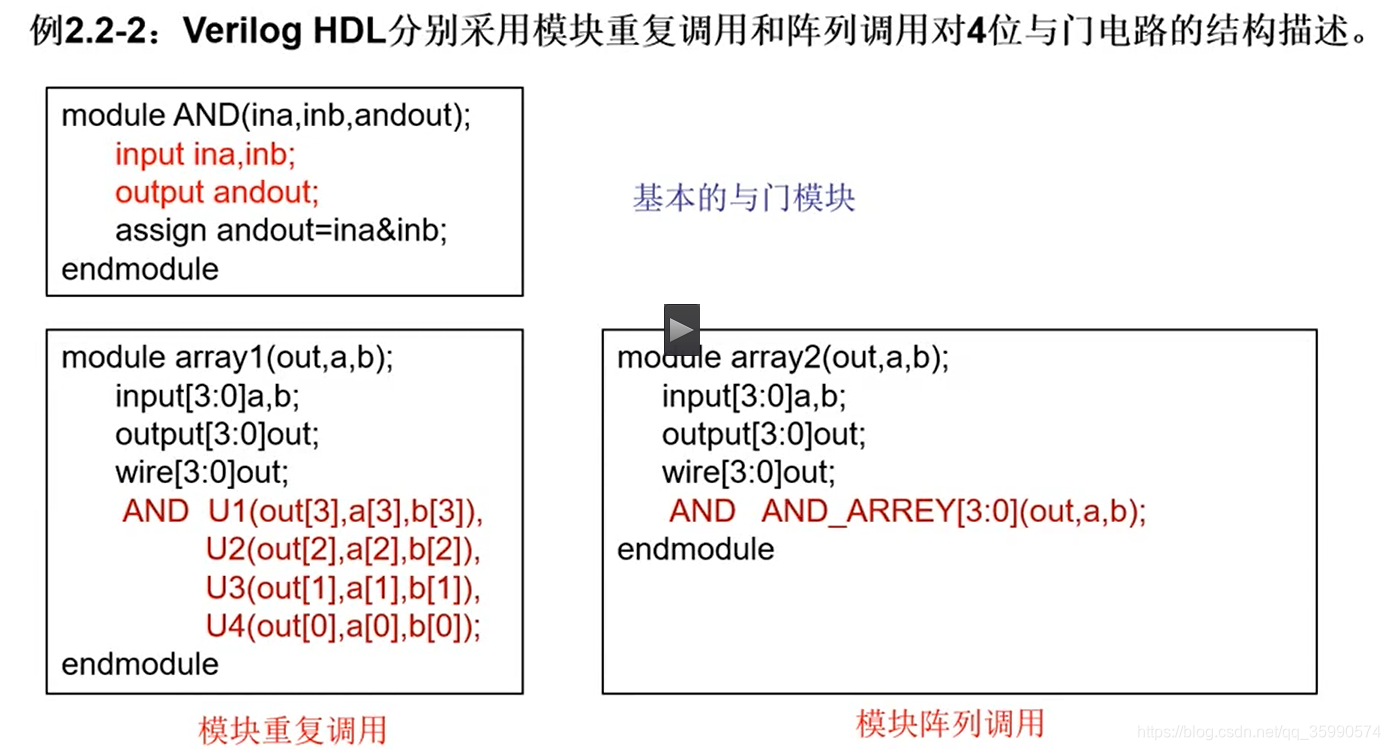

3.模块的调用和结构化建模

硬件描述语言建模方式

(1)数据流建模(2)行为级建模

(3)结构化建模:使用己有的功能化模块,通过调用的方式形成更大规模电路的设计方法,在大型程序设计中使用量大,尤其是系统级电路设计。

根据所调用子模块的不同抽象级别,可以将模块的结构描述方式分成如下三类:

(1)模块级建模:通过调用由用户设计生成的低级子模块来对硬件电路结构进行说明,这种情况下模块由低级模块的实例组成。

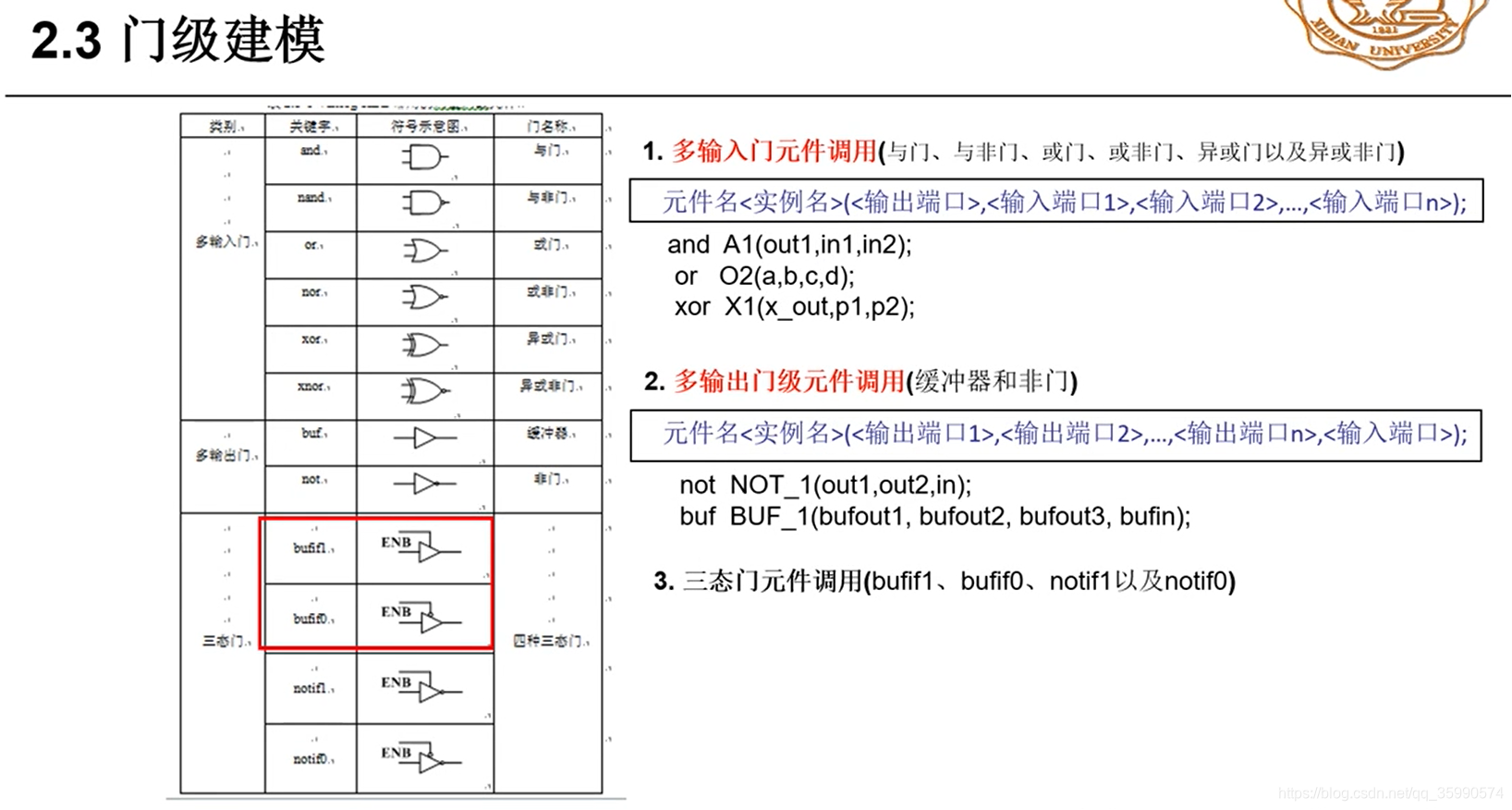

(2)门级建模:通过调用 Verilog HDL内部的基本门级元件来对硬件电路的结构进行说明,这种情况下模块将由基本门级元件的实例组成。

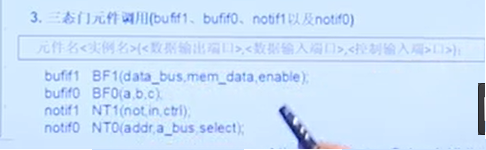

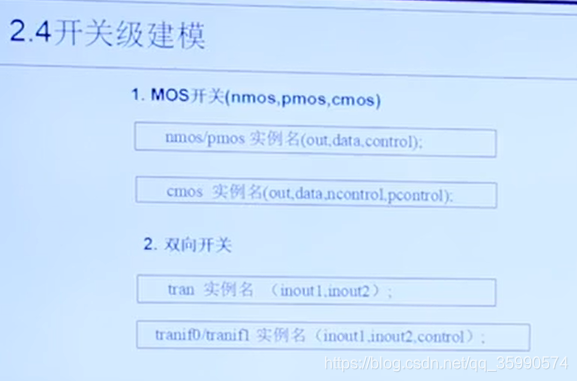

(3)开关级建模:通过调用 erilog HDL内部的基本开关元件来对硬件电路的结构进行说明,这种情况下模块将由基本开关级元件的实例组成。

开关级更为基础和简化(vhdl不支持)

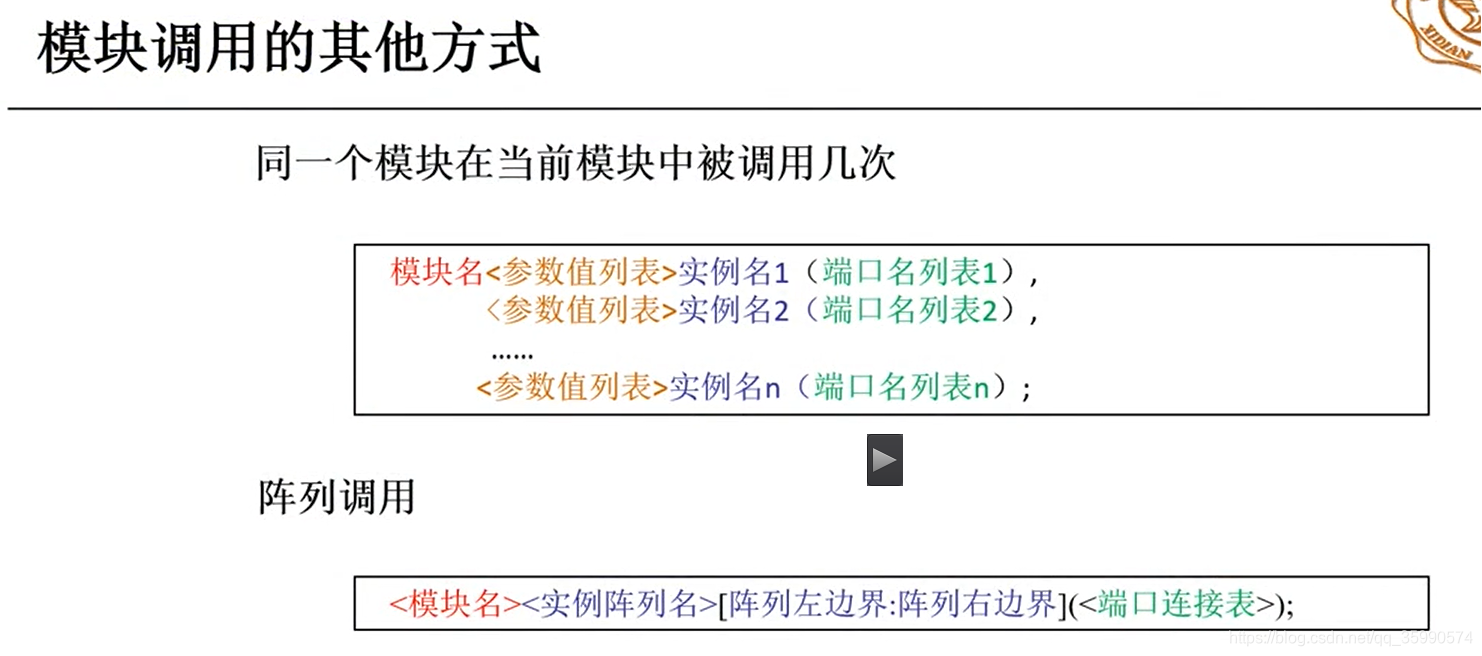

模块调用的其他方式 可以减少代码量

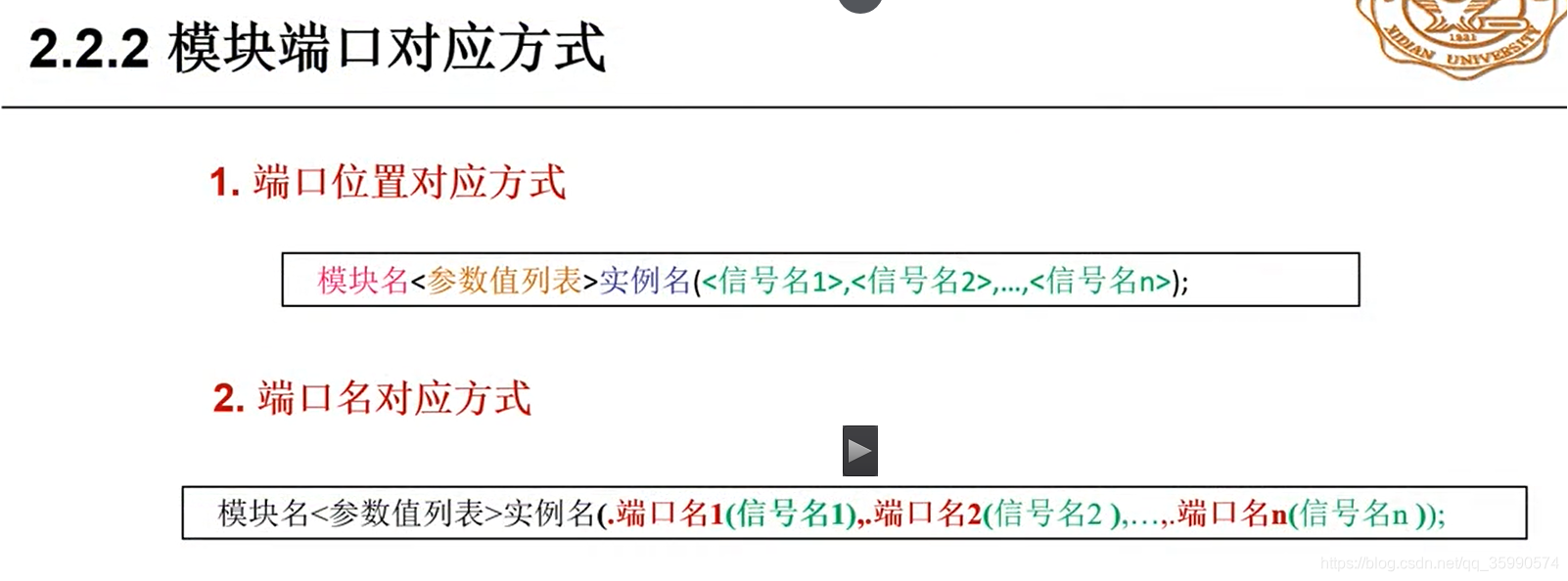

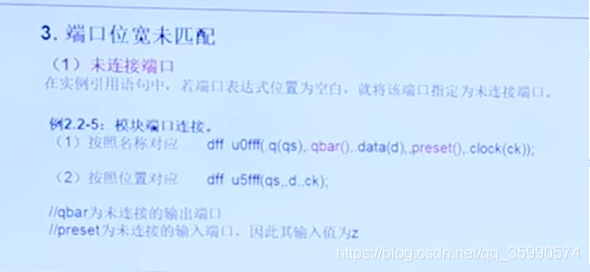

4.模块端口对应方式

注:对于实际应用中,工程师主要采用端口名对应方式,以确保程序的可靠性、

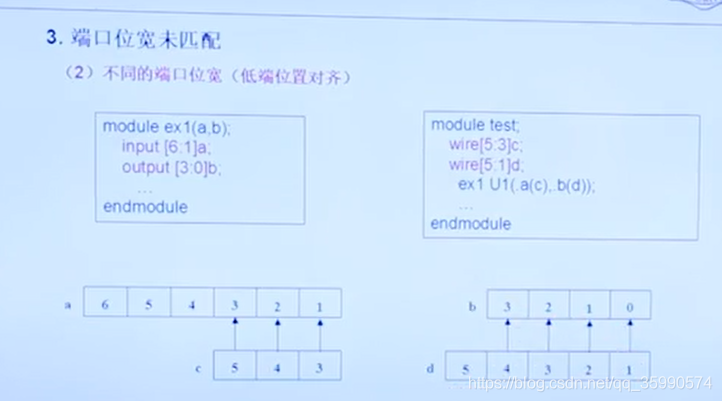

2)不同的断口位宽 (低端位置对齐)

5.门级建模&开关级建模

buf:驱动缓冲,增加驱动能力

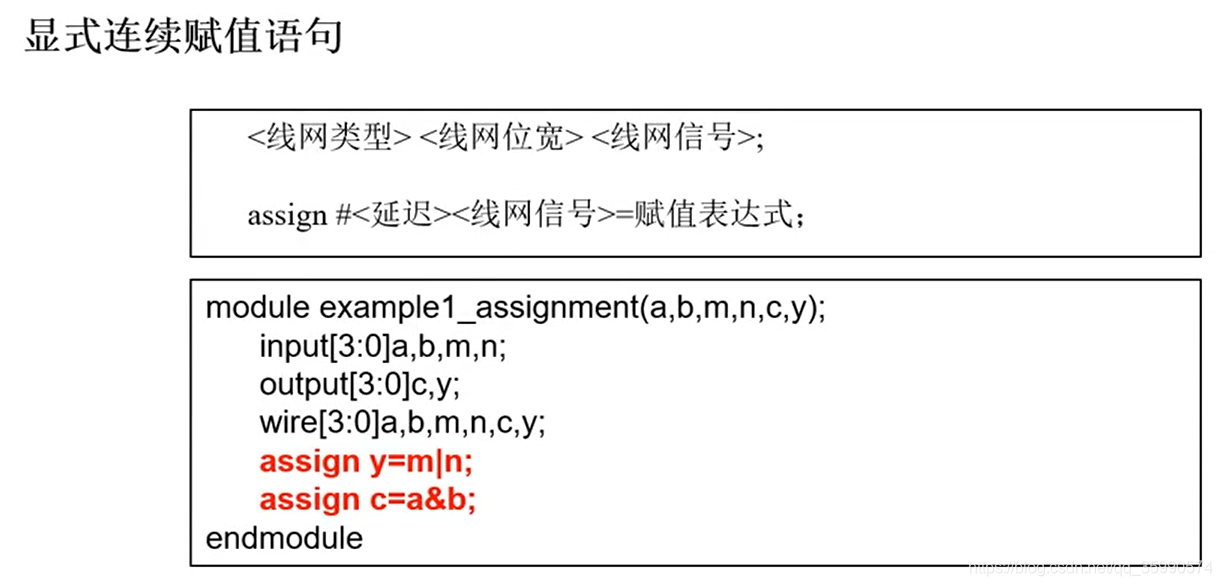

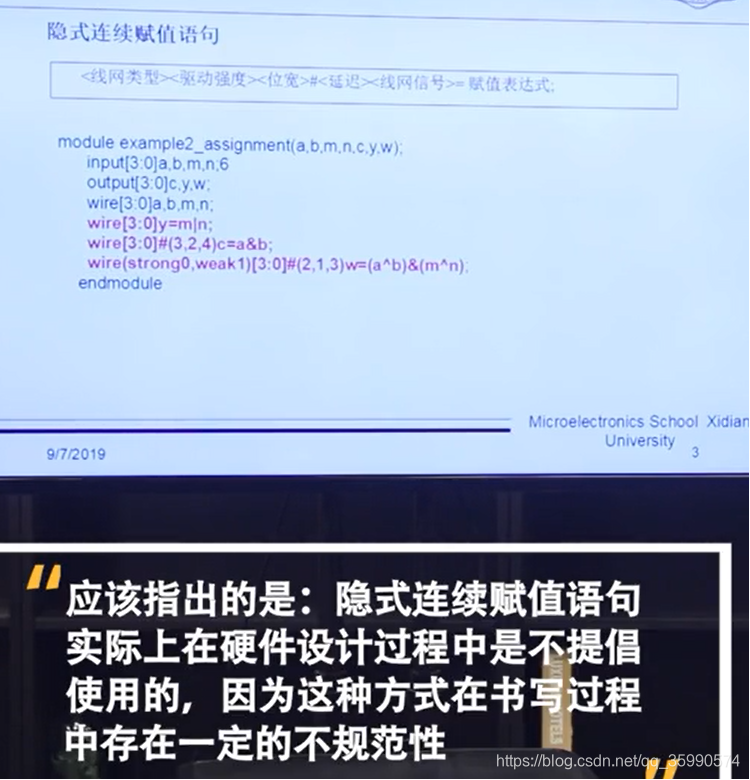

6.连续赋值语句

数据流描述:组合电路

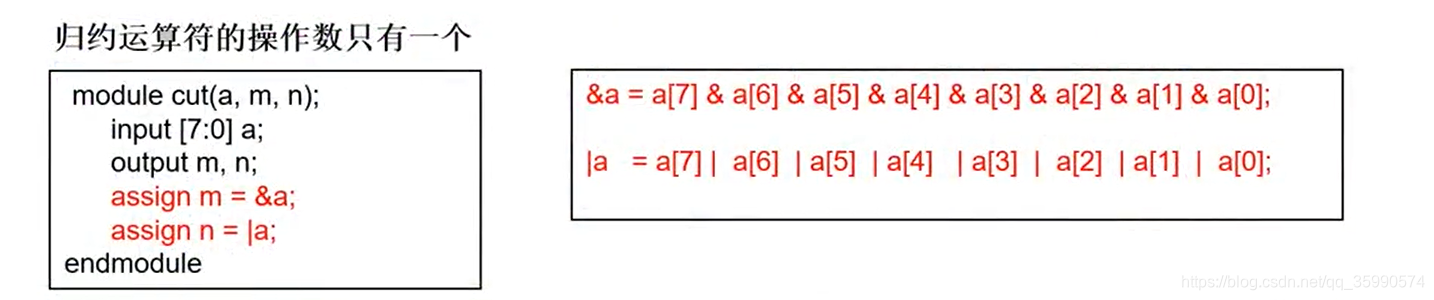

数据流建模:通过连续赋值语句和运算符的建模方式

注

(1)赋值目标只能是线网类型(wire),或者是标量或向量线网的拼接而不能是标量或向量寄存器

(2)连续赋值语句总是处于激活在连续赋值中,只要赋值语句右边表达式任何一个变量有变化,表达式立即被计算,计算的结果立即赋给左边信号(若没有定义延时量) (组合逻辑)

(3)连续赋值语句不能出现在过程块中

(4)多个连续赋值语句之间是并行关系,因此与位置顺序无关

(5)连续赋值语句中的延时具有硬件电路中惯性延时的特性,任何小于其延时的信号变化脉冲都将被滤除掉,不会出现在输出端口上

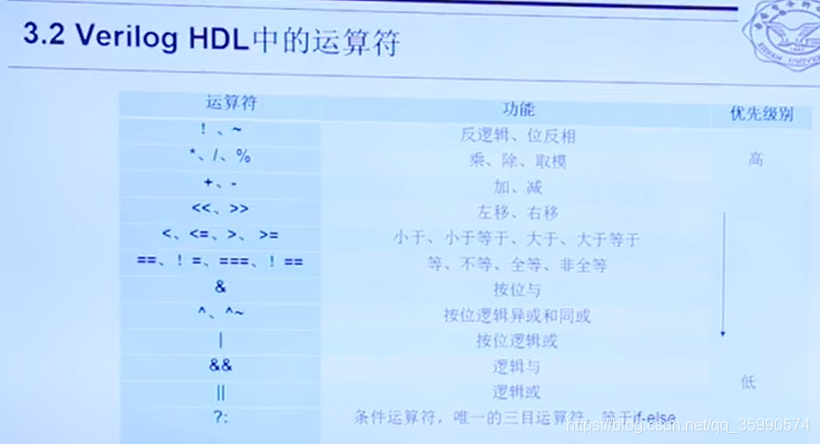

7.VerilogHDL中的运算符

在赋值语句下,算术操作结果的长度由操作左端的目标长度决定

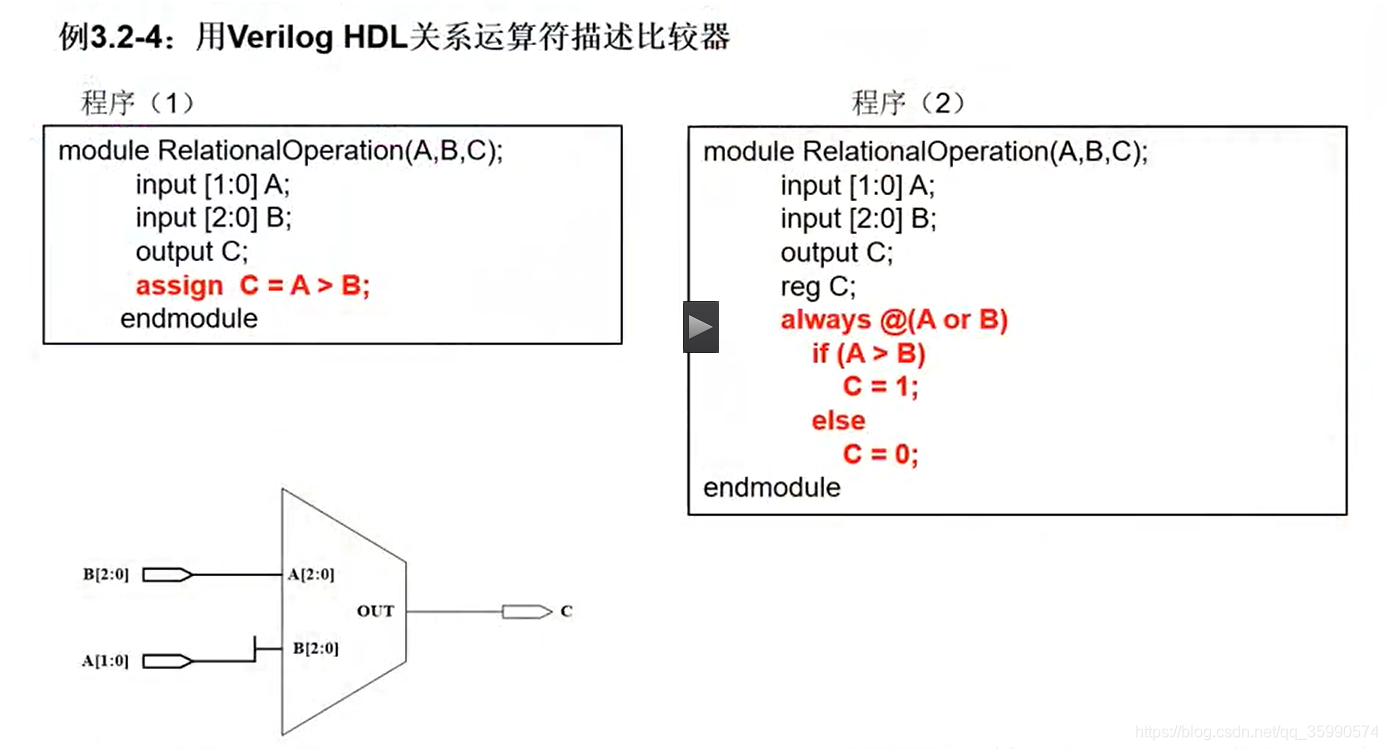

关系运算的结果是一个1bit信号

逻辑运算的结果是一个1bit信号

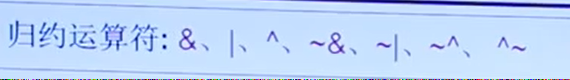

在归约运算符中,单目运算符操作的是一个向量型变量

移位操作符:当信号移出去之后,末端的信号处理只能是补零存在,而在电路使用中一般希望最后一位不是零,而是其他值(所以移位使用不多)

移位运算符实际上很少使用,而连接{}和复制{{ }}运算符在电路形式中则会经常使用

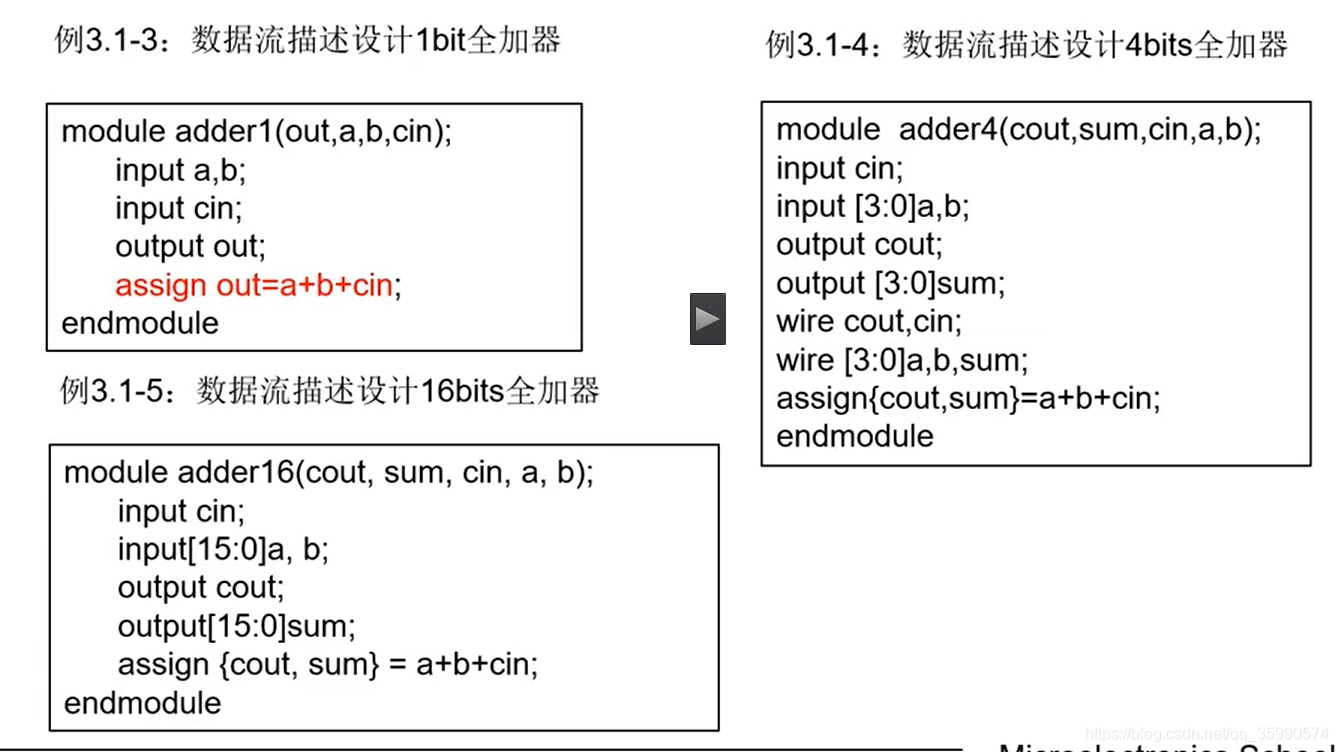

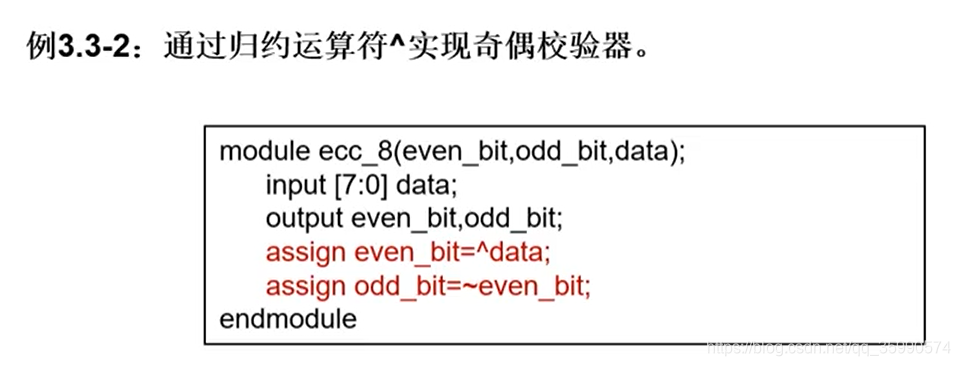

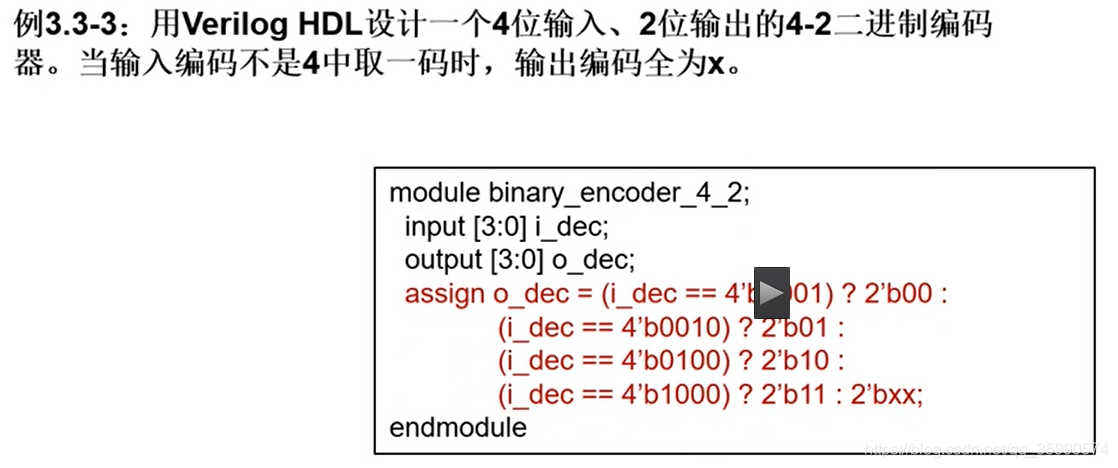

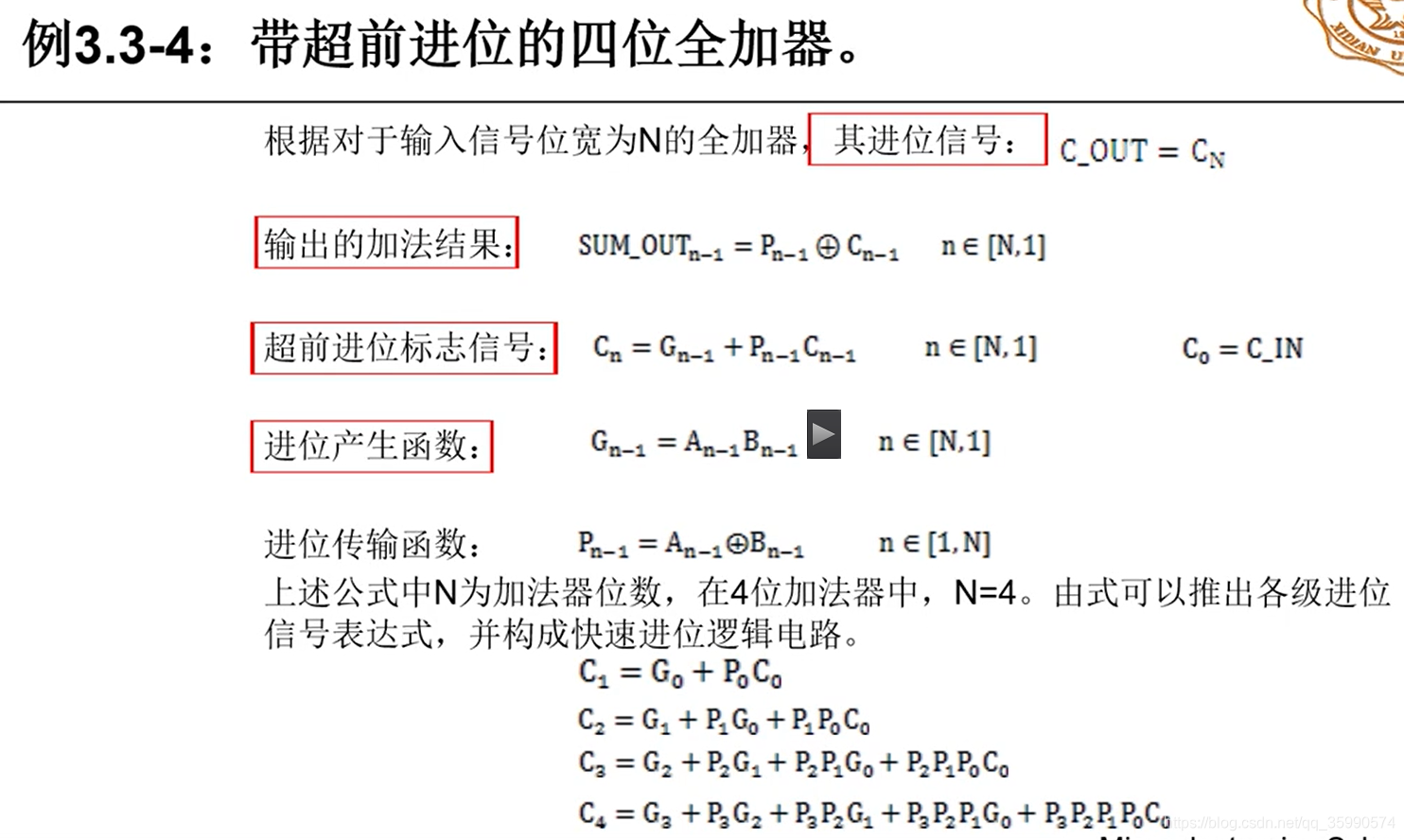

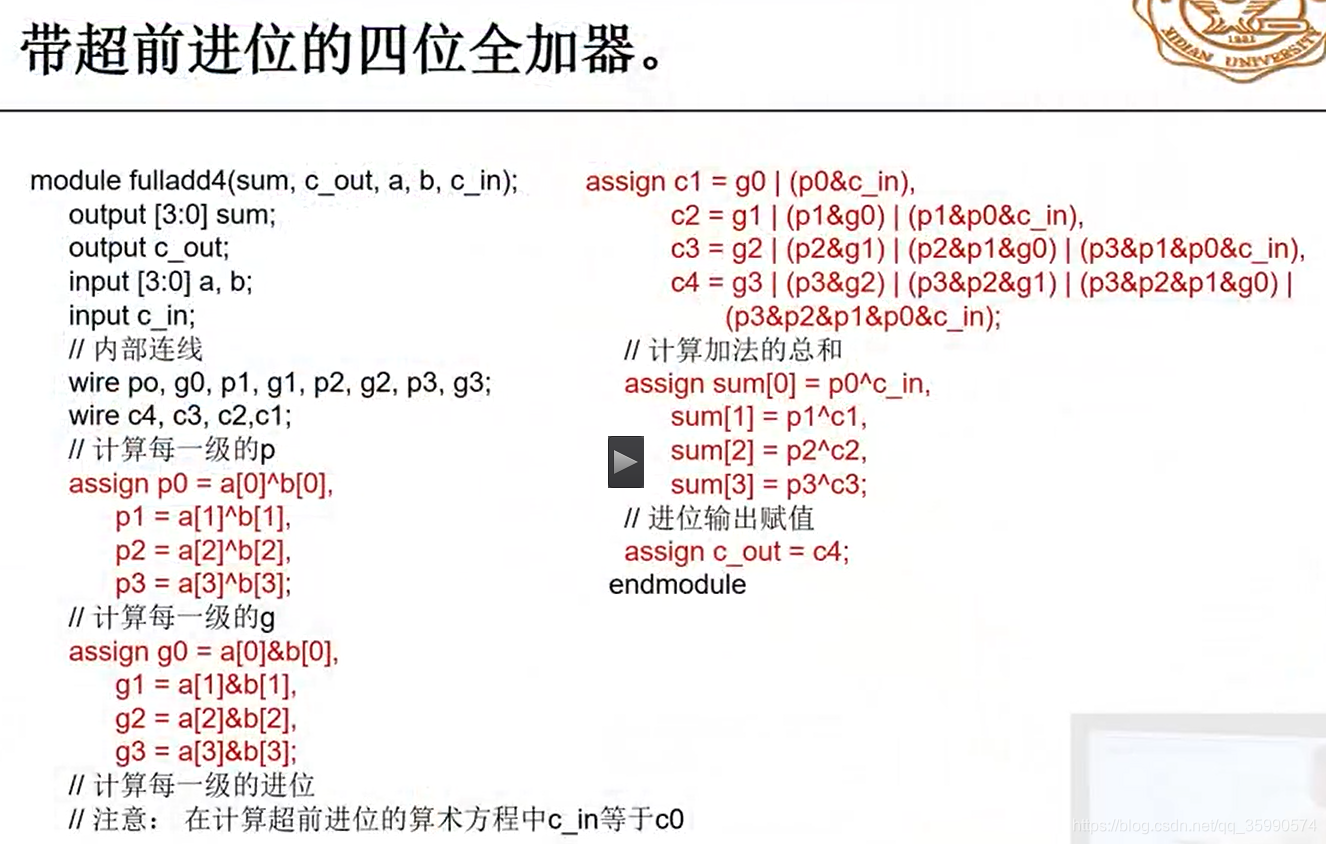

8.Verilog Hdl 数据流建模例程

归约异或:奇校验

等同于嵌套if-else

超前进位加法器的速度会比普通的加法器更快一些,因为它大部分的电路都是并行的

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!