基于FPGA的双目相机目标深度图像提取实现——简略版

目录

一、理论基础

二、核心程序

三、测试结果

一、理论基础

基于FPGA的双目相机目标深度图像提取实现是一种利用双目视觉原理来获取目标深度信息的技术。其基本原理是通过对双目相机获取的图像进行一系列处理,包括图像校正、立体匹配和深度获取等步骤,来得到目标的深度信息。

双目视觉是通过两个相机从不同的角度同时拍摄同一目标,然后根据相机之间的几何关系以及拍摄时的光学参数,将两个图像进行匹配和计算,得到目标的深度信息。其基本原理可以用以下公式表示:

Z = f * (u2 - u1) / (p2 - p1)

其中,Z为目标深度,f为双目相机的焦距,(u1, p1)和(u2, p2)分别为左右相机拍摄的图像中目标在水平和垂直方向上的像素坐标。

在实际应用中,由于双目相机拍摄的图像存在差异,需要进行图像校正,使得两个图像在水平和垂直方向上对齐。然后,通过立体匹配算法,将两个图像中相同的目标点匹配起来,得到视差d。视差与目标深度成反比,即视差越大,目标深度越小。最后,根据视差和相机的几何关系,可以计算出目标的深度信息。

基于FPGA的双目相机目标深度图像提取实现具有实时性和并行处理的优势。FPGA具有高效的并行计算能力和高度可配置的硬件资源,可以大大加速图像处理和计算密集型任务。同时,基于FPGA的实现还可以降低功耗和成本,适合于嵌入式和移动应用等对功耗和体积要求较高的场景。

在实际应用中,基于FPGA的双目相机目标深度图像提取实现需要优化算法和硬件设计,以提高实时性和精度。例如,使用局部匹配算法来减小计算量和提高匹配速度,利用GPU加速立体匹配和深度计算等。此外,还需要考虑相机硬件参数的标定、图像质量、光照条件等因素对目标深度信息提取的影响。

总之,基于FPGA的双目相机目标深度图像提取实现是一种有效的技术,可以实现对目标深度信息的快速、高精度获取。它在机器人视觉、自动化检测、三维重建等领域具有广泛的应用前景。

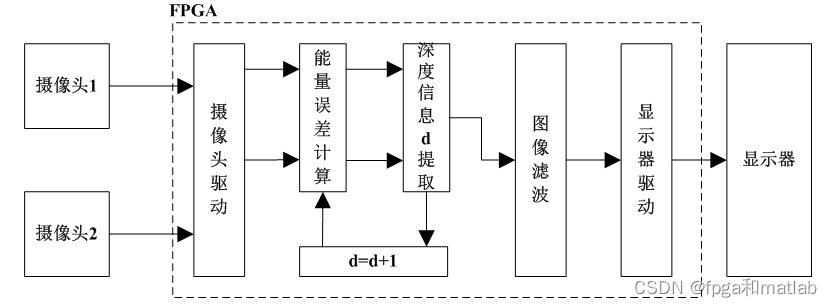

系统的整体框架结构如下图所示:

双目立体视觉模拟了人类双眼感知环境的方式其结构如图2-1所示,主要包括图像采集、摄像机表达、图像校正、立体匹配、及深度获取等五部分构成。

为了使得双目立体视觉能够走出实验室进入到实际应用中,研究者们在优化双目立体视觉系统实时性方面做了许多努力。在这些工作中有一些是基于资源受限的平台如FPGA、DSP或者ASIC等,它们都具有良好的并行计算的能力,并且使用T兼容性很好的局部匹配算法,但是它们的设计都十分复杂,并且具有较长的开发周期。而一些最近的研究确信FPGA是目前较为适合硬件开发的平台P41。在早期的研究中,大部分基于FPGA的平台为了满足实时性W及嵌入式应用的需求,大都使用原理较为简单的基于SAD的算法。而对于PC平台来说,即使是最简单的SAD算法也是不可能满足实时性的需求。然而,对于硬件平台来说,算的速度W及资源的占用是设计的核也内容,而准确性却被忽视了。在这之后,随着立体视觉技术W及FPGA制造工艺技术的发展,越来越多的基于FPGA的平台涌现出来。这些平台使用了更新更有效的算法,但是大部分都没有进行准确性方面的实验和测试。

二、核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 18:11:17 06/08/2018

// Design Name:

// Module Name: deep_image1

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module deep_image19(FCLK_CLK0,gpio_rtl_tri_o_0,Edis0,disparity0,FIFO_M_AXIS_0_tdata,FIFO_M_AXIS_1_tdata,Edis1,disparity1);input FCLK_CLK0;

input gpio_rtl_tri_o_0;

input[15:0]Edis0;

input[15:0]disparity0;

input[23:0]FIFO_M_AXIS_0_tdata;

input[23:0]FIFO_M_AXIS_1_tdata;

output[15:0]Edis1;

output [15:0]disparity1; reg [7:0]R1;

reg [7:0]G1;

reg [7:0]B1;

reg [7:0]Rdelay1;

reg [7:0]Gdelay1;

reg [7:0]Bdelay1;

reg [7:0]Rdelay1a;

reg [7:0]Gdelay1a;

reg [7:0]Bdelay1a;

reg [7:0]Rdelay1b;

reg [7:0]Gdelay1b;

reg [7:0]Bdelay1b;

reg [7:0]Rdelay1c;

reg [7:0]Gdelay1c;

reg [7:0]Bdelay1c;

reg [7:0]Rdelay1d;

reg [7:0]Gdelay1d;

reg [7:0]Bdelay1d;

reg [7:0]Rdelay1e;

reg [7:0]Gdelay1e;

reg [7:0]Bdelay1e;

reg [7:0]Rdelay1f;

reg [7:0]Gdelay1f;

reg [7:0]Bdelay1f;

reg [7:0]Rdelay1g;

reg [7:0]Gdelay1g;

reg [7:0]Bdelay1g;

reg [7:0]Rdelay1h;

reg [7:0]Gdelay1h;

reg [7:0]Bdelay1h;

reg [7:0]Rdelay1i;

reg [7:0]Gdelay1i;

reg [7:0]Bdelay1i;

reg [7:0]Rdelay1j;

reg [7:0]Gdelay1j;

reg [7:0]Bdelay1j;

reg [7:0]Rdelay1k;

reg [7:0]Gdelay1k;

reg [7:0]Bdelay1k;

reg [7:0]Rdelay1l;

reg [7:0]Gdelay1l;

reg [7:0]Bdelay1l;

reg [7:0]Rdelay1m;

reg [7:0]Gdelay1m;

reg [7:0]Bdelay1m;

reg [7:0]Rdelay1n;

reg [7:0]Gdelay1n;

reg [7:0]Bdelay1n;

reg [7:0]Rdelay1o;

reg [7:0]Gdelay1o;

reg [7:0]Bdelay1o;

reg [7:0]Rdelay1p;

reg [7:0]Gdelay1p;

reg [7:0]Bdelay1p;

reg [7:0]Rdelay1q;

reg [7:0]Gdelay1q;

reg [7:0]Bdelay1q;

reg [7:0]Rdelay1r;

reg [7:0]Gdelay1r;

reg [7:0]Bdelay1r; reg [7:0]Rdelay11;

reg [7:0]Gdelay11;

reg [7:0]Bdelay11; always @(posedge FCLK_CLK0 or negedge gpio_rtl_tri_o_0)

beginif(!gpio_rtl_tri_o_0)beginR1 <= 8'd0;G1 <= 8'd0;B1 <= 8'd0;Rdelay1<= 8'd0;Gdelay1<= 8'd0;Bdelay1<= 8'd0; Rdelay1a<= 8'd0;Gdelay1a<= 8'd0;Bdelay1a<= 8'd0; Rdelay1b<= 8'd0;Gdelay1b<= 8'd0;Bdelay1b<= 8'd0; Rdelay1c<= 8'd0;Gdelay1c<= 8'd0;Bdelay1c<= 8'd0; Rdelay1d<= 8'd0;Gdelay1d<= 8'd0;Bdelay1d<= 8'd0; Rdelay1e<= 8'd0;Gdelay1e<= 8'd0;Bdelay1e<= 8'd0; Rdelay1f<= 8'd0;Gdelay1f<= 8'd0;Bdelay1f<= 8'd0; Rdelay1g<= 8'd0;Gdelay1g<= 8'd0;Bdelay1g<= 8'd0; Rdelay1h<= 8'd0;Gdelay1h<= 8'd0;Bdelay1h<= 8'd0; Rdelay1i<= 8'd0;Gdelay1i<= 8'd0;Bdelay1i<= 8'd0; Rdelay1j<= 8'd0;Gdelay1j<= 8'd0;Bdelay1j<= 8'd0; Rdelay1k<= 8'd0;Gdelay1k<= 8'd0;Bdelay1k<= 8'd0; Rdelay1l<= 8'd0;Gdelay1l<= 8'd0;Bdelay1l<= 8'd0; Rdelay1m<= 8'd0;Gdelay1m<= 8'd0;Bdelay1m<= 8'd0; Rdelay1n<= 8'd0;Gdelay1n<= 8'd0;Bdelay1n<= 8'd0; Rdelay1o<= 8'd0;Gdelay1o<= 8'd0;Bdelay1o<= 8'd0; Rdelay1p<= 8'd0;Gdelay1p<= 8'd0;Bdelay1p<= 8'd0; Rdelay1q<= 8'd0;Gdelay1q<= 8'd0;Bdelay1q<= 8'd0; Rdelay1r<= 8'd0;Gdelay1r<= 8'd0;Bdelay1r<= 8'd0; Rdelay11<= 8'd0;Gdelay11<= 8'd0;Bdelay11<= 8'd0; end

else beginR1 <= FIFO_M_AXIS_0_tdata[23:16];G1 <= FIFO_M_AXIS_0_tdata[15:8];B1 <= FIFO_M_AXIS_0_tdata[7:0];Rdelay1 <= FIFO_M_AXIS_1_tdata[23:16];Gdelay1 <= FIFO_M_AXIS_1_tdata[15:8];Bdelay1 <= FIFO_M_AXIS_1_tdata[7:0];Rdelay1a<= Rdelay1;Gdelay1a<= Gdelay1;Bdelay1a<= Bdelay1; Rdelay1b<= Rdelay1a;Gdelay1b<= Gdelay1a;Bdelay1b<= Bdelay1a; Rdelay1c<= Rdelay1b;Gdelay1c<= Gdelay1b;Bdelay1c<= Bdelay1b; Rdelay1d<= Rdelay1c;Gdelay1d<= Gdelay1c;Bdelay1d<= Bdelay1c; Rdelay1e<= Rdelay1d;Gdelay1e<= Gdelay1d;Bdelay1e<= Bdelay1d; Rdelay1f<= Rdelay1e;Gdelay1f<= Gdelay1e;Bdelay1f<= Bdelay1e; Rdelay1g<= Rdelay1f;Gdelay1g<= Gdelay1f;Bdelay1g<= Bdelay1f; Rdelay1h<= Rdelay1g;Gdelay1h<= Gdelay1g;Bdelay1h<= Bdelay1g; Rdelay1i<= Rdelay1h;Gdelay1i<= Gdelay1h;Bdelay1i<= Bdelay1h; Rdelay1j<= Rdelay1i;Gdelay1j<= Gdelay1i;Bdelay1j<= Bdelay1i; Rdelay1k<= Rdelay1j;Gdelay1k<= Gdelay1j;Bdelay1k<= Bdelay1j; Rdelay1l<= Rdelay1k;Gdelay1l<= Gdelay1k;Bdelay1l<= Bdelay1k; Rdelay1m<= Rdelay1l;Gdelay1m<= Gdelay1l;Bdelay1m<= Bdelay1l; Rdelay1n<= Rdelay1m;Gdelay1n<= Gdelay1m;Bdelay1n<= Bdelay1m; Rdelay1o<= Rdelay1n;Gdelay1o<= Gdelay1n;Bdelay1o<= Bdelay1n; Rdelay1p<= Rdelay1o;Gdelay1p<= Gdelay1o;Bdelay1p<= Bdelay1o; Rdelay1q<= Rdelay1p;Gdelay1q<= Gdelay1p;Bdelay1q<= Bdelay1p; Rdelay1r<= Rdelay1q;Gdelay1r<= Gdelay1q;Bdelay1r<= Bdelay1q; Rdelay11<= Rdelay1r;Gdelay11<= Gdelay1r;Bdelay11<= Bdelay1r; end

endreg [7:0]Rd1;

reg [7:0]Gd1;

reg [7:0]Bd1;

reg [15:0]Rdata1;

reg [15:0]Gdata1;

reg [15:0]Bdata1;

reg [15:0]Sdata1;

reg [15:0]ErrorEnergy1; always @(posedge FCLK_CLK0 or negedge gpio_rtl_tri_o_0)

beginif(!gpio_rtl_tri_o_0)beginRd1 <= 8'd0;Gd1 <= 8'd0;Bd1 <= 8'd0;Rdata1 <= 16'd0;Gdata1 <= 16'd0;Bdata1 <= 16'd0; Sdata1 <= 16'd0; ErrorEnergy1 <= 16'd0; end

else beginif(R1>Rdelay11)Rd1 <= R1-Rdelay11;elseRd1 <= Rdelay11-R1;if(G1>Gdelay11)Gd1 <= G1-Gdelay11;elseGd1 <= Gdelay11-G1; if(B1>Bdelay11)Bd1 <= B1-Bdelay11;elseBd1 <= Bdelay11-B1; Rdata1 <= Rd1*Rd1;Gdata1 <= Gd1*Gd1;Bdata1 <= Bd1*Bd1; Sdata1 <= Rdata1+Gdata1+Bdata1;ErrorEnergy1 <= Sdata1;end

endreg [15:0]Edis1;

reg [15:0]disparity1; always @(posedge FCLK_CLK0 or negedge gpio_rtl_tri_o_0)

beginif(!gpio_rtl_tri_o_0)beginEdis1 <= 16'd0;disparity1 <= 16'd0;end

else beginif(Edis0 >= ErrorEnergy1)begindisparity1 <= 16'd19;Edis1 <= ErrorEnergy1;endelse begindisparity1 <= disparity0;Edis1 <= Edis0;end end

endendmodule三、测试结果

点击run之后,程序就下载到FPGA开发板中了。

A23-44

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!