vivado的vio怎么使用_Xilinx Vivado 硬件诊断( ila和vio的使用)

作者:OpenS_Lee

1背景知识

在我们的FPGA设计项目中,硬件的诊断和校验可能会占去超过30%—40%的FPGA开发时间,FPGA的debug也是FPGA设计中重要的一环。掌握并灵活运用FPGA设计工具的debug功能也是加快FPGA设计的关键。

1.1 ILA(Integrated Logic Analyzer)

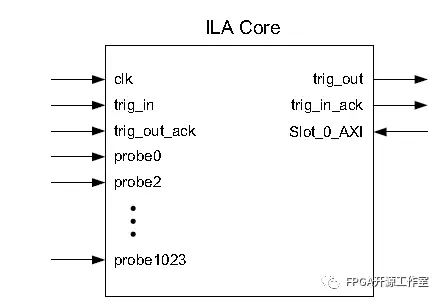

FPGA设计中的信号连接到ILA核的时钟和探针输入如图1。这些信号附加到探针输入,以设计速度采样,并使用片上块RAM(BRAM)存储。核参数指定探针的数量、跟踪样本深度和每个探针输入的宽度。使用与FPGA的JTAG接口连接的自动实例化调试核心集线器与ILA核进行通信。

图1 ILA Core

1.2 VIO (Virtual Input/Output core)

VIO核是一个可定制的核,可以实时监控和驱动内部FPGA信号。不像ILA核,不需要片上或片外RAM。

VIO核有两种类型的信号:

. Input probes

.Output probes

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!