ARTIX-7 XC7A35T实验项目之三八译码器

刷题推荐

链接: Verilog刷题

1,实验简介

在数字电路中可以根据电路功能的不同分为组合逻辑电路与时序逻辑电路。组合逻辑电路==在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。==而时序逻辑从电路特征上来看,其特点为任意时刻的输出不仅取决于该时刻的输入,而且还与电路原来的状态有关。

组合逻辑电路在电路结构上,不涉及对信号跳变沿的处理,无存储电路,也没有反馈电路,通常可以通过真值表的形式表达出来。时序逻辑电路在电路结构上,不管输入如何变化,仅当时钟上升或下降沿到达时,才有可能使输出发生变化。

2,实验环境

vivado 2019.1

黑金AX7035开发板

3,实验原理

译码器(Decoder)是一种多输入多输出的组合逻辑电路,负责将二进制代码翻译为特定的对象(逻辑电平等),功能与编码器相反。译码器一般分为通用译码器和数字显示译码器两大类。本次实验设计的是通用译码器。

以三八译码器为例,其真值表如下表所示,其中A,B,C为数据输入,OUT为数据输出。

| a | b | c | out |

|---|---|---|---|

| 0 | 0 | 0 | 0000_0001 |

| 0 | 0 | 1 | 0000_0010 |

| 0 | 1 | 0 | 0000_0100 |

| 0 | 1 | 1 | 0000_1000 |

| 1 | 0 | 0 | 0001_0000 |

| 1 | 0 | 1 | 0010_0000 |

| 1 | 1 | 0 | 0100_0000 |

| 1 | 1 | 1 | 0100_0000 |

4,程序设计

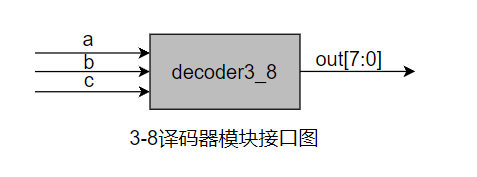

根据真值表可以得到三八译码器模块的接口图及接口功能描述

| 接口名称 | I/O | 功能描述 |

|---|---|---|

| a | I | 数据输入端a |

| b | I | 数据输入端b |

| c | I | 数据输入端c |

| out | O | 数据输出端out |

4.1,vivado工程创建【跳过】

4.2,编写三八译码器的Verilog代码

`timescale 1ns / 1ps

module decoder3_8

(input a,input b,input c,output [7:0] out

);reg [7:0] out;always@(a,b,c)begincase({a,b,c}) // {}为位拼接操作符3'b000:out = 8'b0000_0001;3'b001:out = 8'b0000_0010;3'b010:out = 8'b0000_0100;3'b011:out = 8'b0000_1000;3'b100:out = 8'b0001_0000;3'b101:out = 8'b0010_0000;3'b110:out = 8'b0100_0000;3'b111:out = 8'b1000_0000;endcaseend

endmodule

4.3,vivado仿真验证

1,编写仿真程序,control+s保存好代码;

格式为`timescale 单位 / 精度。例如1ns/100ps,这样再设置延时#100,表示延时100*1ns,并且可以延时100.1ns。

对decoder3_8进行仿真,就需要对输入端口施加激励来观测输出端口的输出波形,与理论的输出波形进行对比,进而判断逻辑代码编写是否正确。在设计文件的输入类型信号,放在仿真文件就需要设置为reg类型;在设计文件的输出类型信号,放在仿真文件就需要设置为wire类型。将设计文件例化到仿真文件中有两种例化方式。第一种方式是调用decoder3_8模块为u1元件名。要求在例化模块中的信号排列顺序要严格与被调用模块的信号排列顺序一致。

decoder3_8 u1(a,b,c,out);

第二种例化方式是调用decoder3_8模块为decoder3_8元件名。

decoder3_8 decoder3_8 (.a(a),.b(b),.c(c),.out(out)

);

`timescale 1ns / 1ns

module decoder3_8;reg a;reg b;reg c;wire [7:0] out;decoder3_8 decoder3_8 (.a(a),.b(b),.c(c),.out(out)initial begina = 0;b = 0;c = 0;#200; //延时200nsa = 0;b = 0;c = 1;#200;a = 0;b = 1;c = 0;#200;a = 0;b = 1;c = 1;#200;a = 1;b = 0;c = 0;#200;a = 1;b = 0;c = 1;#200;a = 1;b = 1;c = 0;#200;a = 1;b = 1;c = 1;#200;//$stop; //停止仿真end

);

endmodule

可以看到如图所示的波形。可以看出输入信号a、b、c每一时刻的状态与仿真文件的赋值一致,输出信号out与理论一致。最终得出逻辑代码复核既定的设计要求。

4.4,添加XDC管脚约束文件【跳过】

因为是组合逻辑电路,不需要对时钟约束。

4.5,下载和Flash固化【跳过】

想加快上电后程序启动,可以在xdc文件添加以下几行代码,目的是为了提高SPI FLASH的读写时钟,其中前面两条设置QSPI FLASH的数据宽度和配置模式,后面一条是配置速度,这个值越大,速度越快。修改好的xdc文件需要重新编译,再次重新生成bit和bin文件。

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!