verilog实现1位2选1数据选择器及数码管数字显示功能以及相应fpga器件开发

verilog实现1位2选1数据选择器及数码管数字显示功能以及相应fpga器件开发

文章目录

- verilog实现1位2选1数据选择器及数码管数字显示功能以及相应fpga器件开发

- 一、实验目的

- 二、实验内容与要求

- 三、实验内容与步骤

- 1. verilog三种方式实现1位2选1数据选择器的功能

- 1.1 结构级建模

- 1.1.1 代码

- 1.1.2 波形

- 1.2 门级建模

- 1.2.1 代码

- 1.2.2 波形

- 1.3 数据流级建模

- 1.3.1 代码

- 1.3.2 波形

- 1.4 Test代码

- 2. FPGA器件开发流程

- 2.1 新建工程

- 2.2 创建新的Verilog源文件

- 2.3 基于Xilinx XST的综合

- 2.4 设计仿真

- 2.5 创建约束

- 2.6 执行设计并生成下载的bit文件

- 四、拓展实验

- 1. 实验内容和要求

- 2. 实验内容和步骤

- 2.1 verilog实现功能

- 2.1.1 代码

- 2.1.2 Test代码

- 2.1.3 波形

- 2.2 FPGA开发

一、实验目的

- 学习使用verilog HDL描述数字逻辑电路与系统的方法;

- 掌握采用可编程逻辑器件实现数字逻辑电路与系统的方法;

- 学习并掌握采用Xilinx_ISE软件开发可编程器件的过程。

二、实验内容与要求

使用ISE软件,通过三种编程方式实现1位2选1数据选择器的功能,并且下载到fpga验证功能;

三、实验内容与步骤

1. verilog三种方式实现1位2选1数据选择器的功能

1.1 结构级建模

1.1.1 代码

`timescale 1ns / 1psmodule select2_1(input wire A,input wire B,input wire sel,output reg o);always @(*) begino = (sel) ? A : B;endendmodule

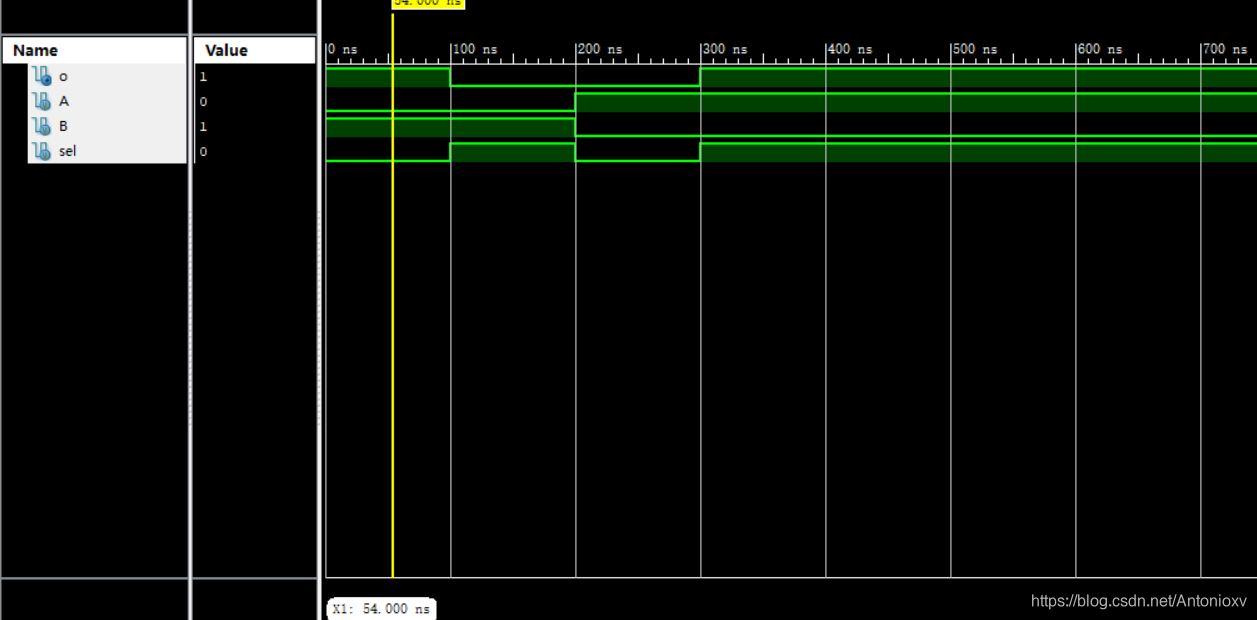

1.1.2 波形

1.2 门级建模

1.2.1 代码

`timescale 1ns / 1psmodule select2_1(input wire A,input wire B,input wire sel,output tri o);bufif1(o, A, sel);bufif0(o, B, sel);endmodule

1.2.2 波形

1.3 数据流级建模

1.3.1 代码

`timescale 1ns / 1psmodule select2_1(input wire A,input wire B,input wire sel,output wire o

);assign o = (sel) ? A : B;endmodule

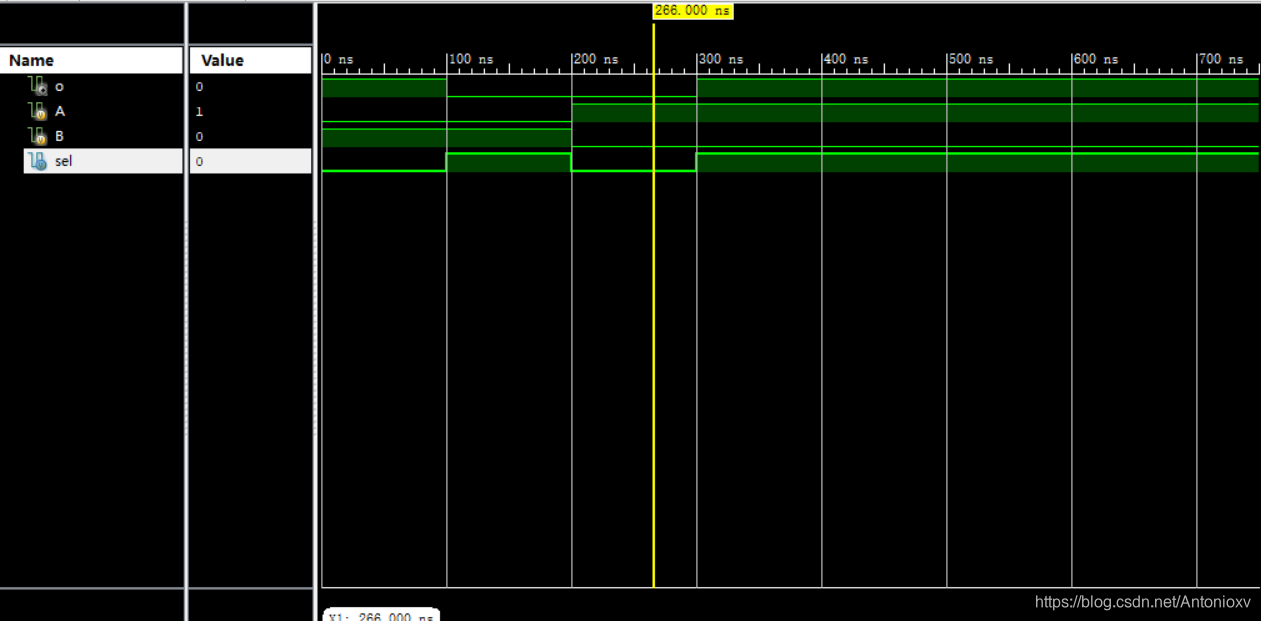

1.3.2 波形

1.4 Test代码

`timescale 1ns / 1psmodule test;// Inputsreg A;reg B;reg sel;// Outputswire o;// Instantiate the Unit Under Test (UUT)select2_1 uut (.A(A), .B(B), .sel(sel), .o(o));initial begin// Initialize InputsA = 0;B = 1;sel = 0;// Wait 100 ns for global reset to finish#100;A = 0;B = 1;sel = 1;// Wait 100 ns for global reset to finish#100;A = 1;B = 0;sel = 0;// Wait 100 ns for global reset to finish#100;A = 1;B = 0;sel = 1;// Wait 100 ns for global reset to finish#100;// Add stimulus hereendendmodule

2. FPGA器件开发流程

2.1 新建工程

须选择与开发板相对应的 FPGA 器件型号,确认项目设定的所有信息准确无误即可finish,否则则需重新设定。

2.2 创建新的Verilog源文件

创建新的verilog文件,确认输入输出的信号,修改完善设计内容,实现我们所需要完成的两输入选择功能,代码见上文。

2.3 基于Xilinx XST的综合

代码写完之后,可进行句法检查。点开Synthesize-xst,双击Check Syntax。如果语法没错,是绿色的打勾,否则会有红色的错误提示。

2.4 设计仿真

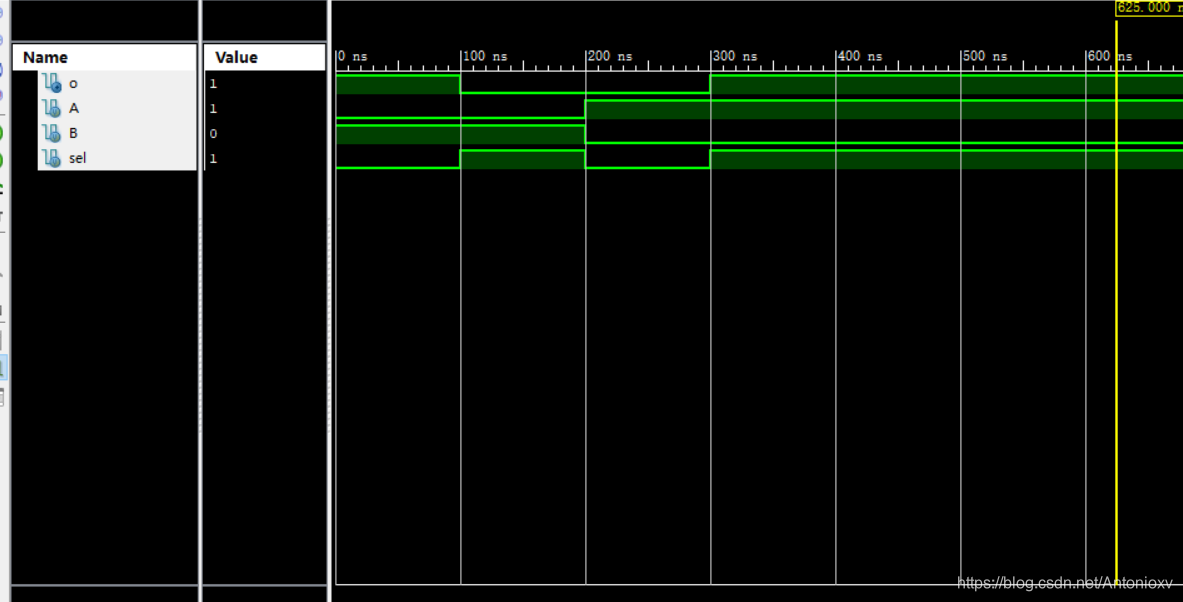

当检查输入源程序句法没有错误后,一般在设计综合之前做行为仿真,以验证代码的行为功能是否正确,利用测试模板( Testbench )来进行。

由于自动生成的Testbench 并不能满足我们所需要的所有测试情况要求,所以重新改写Testbench,使之达到我们的需求。

保存test.v。打开ISE仿真器,得到仿真结果,将图形界面缩放到合适大小,截图见上文。

2.5 创建约束

采用图形化界面设置的方式进行约束,将各个端口与fpga的管脚准确地约束在一起,并保存ucf文件。

2.6 执行设计并生成下载的bit文件

将设计并生成下载的bit文件下载到实验板上,进行实验验证,由授课老师验收。

四、拓展实验

1. 实验内容和要求

- 使用verilog语言实现3-8译码器,并在数码管上显示一位十进制数字的功能;

- 使用Xilinx_ISE软件和fpga开发板实现显示功能。

2. 实验内容和步骤

2.1 verilog实现功能

2.1.1 代码

`timescale 1ns / 1psmodule BinToDec(input LE,input BL_,input LT_,input AN0,input DP_,input [3:0] D,output reg [6:0] L);

/*说明:

输入端:LE BL_ LT_决定74HC4511的工作状态,[3:0]D只有前十个数能够得到相应的输出,其余全部是无效输出;

输出端:[6:0]L从高位到低位分别代表了a-g,决定灯的亮与灭,低电平有效。

*/always @(*) beginif (LE==0&&BL_==1&<_==1&&AN0==0&&DP_==0) begin // AN0 == 0case(D[3:0])4'b0000: L[6:0]<=7'b0000001;4'b0001: L[6:0]<=7'b1001111;4'b0010: L[6:0]<=7'b0010010;4'b0011: L[6:0]<=7'b0000110;4'b0100: L[6:0]<=7'b1001100;4'b0101: L[6:0]<=7'b0100100;4'b0110: L[6:0]<=7'b1100000;4'b0111: L[6:0]<=7'b0001111;4'b1000: L[6:0]<=7'b0000000;4'b1001: L[6:0]<=7'b0000100; default L[6:0]<=7'b1111111; endcaseendelse if (LT_==0&&AN0==0&&DP_==0) L[6:0]<=7'b0000000;else if (BL_==0&<_==1&&AN0==0&&DP_==0) L[6:0]<=7'b1111111;else L<=L;//也可以使用else和casex语句

end

endmodule// L[6:0]从高到低对应CA CB CC到CF CG

//AN0 N6 CA L3

2.1.2 Test代码

`timescale 1ns / 1psmodule test;// Inputsreg LE;reg BL_;reg LT_;reg AN0;reg DP_;reg [3:0] D;// Outputswire [6:0] L;// Instantiate the Unit Under Test (UUT)BinToDec uut (.LE(LE), .BL_(BL_), .LT_(LT_), .AN0(AN0), .DP_(DP_), .D(D), .L(L));initial begin// Initialize InputsLE = 0;BL_ = 1;LT_ = 0;AN0 = 0;DP_ = 0;D[3:0] = 4'b0000;#100;LE = 0;BL_ = 1;LT_ = 1;AN0 = 0;DP_ = 0;D[3:0] = 4'b0000;// Wait 100 ns for global reset to finish#100;LE = 0;BL_ = 1;LT_ = 1;AN0 = 0;DP_ = 0;D[3:0] = 4'b0110;// Wait 100 ns for global reset to finish#100;LE = 0;BL_ = 1;LT_ = 1;AN0 = 0;DP_ = 0;D[3:0] = 4'b1000;// Wait 100 ns for global reset to finish#100;LE = 0;BL_ = 0;LT_ = 1;AN0 = 0;DP_ = 0;D[3:0] = 4'b0000;#100;endendmodule

2.1.3 波形

2.2 FPGA开发

根据实操得到开发板数码管显示如下图,待更新。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!