基于DSP+FPGA+AD9238的冲击波超压测试系统设计与实现

对冲击波关键特征参数进行可靠、精确地评估是进行军事行动规划的前提和依据,

测试结果可以为战斗部设计提供参考,也可以为武器弹体材料的研发制造提供有效依据。

近年来,随着集成电子技术与软件系统取得突破性成果,冲击波测试技术获得了稳定的

发展。

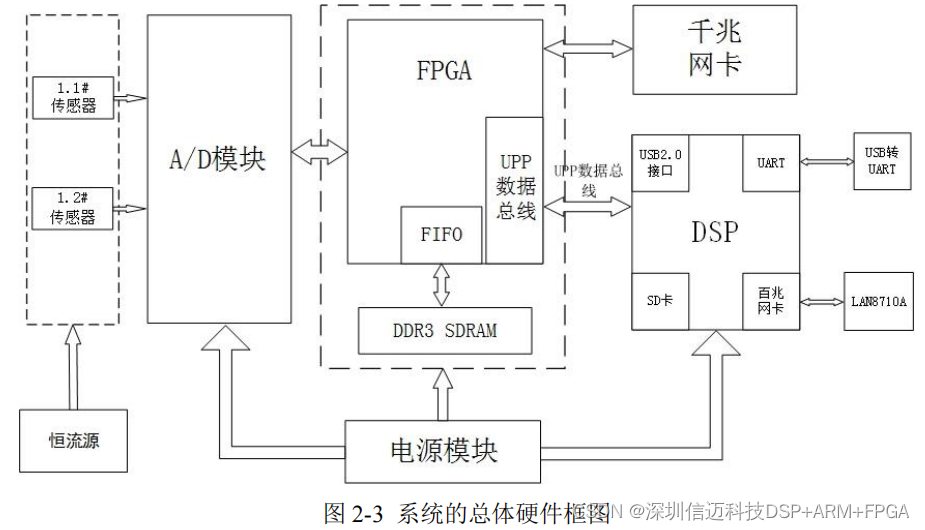

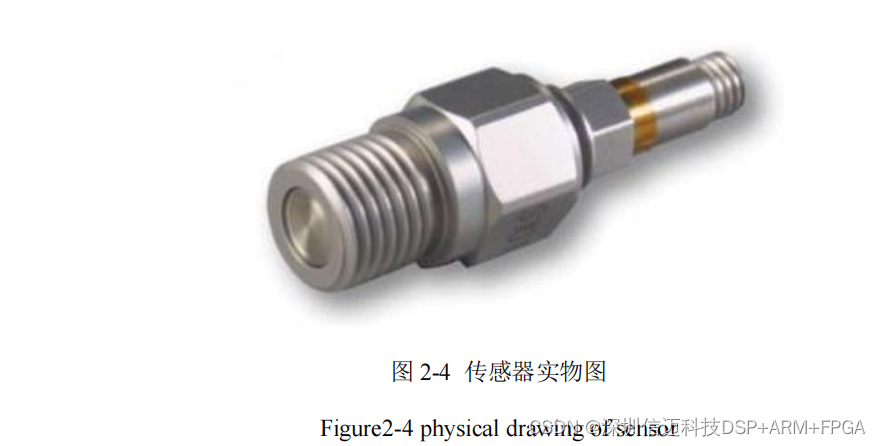

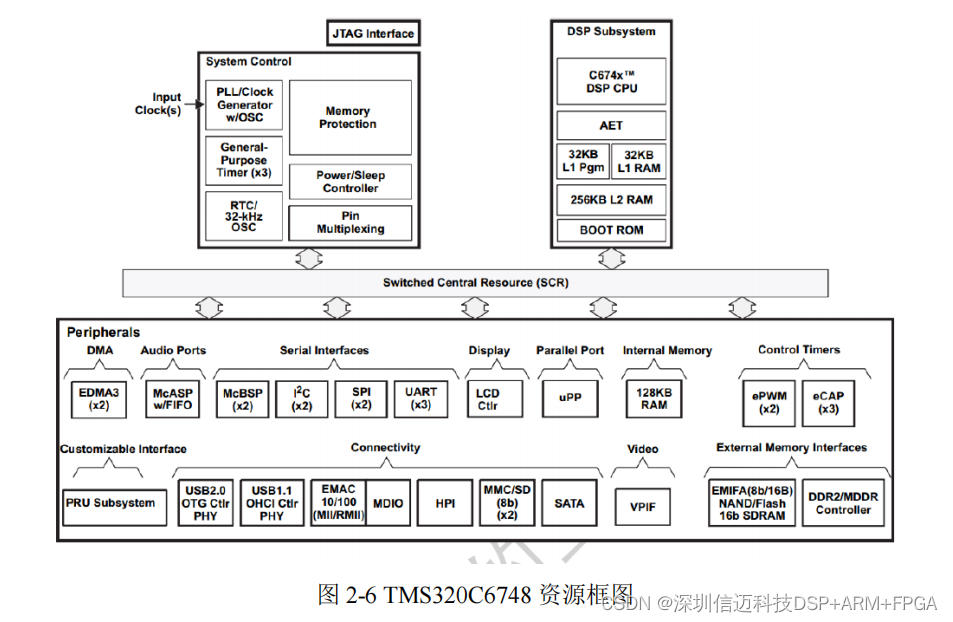

2.2 测试系统的总体框架 2.2.1 系统组成 传统的数据采集系统采用单片机进行软件设计来控制 ADC 进行采集,由于冲击波 测试对系统的实时性要求比较高,基于软件控制的方法无法获得精确的时钟信号,且处 理器速度不足,因此需要采用合适的控制器进行系统设计。 冲击波测试系统需对高频信号进行高速、实时采样,对时钟和数据采集的速率都有 很高要求。现场可编程逻辑门阵列( FPGA )依靠硬件逻辑实现功能,速度可达专用芯片 的速率,且设计过程中可使用内部 PLL 核生成用户想要的任何时钟周期,同时 FPGA 的 硬件并行性使得其可对多通道的冲击波信号同步进行采集,故选用 FPGA 作为系统控制 器。此外 FPGA 具有可编程性,可通过硬件描述语言 Verilog 进行逻辑设计,并根据自 己的功能需求修改程序,灵活性非常高。 FPGA 在本系统中不仅起到控制作用,还通过 逻辑设计达到倍频、数据传输等功能,起到了非常关键的作用。 在 FPGA 控制 A/D 模块进行数据采集后,为使采集结果更加准确,本系统需要对结 果进行实时数据处理。目前常见的控制器如 51 、 ARM 等数据处理能力不足,且外设资 源和外部接口有限,而数字信号处理器( DSP )作为微处理器在结构设计上的优势使得 其在目前信号滤波等各类复杂的数据处理中具有优势。因此本文选择以 DSP 作为系统 的数据解算核心。 相较于使用单片机作为处理器,使用 FPGA 和 DSP 进行数据采集的系统可以完成对 数据高速的采集、处理和传输功能。 FPGA+DSP 系统的最大优势在于其适合于模块化设 计,同时信号处理速度快,实时性高。综上所述,为满足系统要求,设计了采用高速 ADC 、 FPGA 、 DSP 、千兆网卡等模块组成的测试系统,以实现对冲击波超压的采集和传输。 2.2.2 系统结构 本文所设计冲击波测试系统的核心由 FPGA 和 DSP 组成,包括丰富的外设资源,能 够实现对高频信号的高速、实时采样,同时具备强大的数据处理能力,系统的总体结构 如图 2-3 所示。  由图可知,该系统可实现在线与离线两种采集方式,传感器输出的信号送入 AD9238 芯片后,在 FPGA 的控制下进行模数转换,在线采集时 FPGA 控制 DDR3 SDRAM 缓存 将数据通过千兆网卡接口传输至上位机,离线采集时通过 UPP 数据总线将结果输送至 DSP 中进行处理,并将处理后的数据通过 USB2.0 、百兆网卡等接口将传输到上位机进 行进一步的处理或存储至 SD 卡。 主要包括的模块有: ( 1 )传感器部分:作为一种检测装置其主要作用是对冲击波超压信息进行检测。 (2) A/D 模块:将传感器采集的信号进行模数转换。 (3) FPGA 模块: FPGA 作为该测试系统同步采集的核心,主要作用是控制 A/D 模 块的双通道数据同步进行转换及 DDR3 SDRAM 、千兆网卡、 UPP 总线的逻辑控制。 (4) DSP 模块:其主要作用是接收 UPP 总线发送的信息,并对其做相应的处理, 然后把结果通过 USB 、百兆网卡接口发送出去或存储至 SD 卡中,从而减轻 FPGA 处理 器的压力。 (5)千兆网卡模块:将 DDR3 SDRAM 中缓存的数据高速传输至上位机。 2.3 主要模块的选型 2.3.1 传感器型号选择 传感器作为一种检测装置能够对外界信息进行感应,本系统所选择的传感器需要对 冲击波信号进行检测,然后将其转换为电信号输入至系统,因此传感器的性能优良直接 影响到系统的测试性能。 常见的应变式传感器固有频率高,对高频信号进行采集时采集到的数据可能会发生 畸变甚至有很大的偏差。此外冲击波测试环境复杂,爆炸产生的高温和强光易使压阻式 传感器产生漂移。故冲击波压力测试大多采用压电式传感器。 本文选用美国 PCB 公司生产的 ICP 压电式传感器进行测试,其虽对电缆的电容和噪 声要求比较高,但具有灵敏度高、固有频率高、温漂小、信噪比高等优点 [33] ,满足冲击 波测试要求。本系统选择了 102B15 、 102B16 系列的传感器。实物图如图 2-4 所示。

由图可知,该系统可实现在线与离线两种采集方式,传感器输出的信号送入 AD9238 芯片后,在 FPGA 的控制下进行模数转换,在线采集时 FPGA 控制 DDR3 SDRAM 缓存 将数据通过千兆网卡接口传输至上位机,离线采集时通过 UPP 数据总线将结果输送至 DSP 中进行处理,并将处理后的数据通过 USB2.0 、百兆网卡等接口将传输到上位机进 行进一步的处理或存储至 SD 卡。 主要包括的模块有: ( 1 )传感器部分:作为一种检测装置其主要作用是对冲击波超压信息进行检测。 (2) A/D 模块:将传感器采集的信号进行模数转换。 (3) FPGA 模块: FPGA 作为该测试系统同步采集的核心,主要作用是控制 A/D 模 块的双通道数据同步进行转换及 DDR3 SDRAM 、千兆网卡、 UPP 总线的逻辑控制。 (4) DSP 模块:其主要作用是接收 UPP 总线发送的信息,并对其做相应的处理, 然后把结果通过 USB 、百兆网卡接口发送出去或存储至 SD 卡中,从而减轻 FPGA 处理 器的压力。 (5)千兆网卡模块:将 DDR3 SDRAM 中缓存的数据高速传输至上位机。 2.3 主要模块的选型 2.3.1 传感器型号选择 传感器作为一种检测装置能够对外界信息进行感应,本系统所选择的传感器需要对 冲击波信号进行检测,然后将其转换为电信号输入至系统,因此传感器的性能优良直接 影响到系统的测试性能。 常见的应变式传感器固有频率高,对高频信号进行采集时采集到的数据可能会发生 畸变甚至有很大的偏差。此外冲击波测试环境复杂,爆炸产生的高温和强光易使压阻式 传感器产生漂移。故冲击波压力测试大多采用压电式传感器。 本文选用美国 PCB 公司生产的 ICP 压电式传感器进行测试,其虽对电缆的电容和噪 声要求比较高,但具有灵敏度高、固有频率高、温漂小、信噪比高等优点 [33] ,满足冲击 波测试要求。本系统选择了 102B15 、 102B16 系列的传感器。实物图如图 2-4 所示。

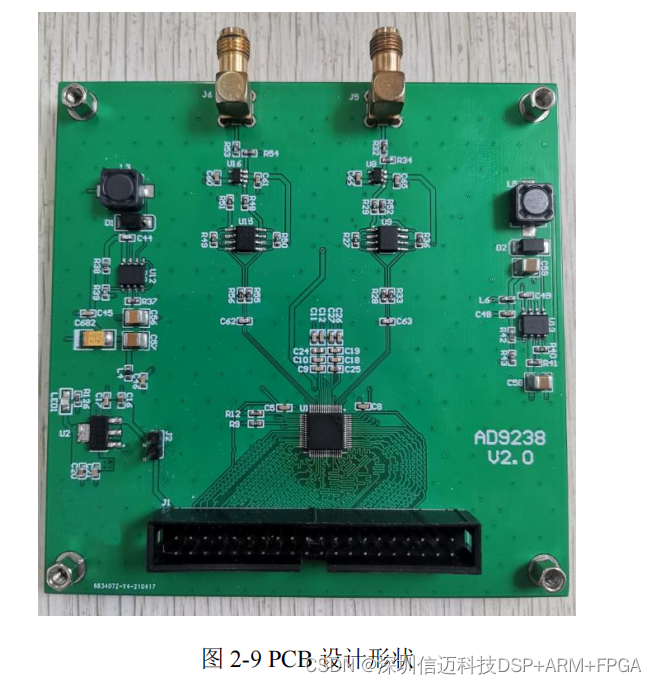

2.4 系统设计原则 本文冲击波测试系统采用模块化的方式进行设计,主要包括 A/D 、 FPGA 、 DSP 和千 兆网卡模块,各模块相互独立,当其中一个模块发生问题或进行升级后可及时更换,设 计中既要考虑系统的功能及结构,也要考虑各模块间的兼容问题。设计原则主要包括以 下几点: (1) 功能可实现原则 功能可实现原则是指冲击波测试系统的功能不仅在技术上是可行的,而且要保证其 能够适应复杂环境,能够实现对冲击波超压的稳定采集。 (2) 结构最优化原则 为方便冲击波超压测试试验,本文将采集系统的各模块制作为 10×10cm 的 PCB 板 并将其堆叠放置,大大减小了系统的占地面积,最终的系统简单便携。其 PCB 设计形状 如图 2-9 所示。

2.4 系统设计原则 本文冲击波测试系统采用模块化的方式进行设计,主要包括 A/D 、 FPGA 、 DSP 和千 兆网卡模块,各模块相互独立,当其中一个模块发生问题或进行升级后可及时更换,设 计中既要考虑系统的功能及结构,也要考虑各模块间的兼容问题。设计原则主要包括以 下几点: (1) 功能可实现原则 功能可实现原则是指冲击波测试系统的功能不仅在技术上是可行的,而且要保证其 能够适应复杂环境,能够实现对冲击波超压的稳定采集。 (2) 结构最优化原则 为方便冲击波超压测试试验,本文将采集系统的各模块制作为 10×10cm 的 PCB 板 并将其堆叠放置,大大减小了系统的占地面积,最终的系统简单便携。其 PCB 设计形状 如图 2-9 所示。  (3) 可靠性原则 由于冲击波测试环境复杂,所采集的信号易受到电磁干扰,进而对数据采集和存储 等环节产生不利影响,此外,冲击波易对系统造成破坏,使系统功能失效。系统的可靠 性是指系统能够适应冲击波试验场的恶略条件,并能够将冲击波超压可靠地采集并存储。 在对系统进行设计时,需尽可能选择可靠的元器件,此外进行 PCB 布线时,要尽量优化 布局,减小干扰误差。

(3) 可靠性原则 由于冲击波测试环境复杂,所采集的信号易受到电磁干扰,进而对数据采集和存储 等环节产生不利影响,此外,冲击波易对系统造成破坏,使系统功能失效。系统的可靠 性是指系统能够适应冲击波试验场的恶略条件,并能够将冲击波超压可靠地采集并存储。 在对系统进行设计时,需尽可能选择可靠的元器件,此外进行 PCB 布线时,要尽量优化 布局,减小干扰误差。 参考链接:omapl138 fpga三核高速数据采集处理核心平台方案_深圳信迈科技DSP+ARM+FPGA的博客-CSDN博客

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!