EDA数字钟设计(verilog)——闹钟模块

源程序:链接:提取码fbd5

闹钟的设置优先级要低于正常示数,所以必须在正常示数时使用闹钟开关才能进行闹钟的设定,而且闹钟的校时校分是用的2Hz的快速校时校分,更加的方便有效,因为是在正常计数下的闹钟设定,所以设定闹钟时时钟依然正常的行走。闹钟将向报时电路输出一个闹钟来了的信号,以便在报时模块中实现闹钟的铃声。具体代码如下:

module alarm(clk_2Hz,naozhong_swh,alarm_hour,alarm_min,hour,minute,hour_reg,min_reg,alarm,swh,baochi_swh);

input clk_2Hz;

input naozhong_swh,baochi_swh; //闹钟开关

input alarm_hour,alarm_min;

input [1:0]swh; //防止出现优先级问题

input [5:0]hour; //时间比较

input [5:0]minute;

output reg[5:0]hour_reg;

output reg[5:0]min_reg;

output reg alarm; always@(posedge clk_2Hz)

beginif((naozhong_swh)&&(swh[1:0] == 'b11)&&(!baochi_swh)) beginif(alarm_hour)beginif(hour_reg == 'd23)hour_reg <= 'd0;elsehour_reg <= hour_reg + 'd1;endif(alarm_min)beginif(min_reg == 'd59)min_reg <= 'd0;elsemin_reg <= min_reg + 'd1;endendendalways@(posedge clk_2Hz)beginif((hour_reg == hour)&&(min_reg == minute)) begin alarm <= 'd1; endelsebegin alarm <= 'd0; endendendmodule

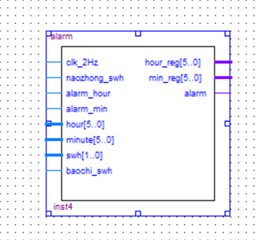

封装图如下:

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!