icg不支持mysql_clock gating | 从ICG cell 在 library 中的定义说起

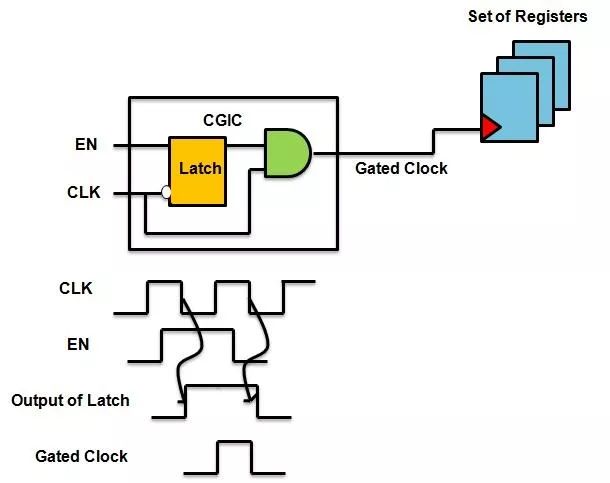

Clock gating 应该算得上IC界十大高频词汇,也是Icer 入行之初最早接触的重要概念之一,但是它并不简单。在数字电路整个设计流程中,它都要被特殊对待,如Coding 时需要考虑什么样的代码风格会使gating 的效率更高;综合时需要特别设置要插入的gating 类型,每个gating 的fanout 范围,是否可以跨层次,是否需要做physical aware 的gating;DFT 时需要确定clock gating 的TE pin 如何连接以保证在DFT 模式clock 可控;P&R 时需要考虑gating 的位置是否合理,是否由于物理上相互拉扯做gating 复制,是否需要人工约束某些关键gating 的位置,CTS 是否需要对gating 做特殊处理;形式验证时需要对gating 做特殊建模;STA时需要明白工具在什么情况下会映射出clock gating 的check, 哪些是真实的clock gating 哪些又是假的clock gating。

目前,网上不乏对clock gating 的描述跟讨论,但驴仍觉得有必要以自己的理解写几篇短文对其做一陈诉。从ICG cell 在library 中的定义说起。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!