Cadence 使用 Integrity 3D-IC 平台实现多小芯片设计

Cadence Design Systems 推出了新的集成 3D 设计规划、实施和系统分析平台,以支持异构多芯片 3D 堆叠设计。

其 Cadence Integrity 3D-IC 平台解决了设计人员在创建超大规模计算、消费、5G 通信、移动和汽车应用时使用 3D 芯片堆叠等先进封装技术所带来的新挑战。

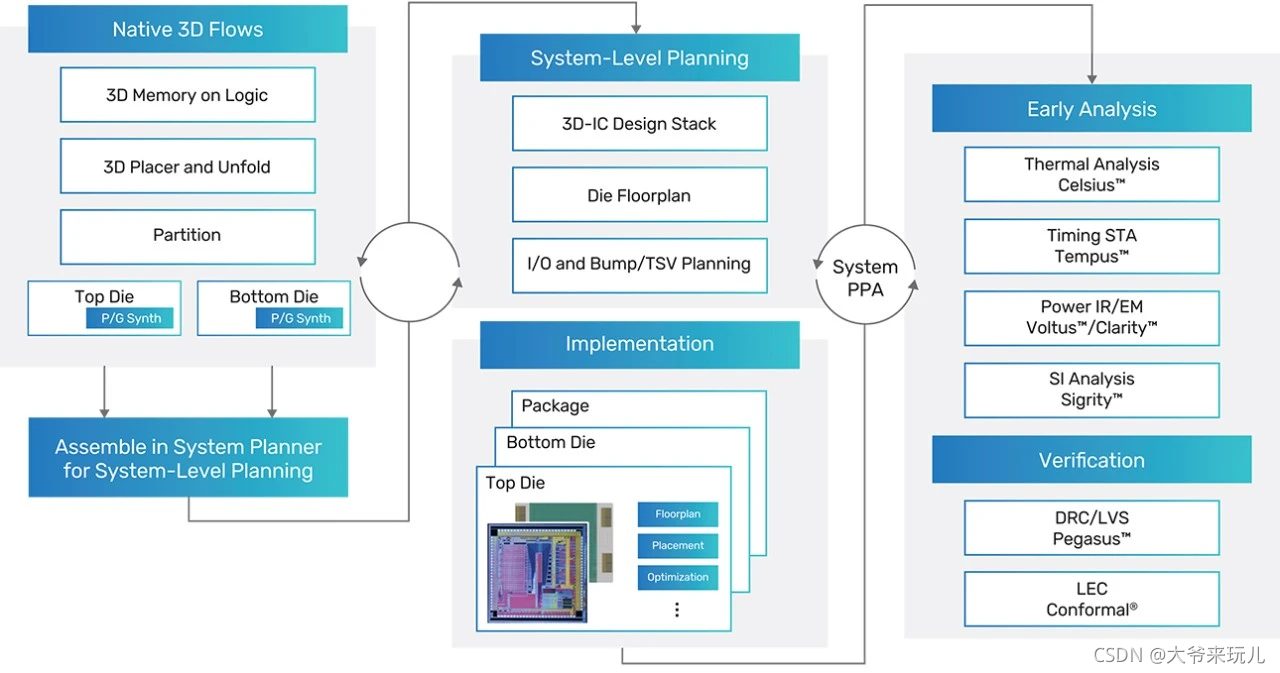

新平台提供了一个统一的驾驶舱,可帮助系统级设计人员规划、实施和分析具有各种封装样式的任何类型的堆叠芯片系统,以提供完整的系统视图以及执行系统驱动的性能优化、功率和面积 (PPA),用于小芯片以及用于 3D-IC 应用的中介层、封装和印刷电路板的协同设计。与使用脱节的逐个芯片实现方法的设计相比,它允许芯片设计人员实现更高的生产力。它提供系统规划、集成电热、静态时序分析 (STA) 和物理验证流程,可实现更快、高质量的 3D 设计收敛。

它还结合了 3D 探索流程,利用 2D 设计网表根据用户输入创建多个 3D 堆叠场景,自动选择最佳的最终 3D 堆叠配置。该平台数据库支持所有 3D 设计类型,让工程师可以同时在多个工艺节点创建设计,并与封装设计团队和使用 Cadence Allegro 封装技术的外包半导体组装和测试 (OSAT) 公司进行无缝协同设计。

在与 Embedded.com 的简报中,Cadence 产品管理组总监 Vinay Patwardhan 表示:“我们接触的大多数客户都是探索 3D 封装 IC 的超大规模公司。挑战在于移动数据的需求很大,但在先进的工艺节点中,我们正在达到物理晶体管尺寸的限制。” 因此,他说进入第三维或 3D 是解决这个问题的一个很好的解决方案,因为它提供更短的电线,使用更少的功率,具有更小的外形和更好的产量,而且它可以满足更高的性能和带宽要求。

然而,3D 芯片设计面临的挑战是芯片放置和凸点规划、SoC 和封装团队在孤岛中工作等问题,并且没有单一的数据库来表示多种技术。额外的系统级验证是另一个挑战,例如来自小芯片的热分析、3D STA 随着签核角数量的激增而成为挑战,以及系统级的芯片间连接验证。

当前的解决方案是脱节的,基于点解决方案,大量文件来回传递,并且没有办法进行探索或提供早期反馈。结果是对堆叠中的单个管芯进行代价高昂的过度设计。

根据 Patwardhan 的说法,这就是该公司的 Integrity 3D-IC 平台的用武之地。该平台具有以下主要特点和优势:

通用驾驶舱和数据库:SoC 和封装设计团队可以同时协同优化整个系统,从而有效地整合系统级反馈。

完整的规划系统: 为所有类型的 3D 设计包含完整的 3D-IC 堆栈规划系统,使客户能够管理和实施原生 3D 堆栈。

无缝实施工具集成:通过与 Cadence Innovus 实施系统的直接基于脚本的集成,为具有 3D 芯片分区、优化和时序流的大容量数字设计提供易用性。

集成系统级分析能力:通过 早期电热和跨芯片 STA 实现稳健的 3D-IC 设计,从而为系统驱动的 PPA 提供早期系统级反馈。

与 Virtuoso 设计环境和 Allegro 封装技术协同设计: 允许工程师通过分层数据库将设计数据从 Cadence 模拟和封装环境无缝移动到系统的不同部分,从而实现更快的设计收敛并提高生产力。

易于使用的界面:包括一个带有流程管理器的强大用户驾驶舱,为设计人员提供了一种统一的交互式方式来运行相关的系统级 3D 系统分析流程。

Cadence 高级副总裁兼数字与签核部门总经理 Chin-Chi Teng 表示:“随着先进封装技术的最新发展,我们看到需要进一步巩固我们成功的 3D-IC 基础,提供更紧密的将我们的实施技术与系统级规划和分析联系起来的集成平台。随着行业继续朝着不同配置的 3D 堆叠芯片发展,新的 Integrity 3D-IC 平台让客户能够实现系统驱动的 PPA,降低设计复杂性并加快上市时间。”

开发通用集成平台的挑战

我们向 Patwardhan 询问了开发 Integrity 3D-IC 平台的挑战。他强调了三个关键领域。“首先是很难找到全流程的专业知识,所以我们让不同的团队聚在一起在集成的通用平台上工作。第二个是创建一个数据库,该数据库提供将节点组合到一个平台中的物理表示。第三,它即将上市:由于 3D-IC 平台仍然是新的,我们必须与代工厂和 OSAT 合作以获得一些标准化。”

他说,Cadence 与 20 多个客户就这个新平台进行了接触。其中之一,imec,纳米电子和数字技术的研究和创新中心,解释了他们如何使用新平台。

imec 3D 系统集成高级研究员兼项目总监 Eric Beyne 表示:“随着 3D-IC 设计的持续发展,越来越需要更有效地自动化 3D 堆叠芯片系统的规划和分区。通过与 Cadence 的长期合作,我们成功地找到了对设计进行分区的自动化方法,以构建具有更高可访问内存带宽的最佳 3D 堆栈,从而在高级节点设计中提高性能并降低功耗。Cadence Integrity 3D-IC 平台中包含的逻辑流上的集成存储器支持跨芯片规划、实施和多芯片 STA,我们的研究团队在多核高性能设计中展示了这一点。”

另一个客户是 Lightelligence Inc;其创始人兼首席执行官沉奕辰表示:“为了通过光计算推动人工智能加速,我们一直在利用芯片设计行业的所有最新创新趋势——多芯片堆叠是一项关键创新。为了构建异构多芯片堆叠设计,拥有一个完全集成的规划和实施系统非常重要,该系统可以在单个驾驶舱中代表多个技术节点。Cadence Integrity 3D-IC 平台提供具有实施和早期系统级分析功能的统一数据库解决方案,包括时序签核和电热分析。它帮助我们使用光学计算进行人工智能加速,实现下一代创新。”

相关实战:https://www.99qibang.cn/information/2d0f8c24eea747a199c757ebf6498980.html

https://www.99qibang.cn/information/2dbda37559ce4df0a1655393f0746682.html

https://www.99qibang.cn/information/8194f79c75c842a19c1587eff07aa131.html

https://www.99qibang.cn/information/cd050fbdebef4a36a88584aa0567e500.html

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!