Verilog经典题(二)——串并转换、序列检测(10010)

文章目录

- 串并转换

- 思路

- 代码

- 波形&总结

- 序列检测(10010)

- 思路

- 代码

- 波形&总结

串并转换

思路

输入din1位、输出dout8位

dout <= {dout[6:0],din}

输入:clk,rst,din

输出:dout

中间寄存器:[7:0]tmp

代码

verilog

module SerialToParallel(input clk,input rst,input din,output [7:0] dout);reg [7:0] tmp;always @ (posedge clk or negedge rst)beginif(!rst)tmp <= 0;else tmp <= {tmp[6:0],din};endassign dout = tmp;

endmodule

tb

module SerialToParallel_tb();parameter [15:0] data = 16'b1010_1101_0101_1011;reg clk;reg rst;reg din;reg [3:0] cout;wire [7:0] dout;initial beginrst = 0;clk = 0;# 15 rst = 1;endinitial beginforever #4 clk = ~clk;endalways @(posedge clk or negedge rst)beginif(!rst) begindin <= 0;//dout <= 0; wire类型不能放到always里cout <= 0;endelse begindin <= data[cout];cout = cout+1;endendSerialToParallel tb1(.clk(clk),.rst(rst),.din(din),.dout(dout));

endmodule

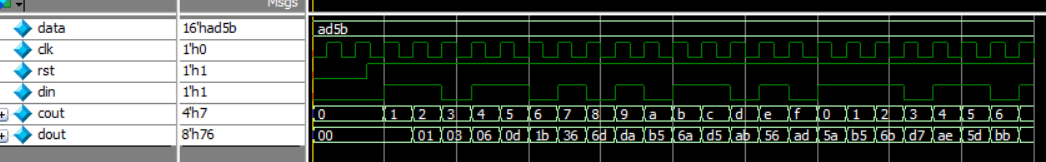

波形&总结

实际情况来说是将一连串的数字改为几位几位的传输,所以输入信号为一个16位甚至更多位的data_in,将data_in在每一时钟取出一位复制给din,data的具体位用count标注即

din <= data[cout]; cout = cout+1;

再与串并转换的代码块相连接。

序列检测(10010)

思路

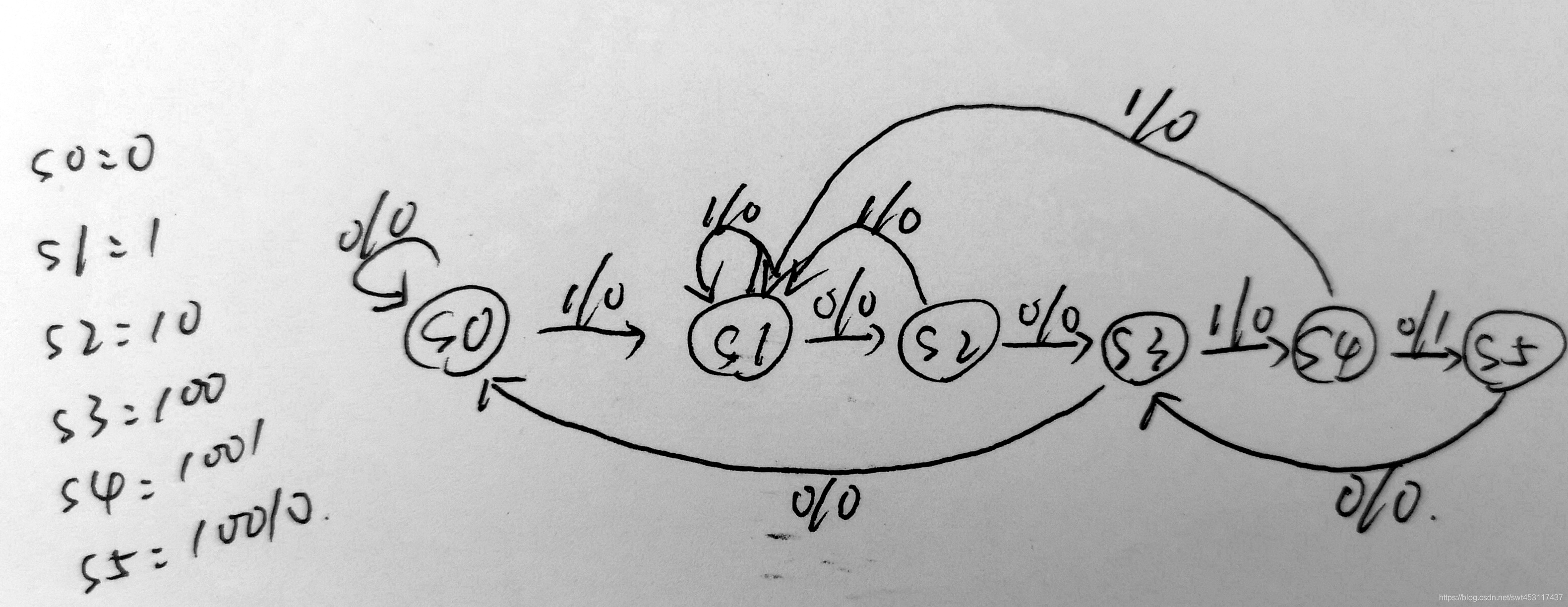

1.画出状态转移图

2.定义好代表每个状态的参数

3.在always里利用case表明状态转移

4.输入:clk,rst,din 输出:dout

中间寄存器:state,nextstate

5.dout = (state == s5) ? 1’b1 : 1’b0

状态转移图

代码

verilog:

module seq_detect(input clk,input rst,input din,output dout);reg [2:0] current_state;reg [2:0] next_state;parameter idle = 3'b000;parameter s1 = 3'b001;parameter s2 = 3'b010;parameter s3 = 3'b011;parameter s4 = 3'b100;parameter s5 = 3'b101;always @(posedge clk or negedge rst) beginif(!rst)current_state <= idle;elsecurrent_state <= next_state;endalways @(*) beginnext_state = idle;case(current_state)idle: beginif(din == 0)next_state <= idle;else next_state <= s1;ends1: beginif(din == 0)next_state <= s2;else next_state <= s1;ends2: beginif(din == 0)next_state <= s3;else next_state <= s1;ends3: beginif(din == 0)next_state <= s0;else next_state <= s4;ends4: beginif(din == 0)next_state <= s5;else next_state <= s1;ends5: beginif(din == 0)next_state <= s3;else next_state <= s1;enddefault: beginnext_state <= idle;endendcaseend//assign dout = (current_state == s5) ? 1'b1 : 1'b0;always @(posedge clk or negedge rst) beginif(!rst) begindout <= 0;endelse begincase(next_state)idle : begindout <= 0;ends1: begindout <= 0;ends2: begindout <= 0;ends3: begindout <= 0;ends4: begindout <= 0;ends5: begindout <= 1;enddefault: begindout<=0;endendcaseendend

endmodule

tb:

module seq_detect_tb();reg clk;reg rst;wire din;wire dout;reg[23:0]data;//=24'b0011_1100_1001_0000_1001_0100;initial beginrst = 0;clk = 0;#10 rst = 1;data = 24'b0011_1100_1001_0000_1001_0100;endinitial begin forever #5 clk = ~clk;endalways @(posedge clk or negedge rst)begin#2 data <= {data[22:0],data[23]};endassign din = data[23];seq_detect tb(.clk(clk),.rst(rst),.din(din),.dout(dout));

endmodule

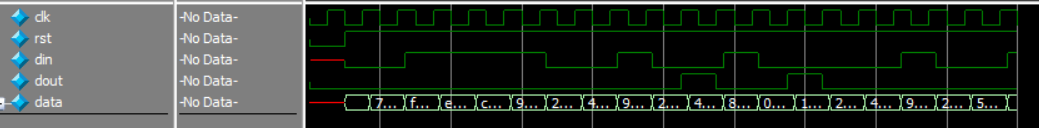

波形&总结

注意将一连串数字每一时钟拿出一位赋予din

always @(posedge clk) begin#2 data <= {data[22:0], data[23]};end

assign din = data[23];*代码参考https://blog.csdn.net/xvrixingkong/category_10393817.html*

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!