D触发器(Verilog)

这是第一篇用Verilog的文章

沿正边沿触发的触发器,包括使能端en

Verilog描述如下

module d_ff(clk, in, en, out);

input clk, in, en;

output reg out;

always @(posedge clk)

if(!en)

out <= 0;

else

out <= in;

endmodule

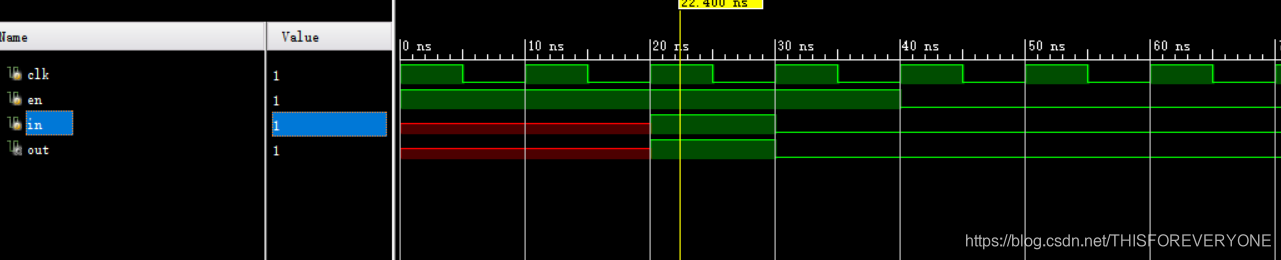

仿真如下

module d_ff_sim();

reg clk, en, in;

wire out;

d_ff u(clk, in, en, out); //这里一定要记着实例化

initial begin

clk = 1; en = 1;

//#10 clk = 1;

#10 en = 1;

#10 in = 1;

#10 in = 0;

#10 en = 0;

end

always //用always语句来模拟时钟变化

//begin#5 clk = ~clk;

//end

endmodule

可以看出D触发器就是当时钟上升沿来临时,输出数据的值是此刻输入数据的值,并一直保持到下一个上升沿来临。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!