SV实验0 DUT设计描述

文章目录

- 一、功能描述

- 二、设计结构

- 三、接口描述

- 四、接口时序

- 五、寄存器描述

- 六、仿真部分代码(.v)

一、功能描述

MCDF(多通道数据整形器,Multi-Channel Data Formatter)

将上行(uplink)多个通道数据经过内部FIFO,并以数据包(data packet)的形式送出。

上行和下行数据的接口协议不同;MCDF有寄存器读写接口,可以支持更多控制功能。

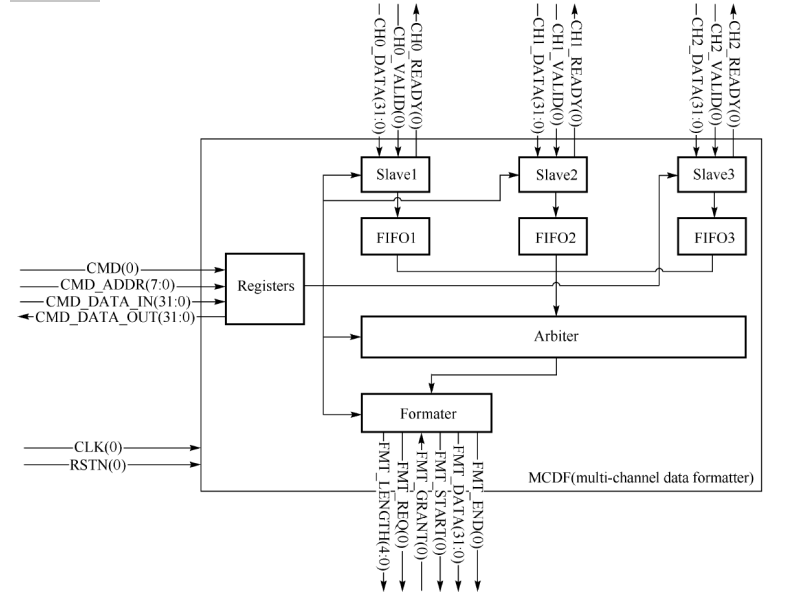

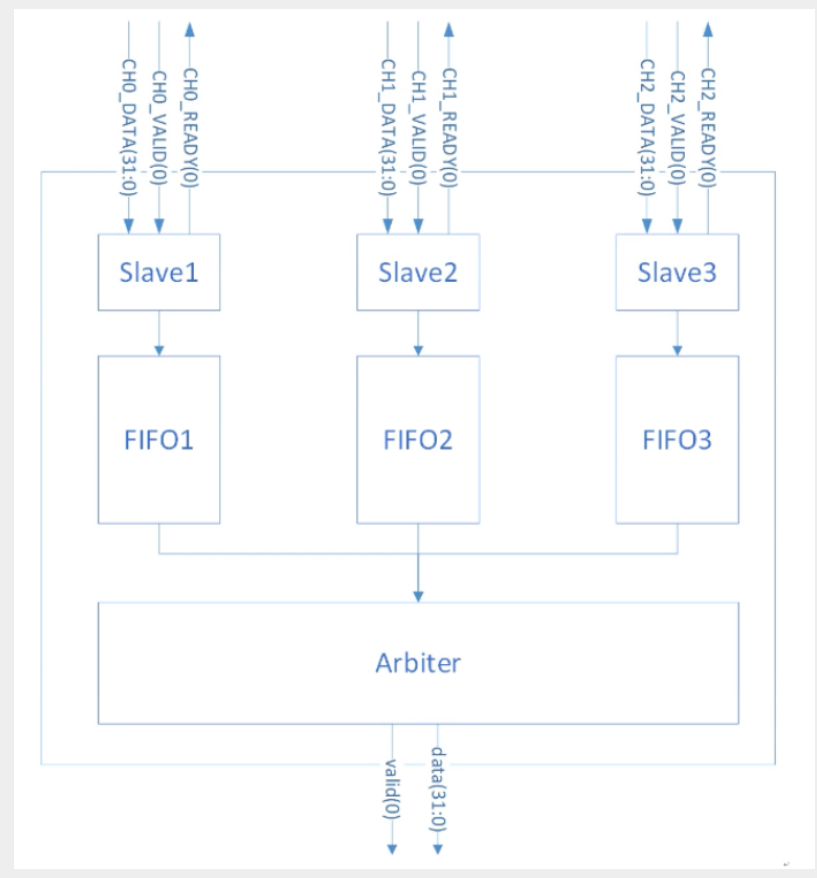

二、设计结构

- Channel Slave(上行数据通道从端) 负责接收上行数据,并存储到对应的FIFO中。

- Arbiter(仲裁器) 可以选择从不同的FIFO中读取数据,并将数据传送至formatter。

- Formatter(整形器) 将数据按一定接口时序送出至下行接收端。

- Control Registers(控制寄存器) 有专用寄存器读写接口,负责接收命令并对MCDF功能做出修改。

三、接口描述

1. System Signal

- CLK(0):时钟信号。

- RSTN(0):复位信号,低位有效。

2. Channel Slave Interface

- CHx_DATA(31:0):通道数据输入。

- CHx_VALID(0):通道数据有效标志信号,高位有效。

- CHx_READY(0):通道数据接收信号,高位表示接收成功。

3. Formatter Interface

- FMT_CHID(1:0):整形数据包的通道ID号。

- FMT_LENGTH(4:0):整形数据包长度信号。

- FMT_REQ(0):整形数据包发送请求。

- FMT_GRANT(0):整形数据包被允许发送的接受标示。

- FMT_DATA(31:0):数据输出端口。

- FMT_START(0):数据包起始标示。

- FMT_END(0):数据包结束标示。

4. Control Registers Interface

- CMD(1:0):寄存器读写命令。

- CMD_ADDR(7:0):寄存器地址。

- CMD_DATA_IN(31:0):寄存器写入数据。

- CMD_DATA_OUT(31:0):寄存器读出数据。

四、接口时序

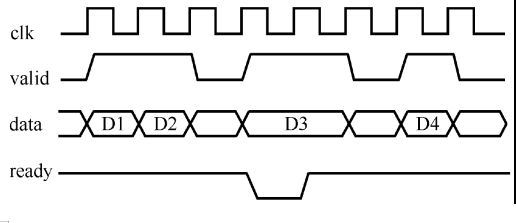

1. Channel Slave 接口时序

- valid为高表示要写入数据。

- ready为高,表示当前时钟周期已将数据写入;ready为低,则需等到ready为高的时钟周期才可写入。

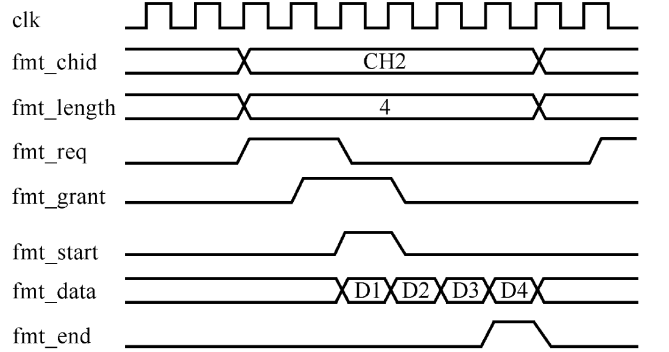

2. Formatter 接口时序

- Formatter按数据包形式发送数据,数据包长度有4、8、16、32。Formatter必须完整发送完某一通道数据包,才可准备发送下一个数据包,在数据包发送期间fmd_chid和fmt_length应保持不变。

- Formatter准备发送数据包时,首先将fmd_req置为高,同时等待接收端的fmt_grant。当fmd_grant变为高时,在下一个周期将fmt_req置为低。fmt_start也必须在接收到fmt_grant高有效的下一个时钟被置为高,且维持一个时钟周期。

- 在fmt_start拉高的同一周期数据开始传送,数据之间不允许有空闲周期,即应连续发送,直到发送完最后一个数据,fmd_end也应置为高且保持一个时钟周期。

- 相邻的数据包之间应保持至少一个时钟周期的空闲,即fmd_end拉低后至少一个时钟周期fmd_req才可再次拉高。

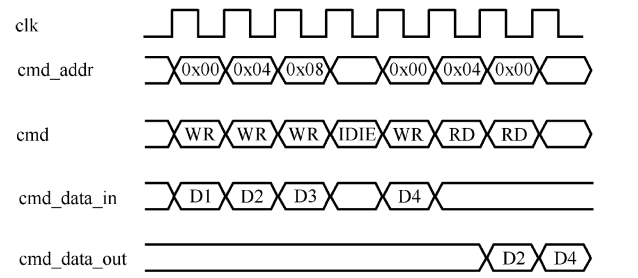

3. Control Registers 接口时序

- Control Registers在每个时钟解析读写命令cmd,当cmd为WR时,把数据cmd_data_in写入到cmd_addr对应的寄存器中;当cmd为RD时,从cmd_addr对应的寄存器中读取数据,并在下一个周期,将数据被驱动至cmd_data_out接口。

五、寄存器描述

- 地址0x00 通道1控制寄存器 32bits 读写寄存器

- 地址0x04 通道2控制寄存器 32bits 读写寄存器

- 地址0x08 通道3控制寄存器 32bits 读写寄存器

| bit | 功能 |

|---|---|

| 0 | 通道使能信号。1为打开,0位关闭。复位值为1。 |

| 2:1 | 优先级。0为最高,3为最低。复位值为3。 |

| 5:3 | 数据包长度,0对应长度4,1对应8,2对应16,3对应32,4~7均暂时对应32。复位值为0。 |

| 31:6 | 保留位,无法写入。复位值为0。 |

- 地址0x10 通道1状态寄存器 32bits 只读寄存器

- 地址0x14 通道2状态寄存器 32bits 只读寄存器

- 地址0x18 通道3状态寄存器 32bits 只读寄存器

| bit | 功能 |

|---|---|

| 7:0 | 上行数据从端FIFO的可写余量,同FIFO的数据余量保持同步变化。复位值为FIFO的深度数。 |

| 31:8 | 保留位,复位值为0。 |

六、仿真部分代码(.v)

MCDT为MCDF子模块,仅包含Channel_slave和Arbiter部分。

Verilog实现的Testbench如下:

`timescale 1ns/1psmodule tb1;

// 模块端口定义和例化省略...initial begin // 时钟周期10nsclk <= 0;forever begin#5 clk <= !clk;end

endinitial begin // 在10~110ns内触发复位#10 rstn <= 0;repeat(10) @(posedge clk);rstn <= 1;

endinitial begin @(posedge rstn);repeat(5) @(posedge clk);// channel 0 testchnl_write(0, 'h00C0_0000);chnl_write(0, 'h00C0_0001);chnl_write(0, 'h00C0_0002);chnl_write(0, 'h00C0_0003);chnl_write(0, 'h00C0_0004);chnl_write(0, 'h00C0_0005);chnl_write(0, 'h00C0_0006);chnl_write(0, 'h00C0_0007);chnl_write(0, 'h00C0_0008);chnl_write(0, 'h00C0_0009);// channel 1,2 test省略...

endtask chnl_write(input reg[1:0] id, input reg[31:0] data); case(id)0: begin@(posedge clk);ch0_valid <= 1;ch0_data <= data;@(posedge clk); // 下一拍idle,数据无效ch0_valid <= 0;ch0_data <= 0;end1: begin@(posedge clk);ch1_valid <= 1;ch1_data <= data;@(posedge clk);ch1_valid <= 0;ch1_data <= 0;end2: begin@(posedge clk);ch2_valid <= 1;ch2_data <= data;@(posedge clk);ch2_valid <= 0;ch2_data <= 0;enddefault: $error("channel id %0d is invalid", id);endcase

endtaskendmodule

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!