京微齐力FPGA开发工具Fuxi 2022的使用指南

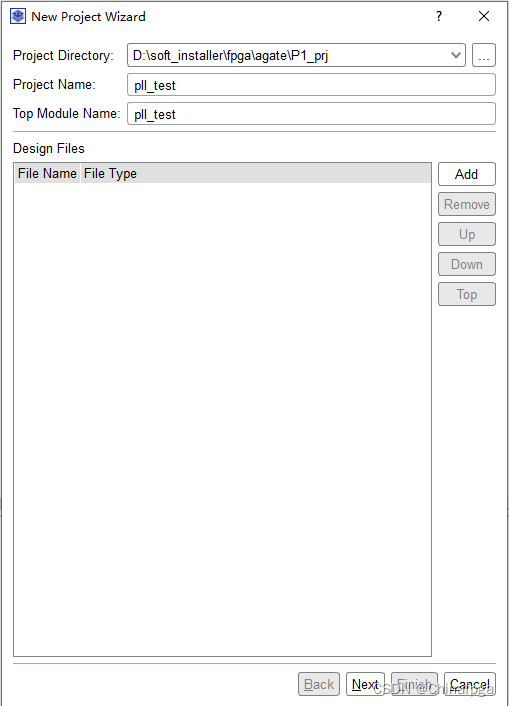

1. 创建Fuxi FPGA Project工程: Project菜单下"New Project .."命令

会在P1_prj目录下穿件一个工程目录pll_test目录,设置顶层module名字为pll_test(也可以是其他的顶层文件名,工程创建好后也可以修改)。点击"Next",进入器件选择页面

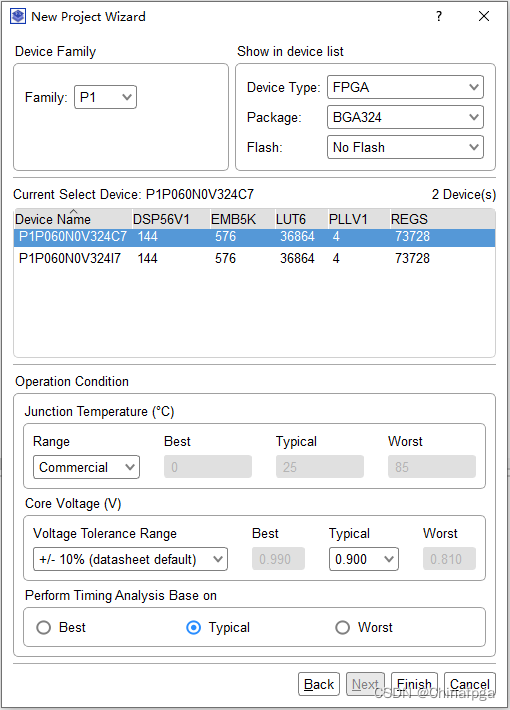

选在"P1P060N0V324C7"器件,最下方的"Perform Timing Analysis Base on"选择"Typical"时序模型。点击"Finish",完成工程设置。

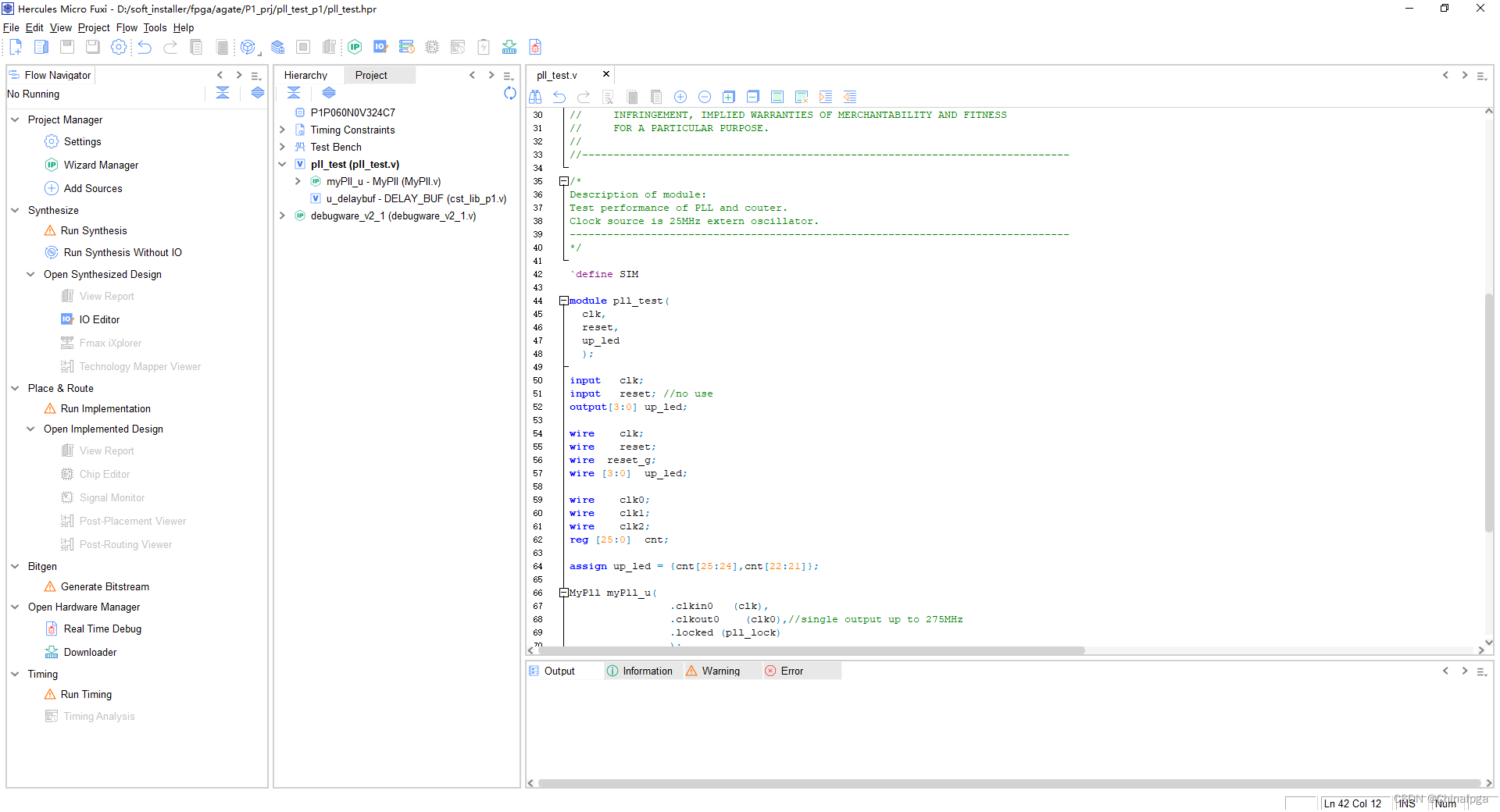

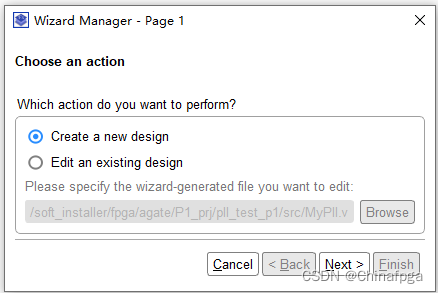

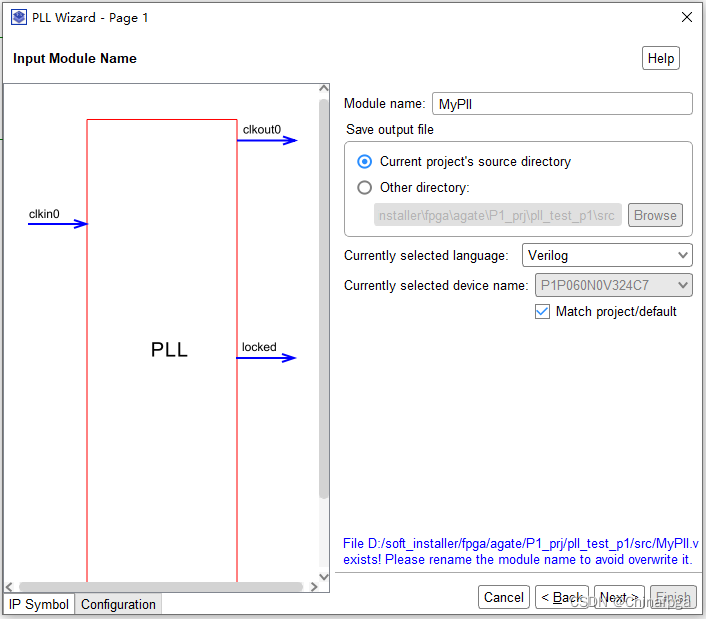

2. 生成PLL IP,左侧"Project Manager"下双击"Wizard Manager"

设置PLL IP的名字为"MyPll",点击"Next"

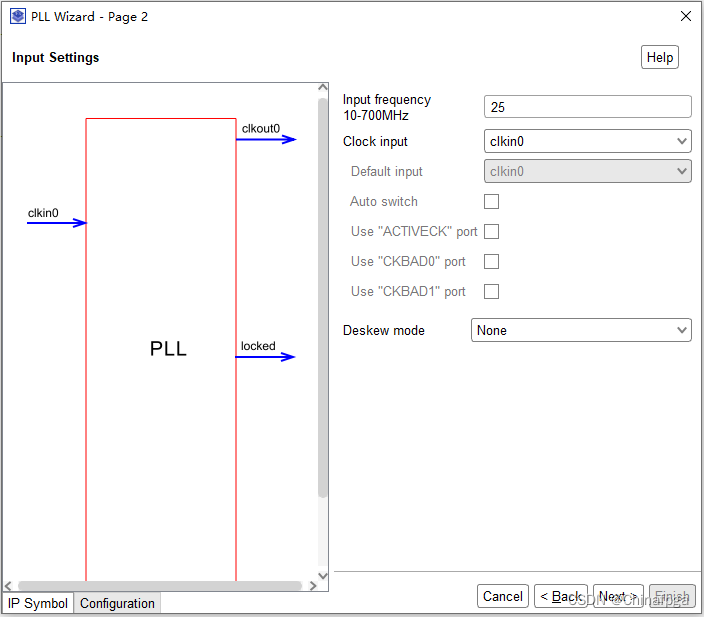

设置Input frequenccy位25Mhz(必须和板上外部的时钟频率一致),其他使用缺省设置,点击"Next"

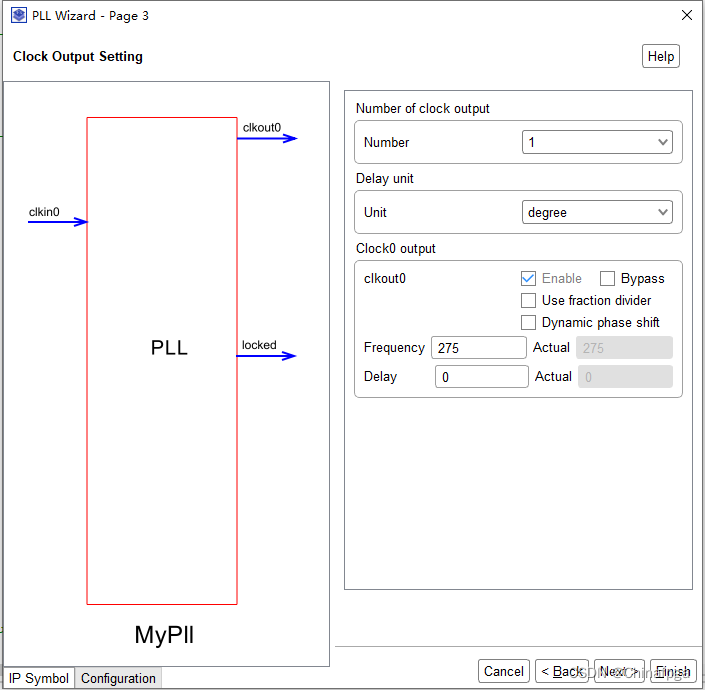

设置Clock0 output Frequency为275Mhz,点击Next

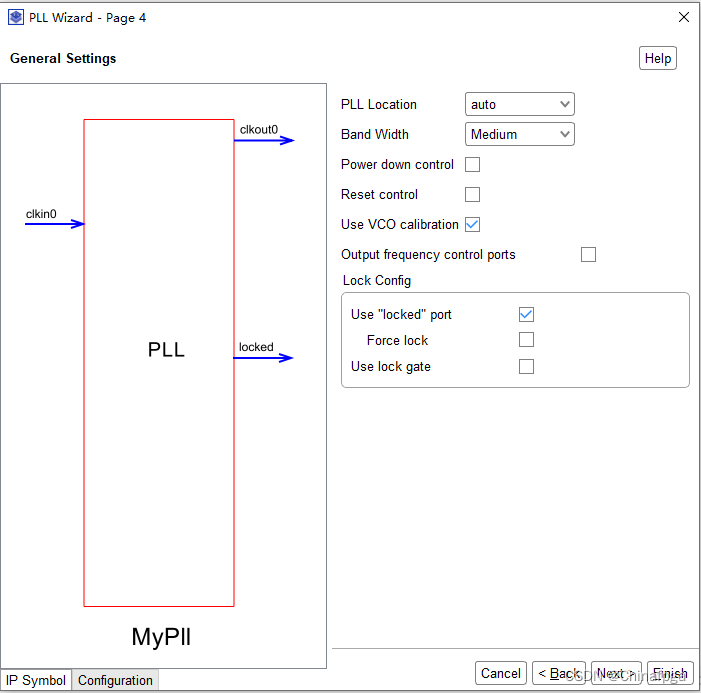

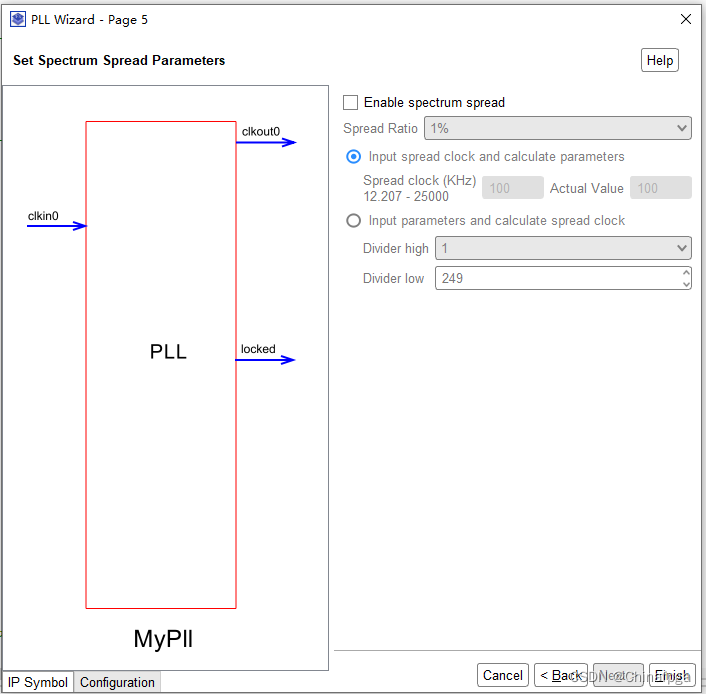

如上所示设置,点击Next

点击"Finish",完成PLL IP生成。

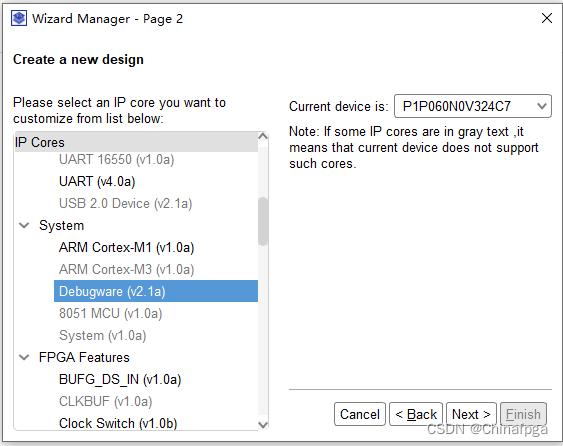

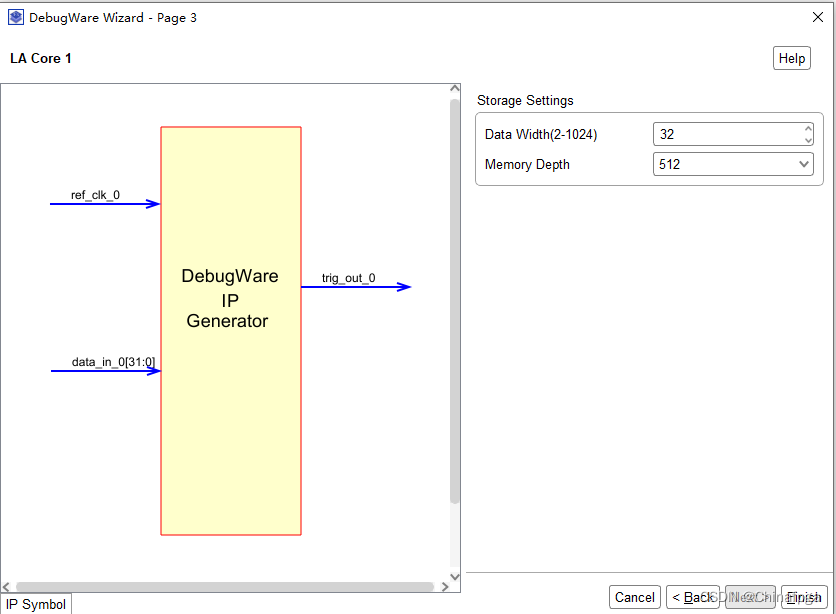

3. 创建debugware IP

4. 创建测试工程顶层文件: pll_test.v, 将文件保存在工程目录的子文件加src目录下,注意提示信息,软件会自动将新建的源代码添加到工程目录下

/*

Description of module:

Test performance of PLL and couter.

Clock source is 25MHz extern oscillator.

--------------------------------------------------------------------------------

*/`define SIMmodule pll_test(clk,reset,up_led);input clk;

input reset; //no use

output[3:0] up_led;wire clk;

wire reset;

wire reset_g;

wire [3:0] up_led;wire clk0;

wire clk1;

wire clk2;

reg [25:0] cnt;assign up_led = {cnt[25:24],cnt[22:21]};MyPll myPll_u(.clkin0 (clk),.clkout0 (clk0),//single output up to 275MHz.locked (pll_lock));always @ (posedge clk0)begincnt <= cnt + 1'b1; //cnt power on initial value is all 1end`ifndef SIMdebugware_v2_1 debugware_v2_1_u(.data_in_0( cnt[25:0] ),.ref_clk_0( clk0 )

);`endif

endmodule

5. RTL 仿真

创建pll_test_tb文件

`timescale 1 ns/100psmodule pll_test_tb;reg clk;

reg reset;

wire [1:0] led;

wire led1;

wire [1:0] up_led;

wire pll_lock;pll_test u_pll_test(.clk(clk),.reset(reset),

// .led(led),

// .led1(led1),.up_led(up_led)//,

// .pll_lock(pll_lock));initialbeginclk = 1'b0;reset = 1'b0;

#100 reset = 1'b1;end///

//

// Clock generation

//always #20 clk = ~clk;endmodule

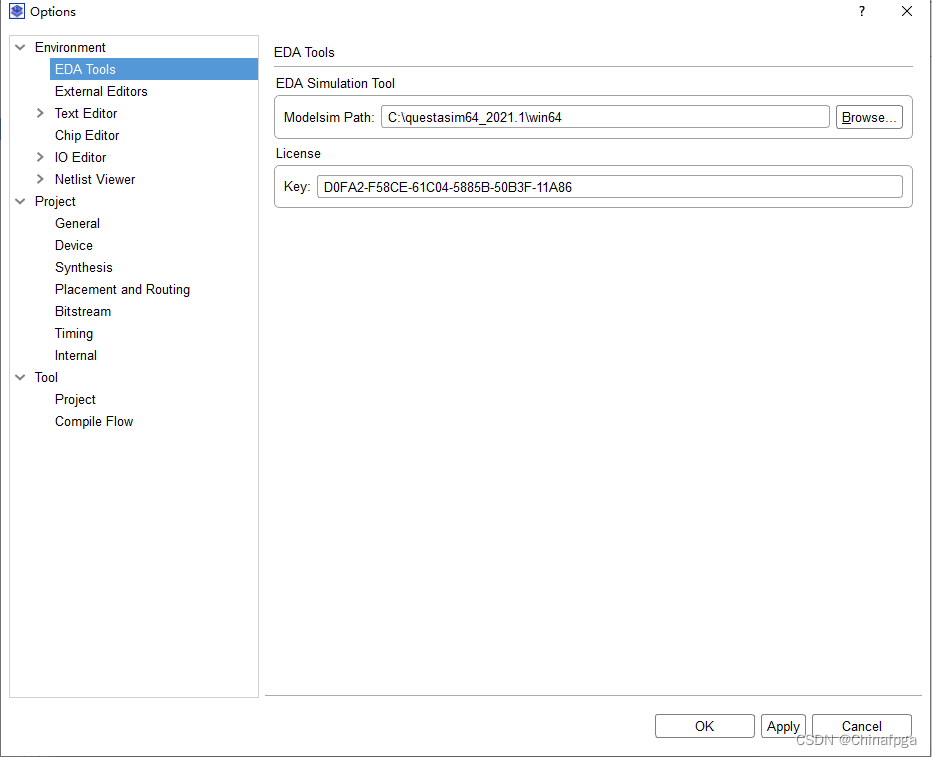

设置Questasim/Modelsim的exe执行目录,一般在仿真软件安装目录的win64子目录下,如果是Questasim工具,需要手工复制Questasim.exe为Modelsim.exe,因为Fuxi工具只会自动找"Modelsim.exe"

仿真文件的工程设置

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!