10. 软硬件I2C

江科大stm32 P10. 软硬件I2C

USART串口通信的缺点

- 只能单设备通信

- 在一发一收模式下总有一根线是空闲的,浪费资源

- 异步时序对时间要求严格,不能中断暂停,发送方停了,但接收方仍会按波特率接收(会导致出错),这导致异步时序非常依赖硬件电路,很难用软件模拟

改进

改成同步时序,另加一条时钟线指导双方读写,这样通讯对于时间的要求就不高了,也可以随时暂停中断,可以极大降低对硬件电路的依赖

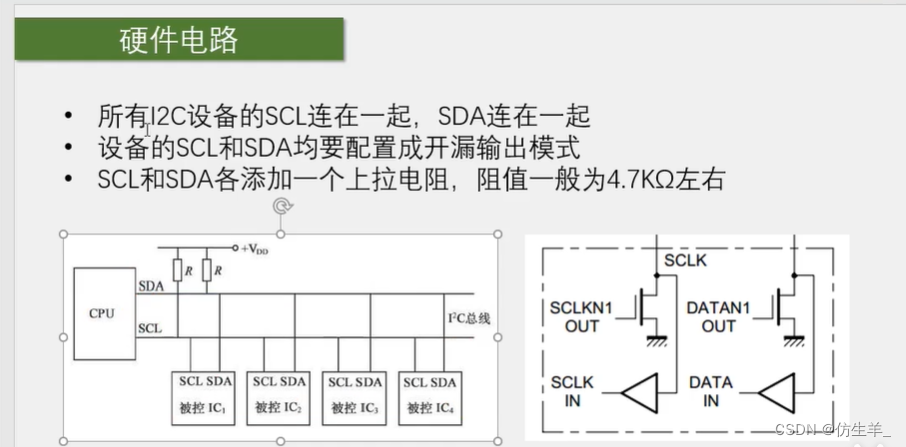

IIC硬件电路

一主多从模式下主机对SCL线有完全控制权,在空闲状态下主机可主动发起对SDA的控制。在主机发送读指令后或者从机应答时主机才会转交SDA控制权给从机。从机在任何时刻都不能控制SCL只能读取

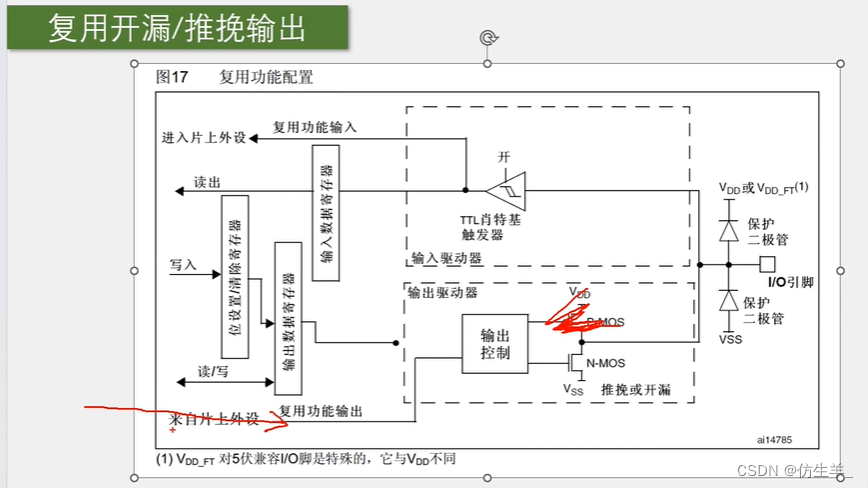

如果时序没调好导致主机和从机同时处于输出状态,又刚好输出高电平一个输出低电平,就会导致短路,IIC为了避免总线没协调好导致短路的问题,禁止所有设备输出强上拉高电平,采用弱上拉电阻加开漏输出的电路结构。这解决了几个个问题(开漏输出,高电平时是引脚浮空状态)

1.完全杜绝电源短路现象,保证电路安全

2.避免了引脚模式的频繁切换,开漏加弱上拉,同时兼据输入和输出的功能

3.线与功能,只要任意一个或多个设备输出低电平,则总线就处于低电平,只有所有的设备都输出高电平,总线才处于高电平,IIC可以利用这个特性,执行多主机模式下的时钟同步和总线仲裁。所以SCL也要用开漏加弱上拉。

I2C基本时序单元

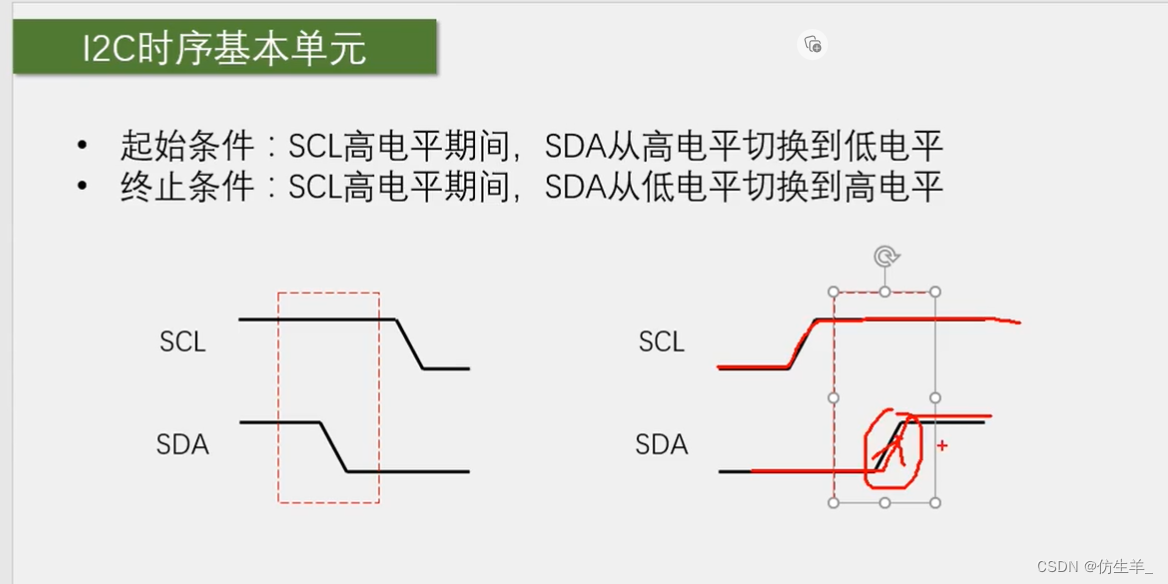

起始和终止时序

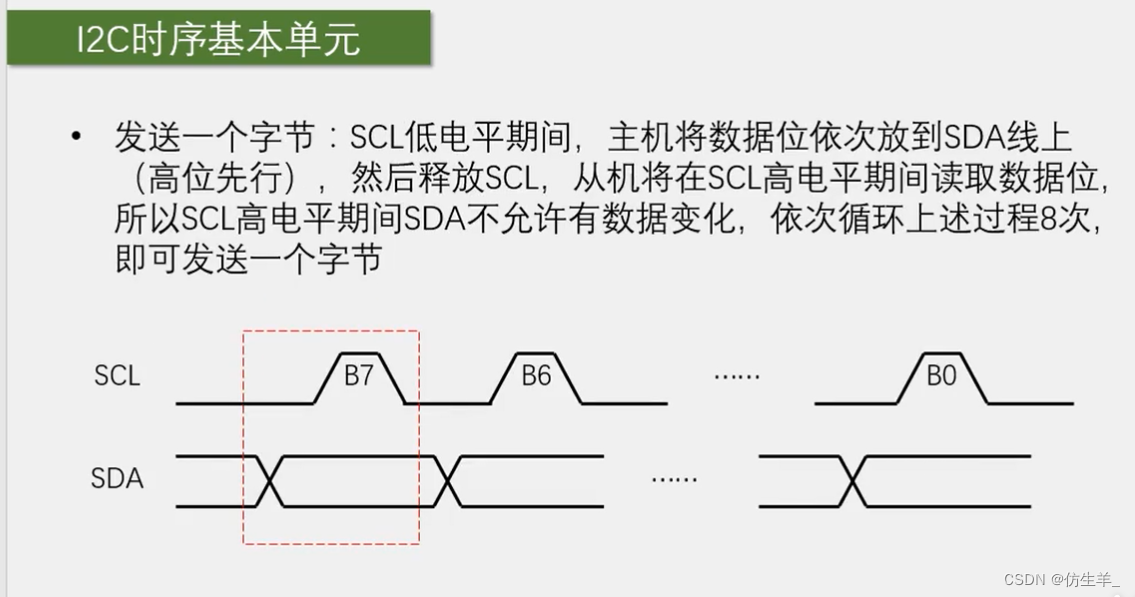

发送时序

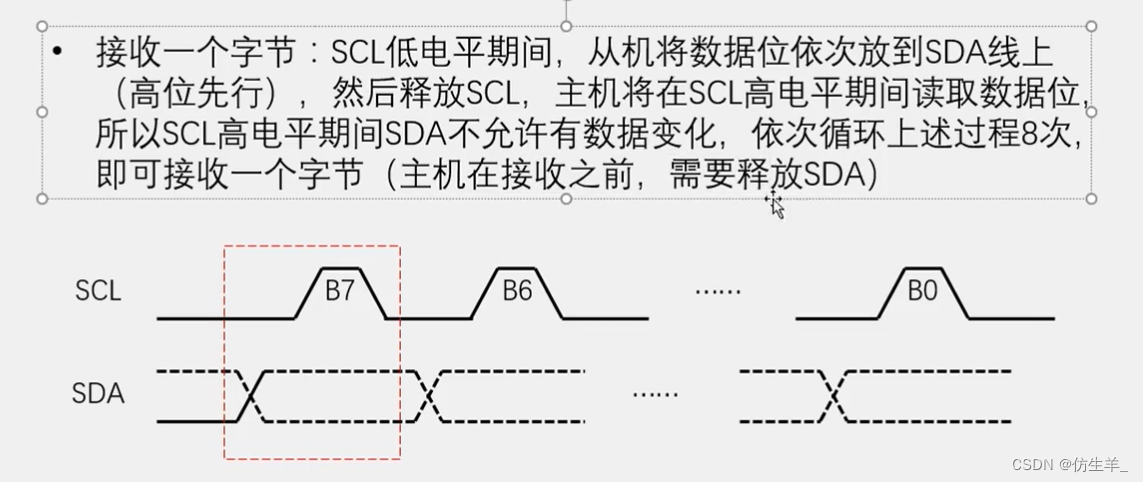

接收时序

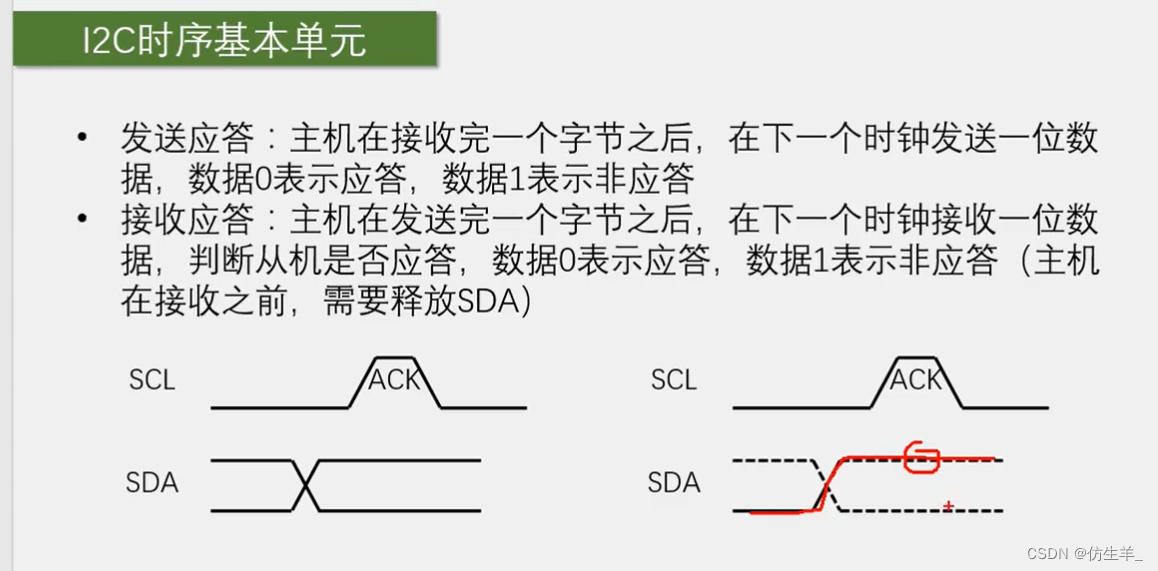

应答时序

寻址方式

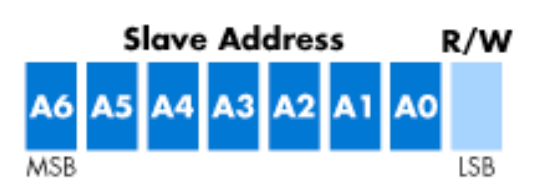

7位寻址

七位地址,也就是最多可以挂载2^7个从设备,去掉000号广播地址,理论上可以挂载127个从设备。

但是IIC协议规定总线电容不能超过400pf,所以实际只能挂载不超过8个从设备。

具体可看这篇文章 IIC可挂载多少从设备

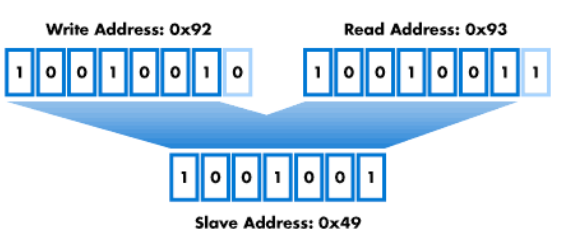

8位寻址

其实是包含了读写位,前7位才是从机地址

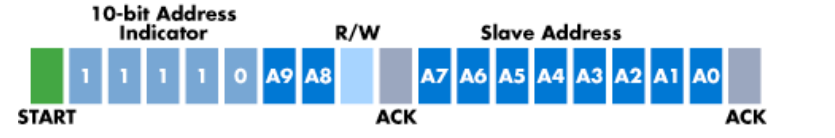

10位寻址

5位固定前缀11110,然后发地址高两位,再发读写位,之后等从机应答后再发剩余八位

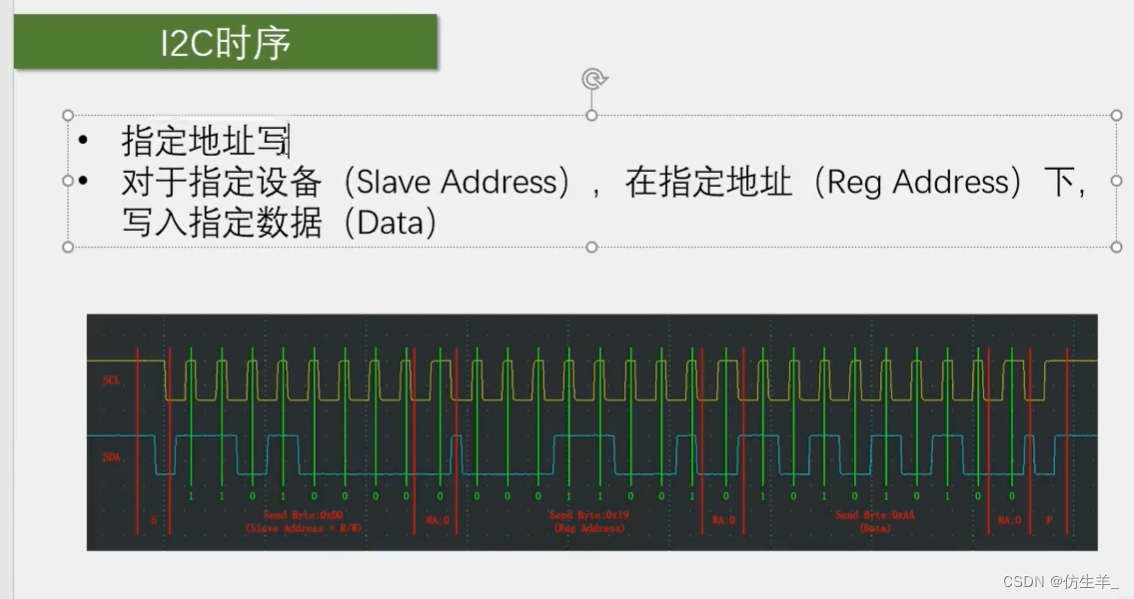

I2C时序

指定地址写

- SCL高电平期间拉低SDA,产生起始条件

- 之后紧跟发送一个字节的时序(从机地址7位+读写位1位)

- SCL低电平期间主机改变SDA,SCL高电平期间从机读取SDA

- 读写位为0表示,之后的时序主机要进行写操作,1表示之后的时序主机要进行读出操作

- 之后紧跟着的就是接收从机的应答位,主机要释放SDA

- 从机应答后,在SCL低电平交出控制权,因为从机要尽快交换数据,所以SDA电平拉高的上升沿和SCL的下降沿几乎是同时发生的

- 第二个字节可以是寄存器地址或者是指令控制字等,MPU6050第二个字节是寄存器地址

- 最后一个字节就是想要写入到寄存器的内容

- 收到应答后若不想继续写,就可以产生停止条件,主机先拉低SDA为之后的上升沿做准备。还想继续写的话,只需要重复最后一个字节的时序就可以了,每写一次,地址指针加一

- 对于制定从机地址为1101000的设备,在指定地址0x19的寄存器写入0xAA这个数据

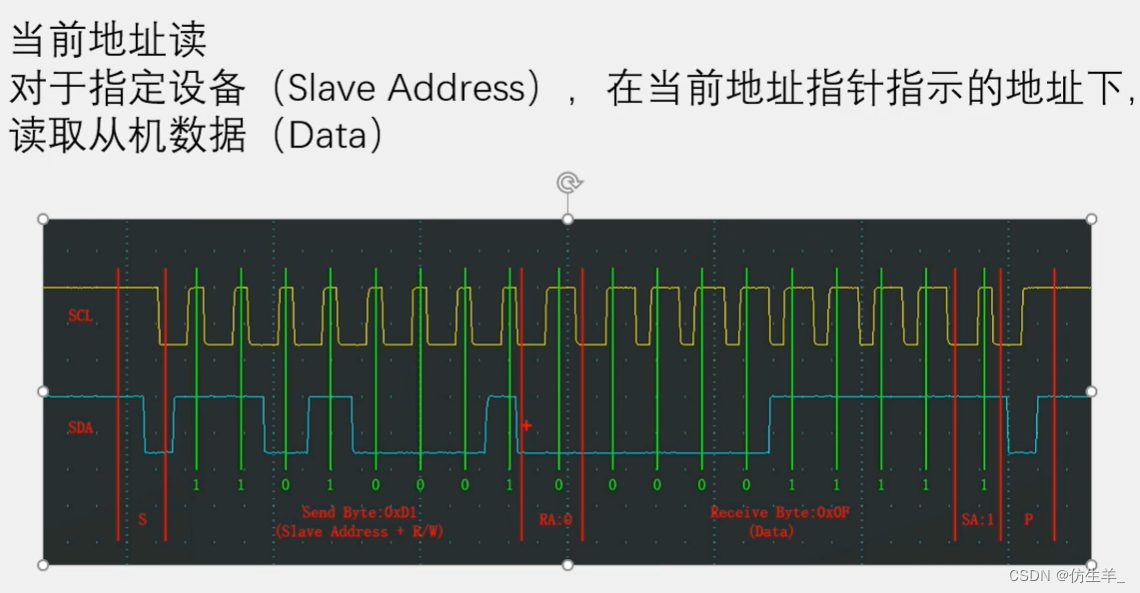

当前地址读

- 产生起始条件

- 发送设备寻址,读写位置1,读

- 从机应答

- 数据传输方向反转,主机调用接收一个字节的时序,进行接收,从机得到允许,在SCL低电平期间写入SDA,主机在SCL高电平期间读SDA

- 从机中所有寄存器被分配到一个线性区域中,一个指针变量指向这个区域,上电后一半默认指向0号寄存器的地址,每写入和读出一个字节后,指针自增一次

- 没有指定地址时,读数据会返回当前指针指向地址的数据

由于不能指定地址,这个时序很少用

指定地址读

指定地址写的时序去掉最后一字节写数据的部分,加在当前地址读时序的前面,就构成了指定地址读的时序

- 起始条件

- 发送设备寻址 读写位置0,写

- 从机应答

- 发送指定地址字节

- 从机应答。

- 之后就是读的时序了,也可以在从机应答后加一个停止位,这样就是一个完整的时序。地址已经写入地址指针,不会因为停止条件而消失。但是IIC协议规定的时序是没有这个停止位的。

- 产生起始条件Sr(Start Repeat)重复起始条件

- 发送设备寻址 读写位置1,读

- 从机应答

- 主机接收一个字节

- 主机想继续读的话,需要回复应答。主机回复非应答,从机释放总线,交还SDA控制权

从机控制SDA的权利开始于读写位 置1,结束于主机非应答

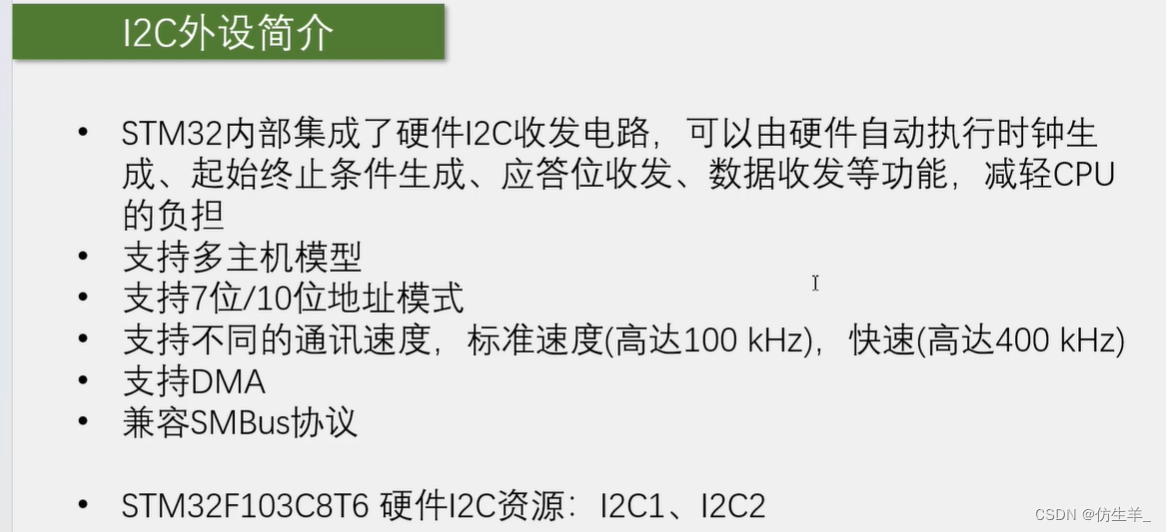

I2C硬件外设

- 硬件I2C优势:执行效率高、节省软件资源、功能强大,可以实现完整的多主机通信模型、时序波形规整、通信速率快等等。如果对性能要求比较高可以考虑使用硬件I2C

- 多主机:stm32的多主机是可变多主机,stm32不进行通信时是从机

- 速度:作为一个同步时钟,速率并不严格,不超过最大值就行,一般不会关注频率的具体值

- DMA:多字节传输时可以提高传输效率

原理图分析

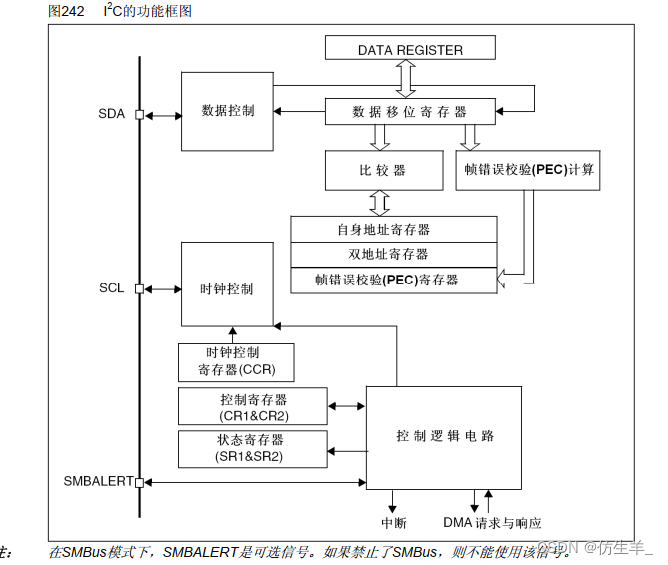

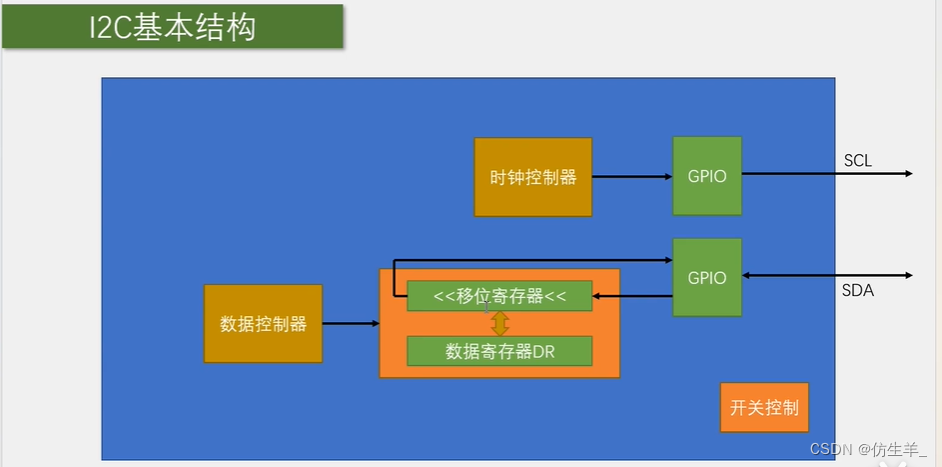

移位寄存器与数据寄存器:

- 发送:当移位寄存器没有数据移位时,数据寄存器的值就会转到移位寄存器中,在移位的过程中就可以把下一个数据放到移位寄存器了。当数据寄存器转到移位寄存器时就会值状态寄存器TXE的值为1,表示发送寄存器为空

- 接收:数据从SDA引脚进入沿着图中箭头标注的线一位一位的进入移位寄存器,当一个字节数据收齐后,就从移位寄存器转到数据寄存器,同时值标志位RXNE,表示接受寄存器非空

数据控制:内有I2C控制寄存器,可以发送起始条件、终止条件、应答位等,

比较器和地址寄存器:从机模式时使用。自定从机地址可以写到自身地址寄存器。收到寻址后比较器判断是否和自身地址寄存器相同

校验:CRC校验

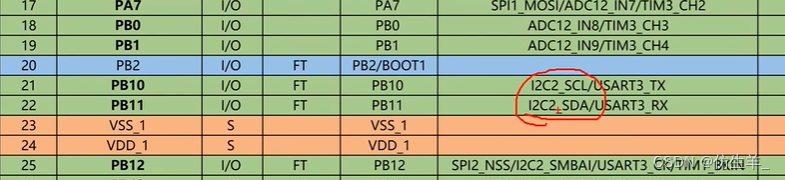

GPIO引脚复用情况 如下:

在标准速度下(不超过100KHz)SCL 时空占空比DutyCycle默认为低电平比高电平1 : 1。

在图中可以看出SCL和SDA下降沿十分平滑,但是上升沿有缓冲现象,这是因为,产生下降沿时引脚接地产生强下拉,而上升沿是上拉电阻弱上拉

SCL低电平期间变化数据,高电平读取数据 在快速模式下(高于100KHz)低电平时间应该长一些,因为SDA反转上升沿时间比较慢,所以SCL低电平时间要多分配一些,使得SDA有时间变化数据。也就是写入时间大于读取时间

I2C基本结构图

多主机模式下,SCL也是有输入的,这个图是一主多从模式的

高位先行,向左移位

GPIO要配置为复用开漏输出,复用就是GPIO的状态由片上外设控制

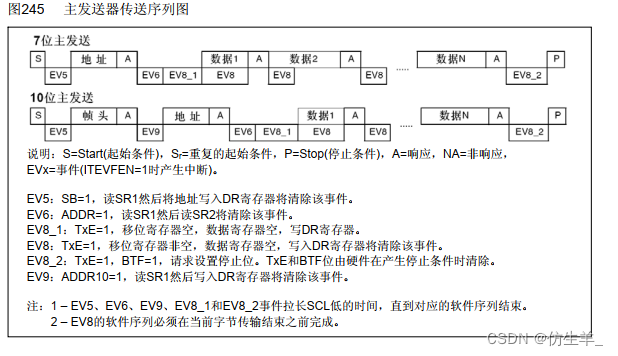

主机发送时序图

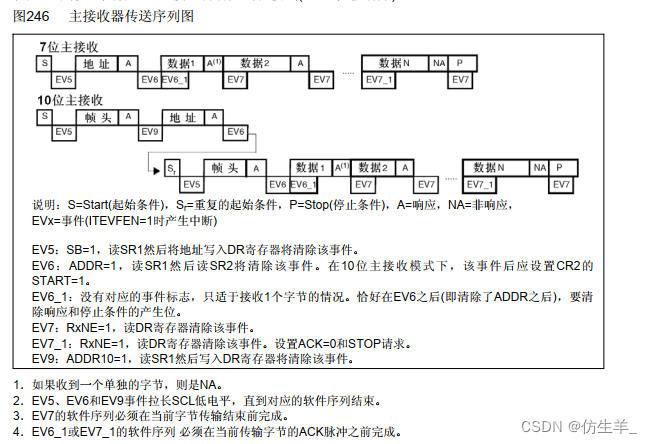

主机接收时序图

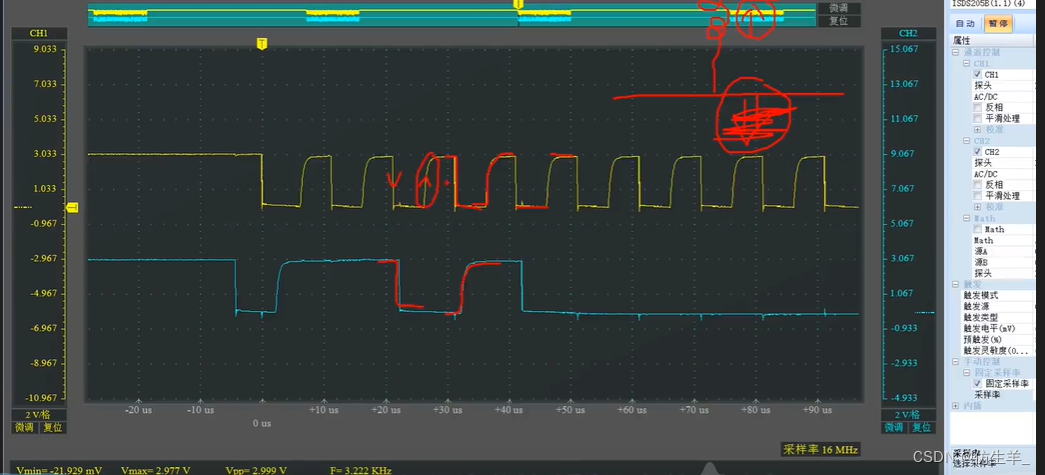

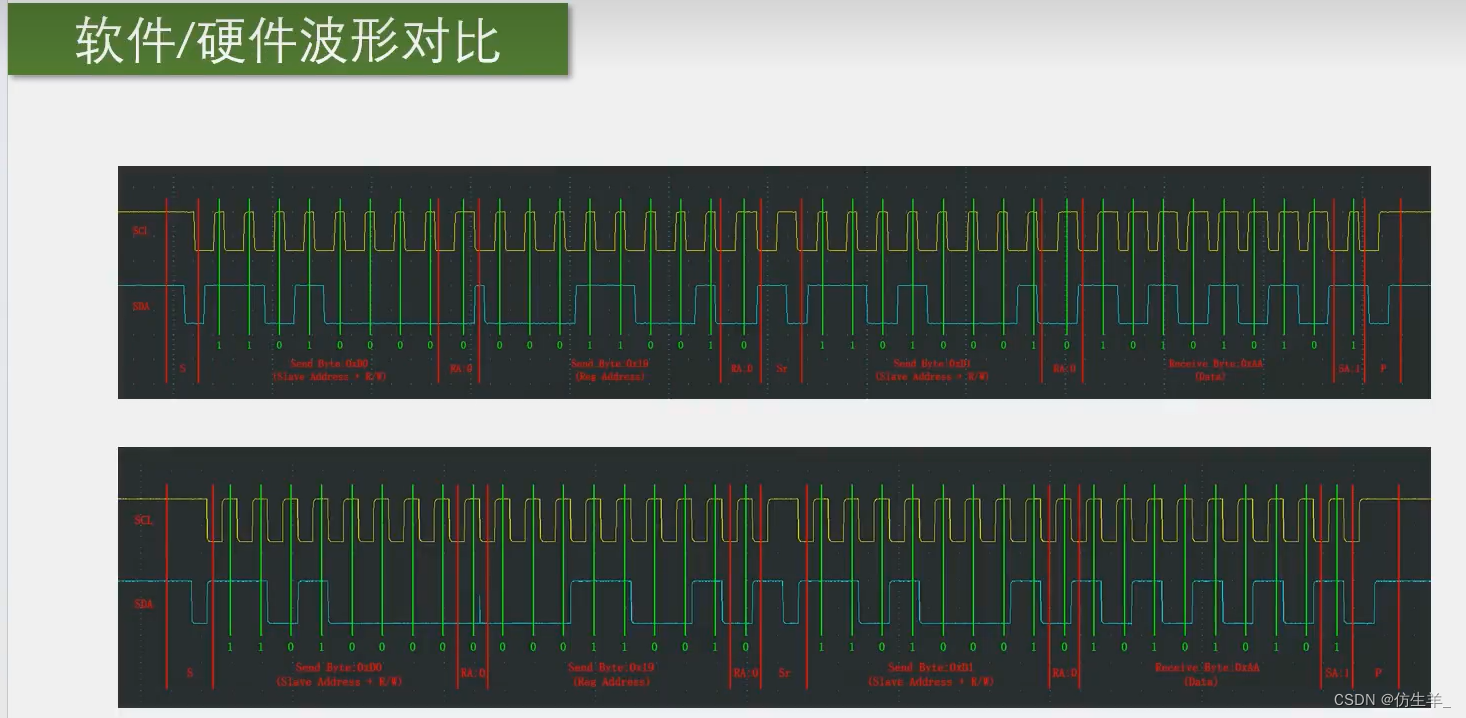

软硬件I2C波形对比

硬件I2C的波形更加规整,每个时钟的周期、占空比都非常一致

而软件I2C由于操作引脚之后加了延时,有时候多,有时候少,所以不是很规整。但由于I2C是同步时序,没有太大影响

SCL低电平写,高电平读,整个电平期间都可以读写,但是一般要求尽早读写。软件I2C的读写都有些延时,而硬件I2C都是紧贴着下降沿和上升沿读写

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!